VL4 移位运算与乘法

这里有一个细节

一个数A做乘法,每乘一次2,就等于这个数A的二进制左移一位

比如,7的二进制是0111,那么72的操作就是0111左移一位变成1110,就是十进制的14

而这里的乘以3可以根据分配律来看

假设一个数A乘以3可以写成A3=A*(2+1),也就是左移一次,然后再加上这个数

那么同理A4是左移两位

那么乘以7也是同理,A7=A*(2+4+1),就是左移一位,左移两位,再加原先这个数

那么机智的你一定发现,乘以8就是把这个数的二进制左移三位

verilog代码

`timescale 1ns / 1ps

module vl4(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [1:0]state;

reg [7:0]d1;

always@(posedge clk or negedge rst) begin

if(~rst) begin

input_grant <= 0;

out <= 10'b0;

state <= 0;

d1 <=7'b0;

end

else begin

if (input_grant == 1)

input_grant <= 0;

else

input_grant <= input_grant;

case(state)

0://d乘1,用d1将d的值锁存进去

begin

out <= d;

d1 <= d;

input_grant <= 1;

state <= 1;

end

1://d乘3

begin

out <= d1 + {d1,1'b0};

state <= 2;

end

2://d乘7

begin

out <= d1 + {d1,1'b0} + {d1,2'b00};

state <= 3;

end

3://d乘8

begin

out <= {d1,3'b000};

state <= 0;

end

endcase

end

end

endmodule

TB

`timescale 1ns / 1ps

module vl4_tb();

reg [7:0]d ;

reg clk;

reg rst;

wire input_grant;

wire [10:0]out;

vl4 vl4_tb_1(

.d(d) ,

.clk(clk),

.rst(rst),

.input_grant(input_grant),

.out(out)

);

real CYCLE_200MHz = 10 ;

always begin

clk = 0 ; #(CYCLE_200MHz/2) ;

clk = 1 ; #(CYCLE_200MHz/2) ;

end

initial begin

rst = 0; d = 0;

#10 rst = 1;d = 143;

#40; d = 7;#40;

$stop;

end

endmodule

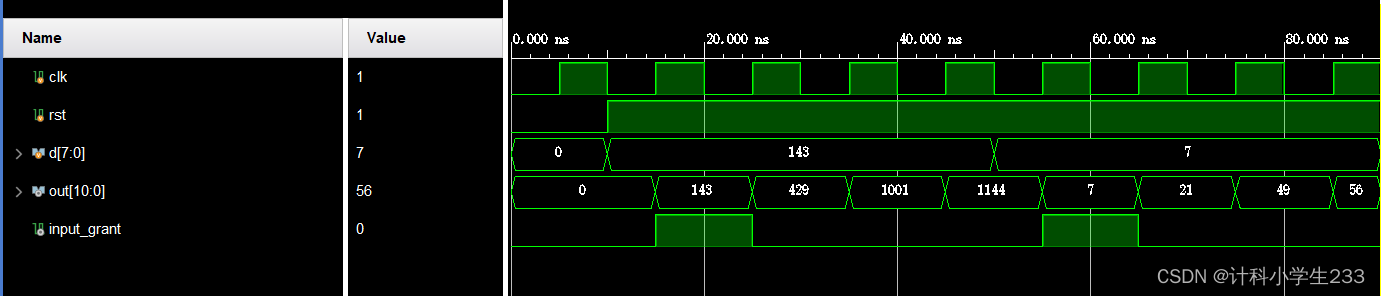

波形图

333

333

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?