开发板:Zynq7030数据采集板

PC平台:Ubuntu-18.04 + MobaXterm

开发环境:Xilinx Vivado + SDK -18.3

交叉编译工具:arm-linux-gnueabihf-

学习目标:生成 fsbl.elf 文件

一、Zynq-7000系列启动顺序

Zynq-7000是一个可扩展处理平台,具有ARM核心和FPGA可编程单元。整个启动过程包括了PS端ARM的配置,也有PL端FPGA的配置。

Zynq-7000支持从多种设备启动,包括:JTAG,NAND,parallel NOR,Serial NOR (Quad-SPI),以及SD卡,通过几个特殊的MIO引脚的状态来确定启动设备,如下图所示。 目前使用的Zynq7030数据采集板可支持JTAG、QSPI和SD卡启动,学习中选用从SD卡启动。

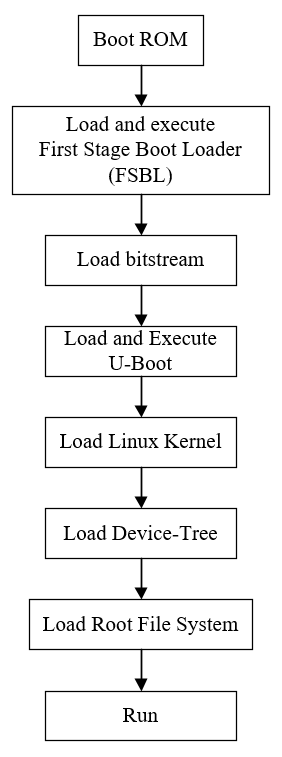

Zynq-7000的启动过程如下图所示:

熟悉Linux的都知道系统启动离不开BootLoader,u-boot便是一种常用的BootLoader程序。在Zynq中,系统启动需要有一个文件叫 BOOT.bin ,组成文件如下表所示:

| 包含文件 | 作用 |

|---|---|

| fsbl.elf | 第一阶段启动代码,用来完成全局初始化和硬件配置 |

| 硬件比特流.bit文件 | 用来配置PL端(可选!若不添加此项,可启动后由软件配置) |

| u-boot.elf | 用来初始化ARM端,引导Linux操作系统 |

一般在生成fsbl.elf文件时候,已经在Vivado里面生成了硬件比特流.bit文件。所以在制作BOOT.bin文件时,只需要再编译生成一个u-boot.elf文件即可。

二、FSBL制作

本篇先开始制作fsbl.elf和硬件比特流.bit文件。

fsbl生成

首先仍然是创建一个Vivado工程,并命名为fsbl。

然后按照之前的文章配置好工程,并完成创建。

进入到界面后,点击 Create Block Design 创建一个原理框图设计,并命名为fsbl。

接着添加 Zynq 7 Processing System 的IP核,双击进入到配置界面。

选择 PS-PL Configuration ,去掉图中 FCLK_RESET0_N 选项。

选择 Peripheral I/O Pins 进行配置。这里需要根据具体的原理图设计来进行配置,以Zynq7030数据采集板为例:有两颗QSPI Nor Flash,两个Ethernet(这里使用其中一个。注意:MDIO的选择要使用MIO,这里没有用到EMIO),一个SD卡接口,一路SPI 1,一路I2C 0和一路UART1。最后再为LED添加一个EMIO口。

每种接口对应的MIO要仔细核对,不能有错。配置如下图所示:

I/O口配置好后,选择 MIO Configuration 对每个接口的IO口进行设置,最终设置如下图所示:

然后选择 Clock Configuration ,将SDIO的时钟频率改为50MHz,其他可保持不变。

选择 DDR Configuration ,选择好DDR3的型号即可。

最终可得到如图所示的原理框图设计。

然后就可以生成顶层文件,关闭本窗口。

接着还需要写管脚的约束文件,这里仍然命名为fsbl,约束文件内容如下:

set_property PACKAGE_PIN N8 [get_ports {SYS_LED_tri_io[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {SYS_LED_tri_io[0]}]

上述步骤都完成,就可以生成Bitstream,然后导出硬件配置,打开SDK了。

这里其实就已经生成好硬件比特流文件.bit了,文件存放路径如下图所示: fsbl_wrapper.bit 。

也可以打开终端,到工程相应目录下就可看见 fsbl_wrapper.bit 。

claude1009@ubuntu:~/xc7030/fsbl/fsbl.runs/impl_1$ ls

fsbl_wrapper.bit fsbl_wrapper_drc_routed.rpx fsbl_wrapper_routed.dcp gen_run.xml runme.log

fsbl_wrapper_bus_skew_routed.pb fsbl_wrapper.hwdef fsbl_wrapper_route_status.pb htr.txt runme.sh

fsbl_wrapper_bus_skew_routed.rpt fsbl_wrapper_io_placed.rpt fsbl_wrapper_route_status.rpt init_design.pb usage_statistics_webtalk.html

fsbl_wrapper_bus_skew_routed.rpx fsbl_wrapper_methodology_drc_routed.pb fsbl_wrapper.sysdef ISEWrap.js usage_statistics_webtalk.xml

fsbl_wrapper_clock_utilization_routed.rpt fsbl_wrapper_methodology_drc_routed.rpt fsbl_wrapper.tcl ISEWrap.sh vivado.jou

fsbl_wrapper_control_sets_placed.rpt fsbl_wrapper_methodology_drc_routed.rpx fsbl_wrapper_timing_summary_routed.pb opt_design.pb vivado.pb

fsbl_wrapper_drc_opted.pb fsbl_wrapper_opt.dcp fsbl_wrapper_timing_summary_routed.rpt place_design.pb write_bitstream.pb

fsbl_wrapper_drc_opted.rpt fsbl_wrapper_placed.dcp fsbl_wrapper_timing_summary_routed.rpx project.wdf

fsbl_wrapper_drc_opted.rpx fsbl_wrapper_power_routed.rpt fsbl_wrapper_utilization_placed.pb route_design.pb

fsbl_wrapper_drc_routed.pb fsbl_wrapper_power_routed.rpx fsbl_wrapper_utilization_placed.rpt rundef.js

fsbl_wrapper_drc_routed.rpt fsbl_wrapper_power_summary_routed.pb fsbl_wrapper.vdi runme.bat

进入到SDK后,新建一个APP工程,命名为fsbl。

这里选择Xilinx SDK自带的Zynq FSBL工程模块就可以。

创建完后,找到并打开fsbl_debug.h,然后添加一行代码如下:

#define FSBL_DEBUG_INFO

保存修改后,自动编译。在下方的窗口可以看到如下图所示的编译结果。

fsbl.elf 就自动帮我们生成了,存放路径如下图所示:

同样,也可以打开终端,到工程相应目录下就可看见 fsbl.elf 。

claude1009@ubuntu:~/xc7030/fsbl/fsbl.sdk/fsbl/Debug$ ls

fsbl.elf fsbl.elf.size makefile objects.mk sources.mk src Xilinx.spec

fsbl串口输出信息

这部分内容仅仅做展示用,实际操作中并不会这样做。

用上面得到的 fsbl.elf 和 fsbl_wrapper.bit 两个文件来生成BOOT.bin文件。在SDK界面,点击 Xilinx ,出现菜单后再点击 Create Boot Image ,如下图所示:

然后选择好文件输出路径,我的路径如图所示。接着点击 Add ,依次添加刚才生成的 fsbl.elf 和 fsbl_wrapper.bit ,添加文件操作如下图所示。最后点击 Create Image 即可。

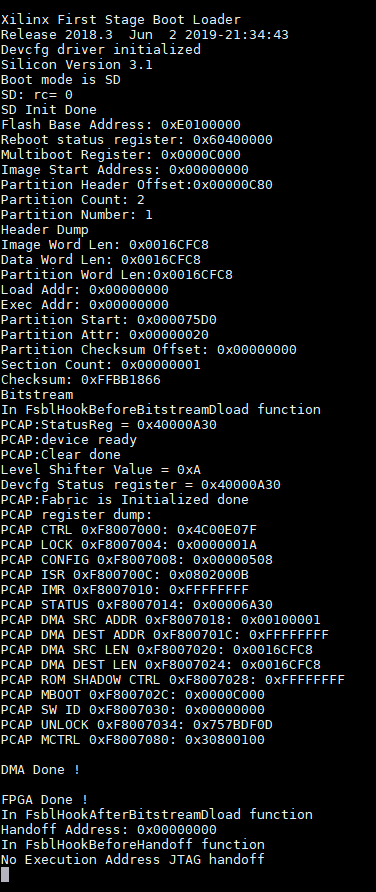

此时BOOT.bin就已经在刚才设置的输出路径里生成了。可以将此BOOT.bin文件复制到SD卡里,然后插入到板子的SD卡槽中,连上USB线和电源线,在PC端打开MobaXterm工具,即可看到如下的信息打印:

1191

1191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?