(3)数据交易类型

通过组合信号可以得到四种基本的传输类型。

①空闲:(没有任何传输)

HSTRANS[1:0] == 2’b00;

②取指:(处理器希望执行取指操作,处理器一次性从存储器中取出32位指令信号)

HSTRANS[1:0] == 2’b10;

HPROT[0] == 1’b0;

HSIZE[1:0] == 2’b00;

HWRITE == 1’b0;

③字节:(处理器希望执行8位数据访问操作,该操作由指令LDRB、LDRBS、STRB等产生)

HSTRANS[1:0] == 2’b10;

HPROT[0] == 1’b1;

HSIZE[1:0] == 2’b00;

//HWRITE信号为高电平对应STRB指令,HWRITE信号为低电平对应LDRB、LDRBS等指令。

④半字:(处理器希望执行16位数据访问操作,该操作由指令LDRH、LDRHS、STRH等产生)

HSTRANS[1:0] == 2’b10;

HPROT[0] == 1’b1;

HSIZE[1:0] == 2’b01;

//HWRITE信号为高电平对应STRH指令,HWRITE信号为低电平对应LDRH、LDRHS等指令。

⑤字节:(处理器希望执行32位数据访问操作,该操作由指令LDR、LDM、POP、STR、STM、PUSH等,或者异常入口的一部分,或者返回所产生)

HSTRANS[1:0] == 2’b10;

HPROT[0] == 1’b1;

HSIZE[1:0] == 2’b10;

//HWRITE信号为高电平对应STR、STM指令,HWRITE信号为低电平对应LDR、LDM等指令。

(4)读/写数据字节通道

//详见《手撕SoC》P65

(5)处理器存储器映射属性

Cortex-M0的存储器属性已经由ARMv6-M架构决定了,所以存储器地址空间的使用规则已经固定了。

//详见《手撕SoC》P65

(6)地址译码器

多路复用器为多对一设备,由多个从设备指向一个主设备。

地址译码器是一对多设备,由一个主设备指向多个从设备。其输入为地址信号,输出为选择信号。它包含两个功能:

①根据主设备在地址总线上提供的访问地址空间信息,生成选择一个从设备的选择信号HSEL_x,通向各个从设备。

②选择信号也连接到从设备多路选择器,用于在多个从设备当中选择对应的从设备返回信息。

(7)多路选择器实现总线互联

AHB-Lite使用多路选择器来实现从设备输出的多路数据信号之间的互联。

每个从设备都有一系列响应信号:HRDATA_x、HRESP_x、HREADYOUT_x。这些信号在输入多路复用选择器之后,通过从地址译码器输入的选择信号来控制输出其中一路给主设备。

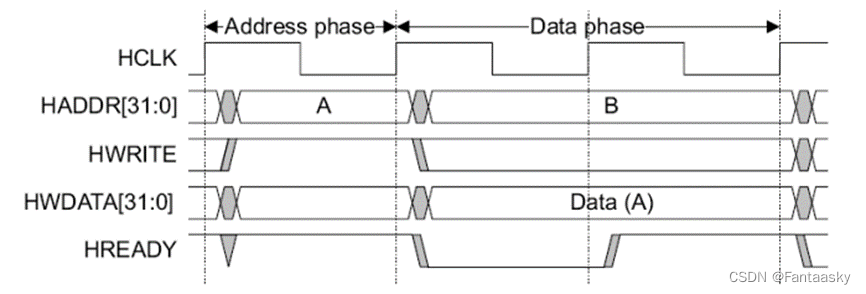

(8)AHB-Lite总线时序

不论是写还是读,不论是否有等待状态,传输都分为两个阶段:

①地址访问阶段

地址阶段只持续一个HCLK,表示把之后传输的数据对应的地址信号HADDR和控制信号(HWRITE等)给提前一个HCLK给出。

②数据访问阶段

持续几个HCLK周期,其持续时长和HREADY信号有关系(HREADY信号通过监控先前传输是否完成来判断是否进入等待状态)。

//在AHB-Lite中,引入了流水线传输的机制,就是说现在在进行当前的数据访问阶段的同时,也可以执行下一次传输的地址访问阶段。

//控制读传输和写传输的是HWRITE信号,当它是高电平时说明是写传输,低电平时是读传输。

1)无等待基本读传输

2)无等待基本写传输

3)有等待读传输

//等到HREADY回归高电平之后HRDATA[31:0]才开始读取数据

4)有等待写传输

//等到HREADY回归高电平之后HWDATA[31:0]上的数据才开始写入

(9)实现中需要注意的问题

因为AHB-Lite中使用了流水线的思想,所以必须对某些信号做出一些延迟,以达成传输的顺利:

①由地址译码器到多路选择器的选择信号HSEL,需要一个HCLK的延迟。

②在多路选择器输出的HREADY信号反馈到从设备的HREADYIN之前,需要延迟一个HCLK周期。

2582

2582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?