1.异步复位和同步复位

异步复位中复位信号是老大,不管clk如何变化,只要检测到复位信号的上升沿,就要把输出置为复位值。

同步复位不一样,只有clk一个老大,在clk的上升沿到达的时候,我才会去看小弟rst的值,如果rst有效,才会把输出置为复位值。

同步复位的问题:如果复位有效持续时间小于时钟一个周期时间,那么复位信号会在采样的时候被抹杀掉,无法采到复位信号,导致无法复位。

2.异步复位释放会导致的问题:亚稳态

异步复位信号的释放明确了两个概念:恢复时间(Recovery Time)和去除时间(remove time),这个概念时针对异步信号释放给出的,需要满足的要求是:释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放。换句话说,为了时钟采集异步复位信号时,需要满足建立时间Tsu和保持时间Th的概念。

在图中,rst_n位低电平有效。亚稳态出现的原因是:复位信号不知什么到来,若在图中的时候到来,由于线延迟,复位引脚的信号到达各个触发器异步复位引脚的时刻不确定,若复位信号到达触发器的引脚的信号正在进行由高电平转换为低电平,而这个电平变化正好在采集时钟沿的保持时间或者建立时间窗口内,这会导致不满足建立时间或保持时间要求,就会出现亚稳态现象。

这个问题比较严重,因为由于线延迟不确定,从复位输入信号引脚到各个触发器异步复位引脚的时延不同,这样会导致有些触发器正常复位,有些触发器由于线延时过长,还没有进行复位,有的触发器采到亚稳态,这就会导致整个系统混乱,直接完蛋。

但是好消息是99.9%的情况下,这种问题不会发生。

3.Xilinx推荐复位方式:同步复位

为了避免0.1%的概率,Xilinx提出了同步复位方案,这种方案沿用了异步复位的优势:复位不用管clk,但也保证了不会出现异步复位释放出现亚稳态的问题。

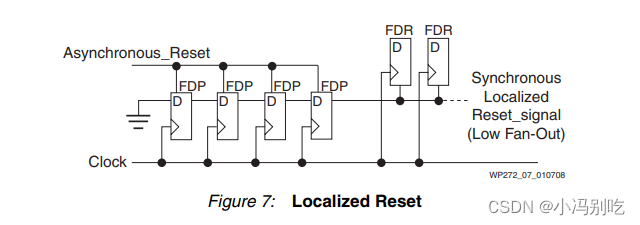

解决方法:异步复位,同步释放。再使用同步复位,同步释放。

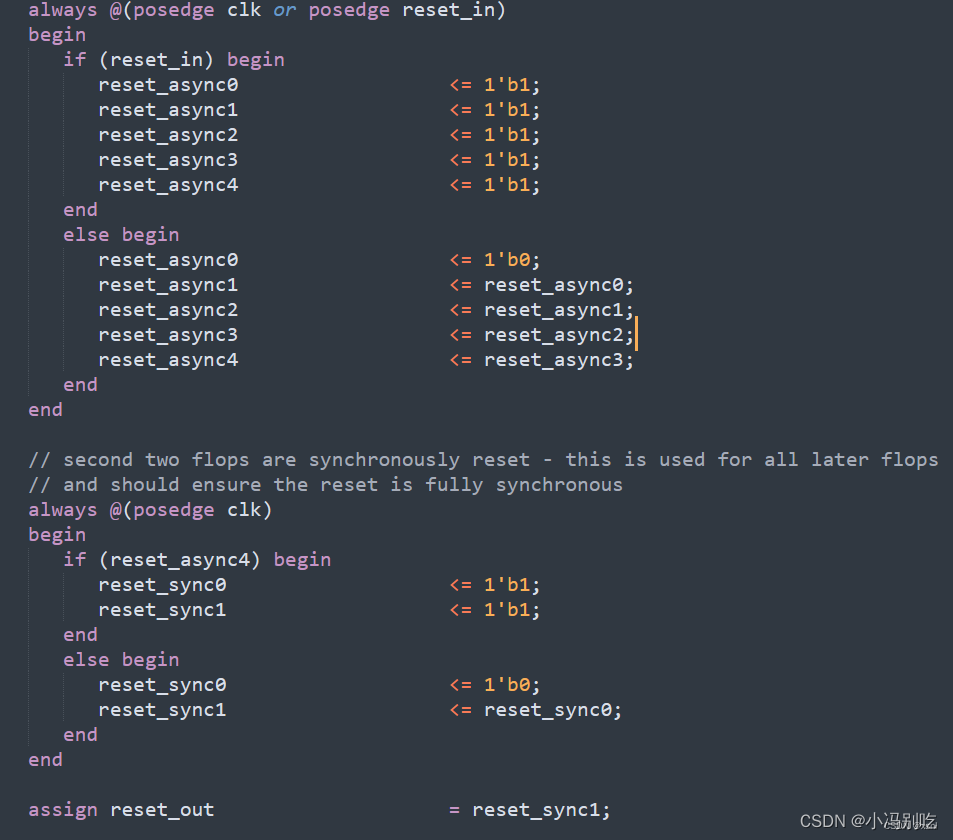

该电路对应的Verilog实现为:

第一个always块为异步复位,同步释放,第二个always块为同步复位同步释放。

第一个always块将复位信号延时了四拍,为何?Reset_in信号为异步复位信号,异步信号在释放的时候如果出现亚稳态则会造成数据的混乱,因此后面进行打四拍的操作,打四拍有两个目的,第一个目的是为了避免异步信号释放产生的亚稳态问题,第二个目的是为了将reset_async信号进行展宽,最终得到与时钟同步的复位信号。

第二个always块是同步复位同步释放,reset_async4已经和时钟同步,已经和时钟同步的信号满足建立时间与保持时间要求,同步电路一般不会产生亚稳态,但由于时钟抖动、时钟偏移等因素,为了保证reset_sync0不受亚稳态的影响,再打一拍把可能的亚稳态隔离开。

4.一种简单有效的复位方式:异步复位同步释放

这种方式相当于是对Xilinx推荐的同步复位方式中的异步复位同步释放部分的截取。

实现电路为:

具体代码如下:

时序分析:

参考:

1、csdn:xnsl复位总结。

2、Xilinx官方文档:wp272

3592

3592

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?