FPGA内部资源及层级结构总结

以Xilinx7系列为例介绍FPGA内部资源。7系列设计使能和复位信号时,统一为高电平有效。

1.FPGA内部资源组成

FPGA主要有六部分组成:可编程逻辑单元、嵌入块状RAM、可编程输入输出单元、内嵌的底层功能单元和内嵌专用硬件模块、布线资源、完整的时钟管理。其中最为主要的是可编程输出输出单元、可编程逻辑单元和布线资源。

1.1可配置逻辑单元

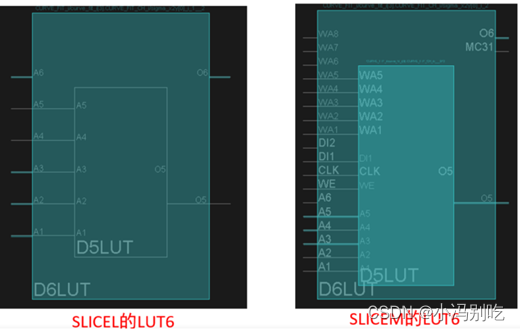

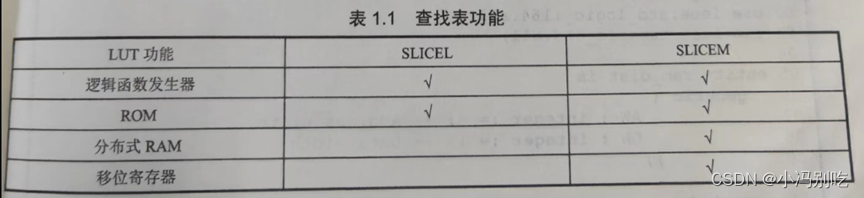

可配置逻辑单元CLB(Configurable Logic B)由两个slice组成,slice又有slicel(logic)和slicem(memory)之分,slice内部资源有4个LUT6,三个数据选择器(MUX),一个进位链(Carry Chain)和8个触发器(Filp-Flop)组成。虽然silce都是由这些资源构成,但是由于两者的LUT6的功能不同,最后将其分为sliceL和sliceM。

因此CLB也因此由slice的类型可以分为四种CLBLL,CLBLM,CLBML,CLBMM。

Slicem的分布式RAM:在slicem中LUT6不仅可以被配置为ROM,还可以被配置为RAM,这种RAM称为分布式RAM。一个LUT6可以配置64*1的RAM,其中写操作为同步,读操作为异步,如果要使用同步读操作,需要占用额外的ff,这样会增加一个时钟的延时,但是会提升系统的性能。

Slicem的移位寄存器:每个LUT6可实现深度为32的移位寄存器,且同一个Slicem中的LUT6可以级联形成128深度的移位寄存器。

1.2储存单元(Block RAM ,BRAM)

RAM就是一张存储表,可写、可读。只要提供地址信息与数据,就可以往指定的地址写入数据,此谓存入信息;同样的,只要提供地址信息,就可以从指定的地址将存储的信息读出来,此谓读取信息。

BRAM,Block RAM,俗称块RAM。BRAM是相对DRAM来说的,DRAM是分布式RAM,是由遍布FPGA全片的逻辑资源LUT构成的RAM(所以叫分布式RAM)。而BRAM则是一整块,完整地固定在FPGA内部的嵌入式资源构成的RAM(所以叫块RAM)。分布式RAM对于一些小规模的数据存储可能比BRAM来说可以获得更好的性能。

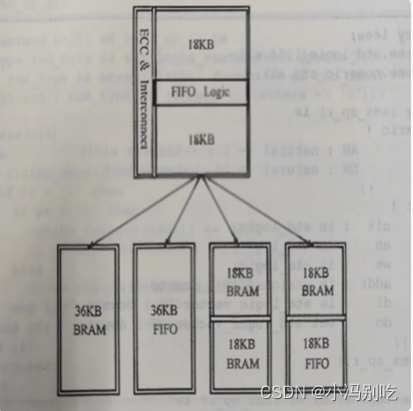

每个BRAM资源可以存储36Kb的数据,这意味着一个最小的BRAM资源是36Kb。但其实36Kb的BRAM还可以切割成2个18Kb的BRAM,或被切割为一个18kb的FIFO。但是由于两个18kb的BRAM不能公用其中的FIFO logic部分(具体是用于生成FIFO控制信号包括读写地址等部分),因此无法将一个36kb的BRAM当作两个18KB的FIFO,一个18Kb的BRAM或FIFO是BRAM的最小实现形式。BRAM的结构和应用情景如下图所示。

BRAM的使用:

1、对于2个相邻的BRAM可以级联配成72Kb的BRAM,这也是我们使用大容量BRAM的实现基础。

2、真双口RAM(True Dual-port RAM),伪双口RAM(Simple Dual-port RAM),单口RAM(Single-port RAM),FIFO等。

1.3底层内嵌的功能单元以及内嵌专用硬件模块

主要包括 DLL、 PLL、 DSP、 CPU 等,现在越来越丰富的内嵌的功能单元,使得 FPGA 成为了系统级的设计工具,使其具备了软硬件联合设计的能力,逐步向SOC 平台过渡。

内嵌专用硬件模块是相对于底层嵌入的软核而言的(mircro_blaze),FPGA内部集成的强大硬核等效于ASIC电路,如专用乘法器用于提高乘法速度,串并收发器(SERDES) 将收发速度提升到数十Gbps,如我们经常看到的一些芯片参数(GTx,即Gigabyte Transfer,兆比特传输,GTP < GTX < GTH ),CPU和DSP用于构建SoC等。

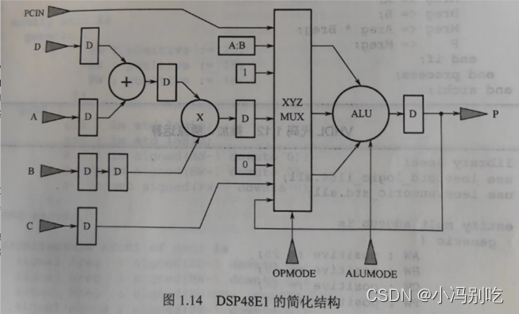

运算单元DSP

DSP48E1支持25*18(被乘数为25bit,乘数为18bit)的有符号乘法或24*17的无符号乘法。在默认情况下,对于乘法、乘加/乘减、乘累加和预相加运算vivado都会将其映射为DSP。DSP48E1内部寄存器只支持同步复位,而不支持异步复位。为获得最高性能,采用DSP48E1实现上述乘法运算时需要三级流水(输入数据寄存,乘法器寄存器输出寄存和ALU输出数据寄存)。

GT高速收发器

单独讲。

1.4可编程输入/输出块(IOB)

为了便于管理和适应多种电器标准, FPGA 的 IOB 被划分为若干个组(bank),每个 bank 的接口标准由其接口电压 VCCO 决定,一个 bank 只能有一种 VCCO,但不同 bank 的 VCCO 可以不同。只有相同电气标准的端口才能连接在一起, VCCO 电压相同是接口标准的基本条件。

1.5丰富的布线资源

布线资源连通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。主要分为四类:全局布线资源、长线资源、短线资源、分布式布线资源。

- 全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

- 长线资源,用于完成芯片bank间的告诉信号和第二全局时钟信号的布线;

- 短线资源,用于完成基本逻辑单元之间的逻辑互联和布线;

- 分布式的布线资源,用于专有时钟、复位等控制信号线

1.6数字时钟管理器DCM

目前,业内大多数FPGA均提供数字时钟管理,在内部资源中通常整合为CMT(Clock Manage Tile,时钟管理模块),每个区域对应一个CMT,一个CMT由一个MMCM(Mix-mode Clock Manager)和1个PLL(Phase Locked Loop)组成。主要起到频率综合、去抖动和去偏斜的作用。

2.FPGA内部层级划分

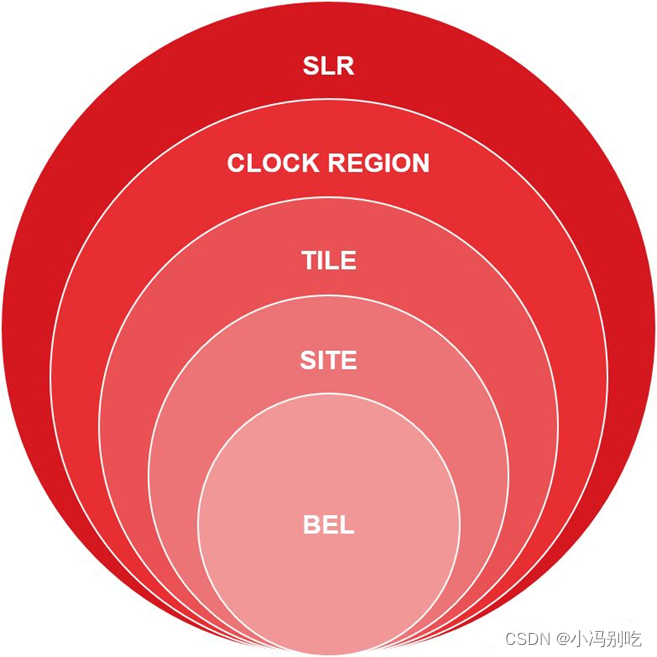

在Xilinx FPGA中,从底层到整个设备可以划分为6个层次(级):

- BEL

- Site

- Tile

- FSR

- SLR

- Device

2.1BEL(Basic Element of Logic)

最底层的基本元素,由于其不可分割性,也叫原子单位,

LUT、FF、CARRY等都属于Logic BEL的一种。

在Vivado综合或实现的Design中,可以看到会在每一个模块下都会有Nets和Leaf Cells。Leaf Cells就是FPGA中一个个真实存在的硬件模块,Vivado中place_design做的工作就是把这些Leaf Cells放到合适的BEL上。

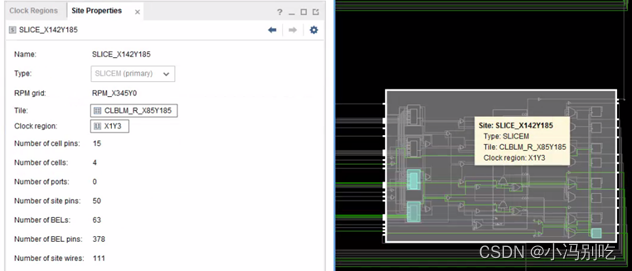

2.2Site

一系列相关的元素与它们的连线组成了Site,Site中主要包含下面三种:

- BEL

- Site的输入输出管脚

- Site内部的连线

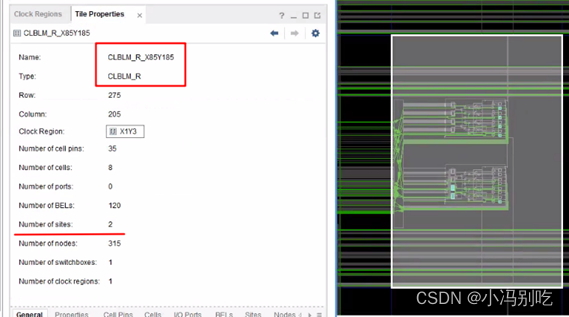

Site一般都是跟Slice、DSP48、BRAM等是对应的,换句话说site的种类有Slice、DSP48、BRAM等。sites是一种设计结构,而slice只是资源分布的一个结构。我们以Slice为例,在7系列的FPGA中,一个CLB有两个Slice,下图的白色框是一个CLB,从左边的Properties中可以看出,包含了两个site,其实就是包含了两个Slice。每个Slice都有独立的site,所以这个CLB中就有两个sites。

Xilinx FPGA中很多元素的位置都是以_X_Y结尾来表示该元素在坐标中的位置,下图中的这个Slice的位置是X142Y185。

2.3Tile

Tile是比Site更高一级的概念,一个Tile里面包含多个Site,Tile没有pin的概念,一般来说,一个tile其实就是一个CLB。

不同类型的TILE按列的方式排列构成了CLOCK REGION,

实际上,考虑到时钟走线,每片FPGA都被分割为多个CLOCK REGION。

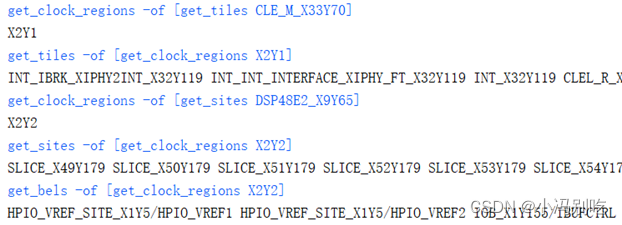

CLOCK REGION包含多个TILE,而TILE又有SITE构成,SITE又有BEL构成,因此,已知CLOCK REGION可以很方便地找到其下的TILE、SITE和BEL。反过来,已知SITE或TILE,可以找到其所在的CLOCK REGION。但如果已知BEL,不能直接找到其所在的CLOCK REGION。

2.4FSR

FSR就是Fabric Sub Region or Clock Region,是由一片Tile组成的,在UltraScale的FPGA中,所有的FSR的高度都有60个CLB,但宽度不尽相同。

时钟routing和distribution的粒度与FSR相同,在UltraScale的FPGA中,有24个水平的routing track,24个垂直的routing track,24个水平的distribution track和24个垂直的distribution track,相邻的FSR就靠这些track互连。

2.5SLR

SLR就是Super Logic Region,超级逻辑区域。这个概念仅针对SSIT工艺的FPGA,也就是包含多个die的芯片,这样每个die就被称为一个SLR。SLR(Super Logic Region)由多个CLOCK REGION构成。单die芯片只包含一个SLR;而多die芯片也就是SSI器件,则包含至少两个SLR。

SSI是Stacked Silicon Interconnect的缩写。SSI芯片其实就是我们通常所说的多die芯片。其基本结构如下图所示。可以看到SSI芯片的基本单元是SLR(Super Logic Region),也就是我们所说的die。SLR之间通过Interposer“粘合”在一起。每个SLR可看作一片小规模FPGA。

2.6Device

这个概念就是指整个FPGA;如果是单个die的片子,那么多个FSR就组成了Device,如果是多个die的片子,那么多个SLR组成了Device。

3.tcl脚本查找关系

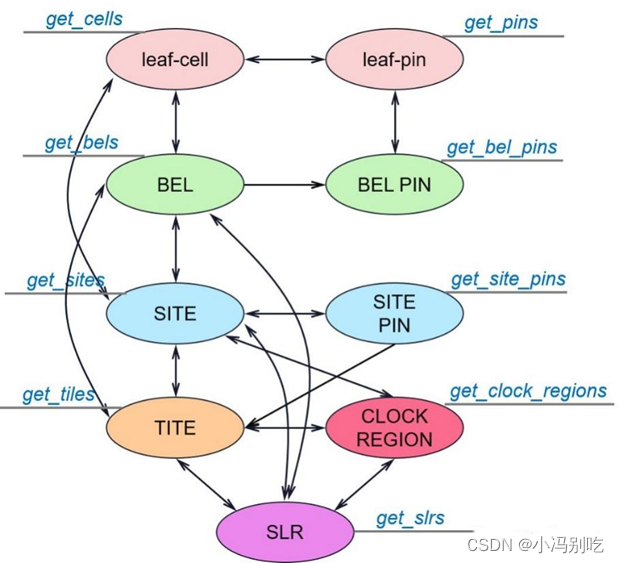

BEL、SITE、TILE、CLOCK REGION和SLR在使用Tcl命令时之间的关系。

如下图所示,图中A->B,表示已知A,可通过选项-of获取B,也就是-of A。

层级使用tcl脚本查找关系

本文介绍了Xilinx7系列FPGA的内部资源,包括可编程逻辑单元CLB、嵌入式BRAM、可编程输入输出单元IOB、内建功能单元如DSP和时钟管理模块。CLB由slice组成,BRAM提供了分布式和块RAM,DSP48E1用于高效乘法运算。此外,文章还详细阐述了FPGA的层级结构,从BEL到Device的六个层次,帮助读者理解FPGA的设计和组织方式。

本文介绍了Xilinx7系列FPGA的内部资源,包括可编程逻辑单元CLB、嵌入式BRAM、可编程输入输出单元IOB、内建功能单元如DSP和时钟管理模块。CLB由slice组成,BRAM提供了分布式和块RAM,DSP48E1用于高效乘法运算。此外,文章还详细阐述了FPGA的层级结构,从BEL到Device的六个层次,帮助读者理解FPGA的设计和组织方式。

1560

1560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?