上次做某家公司笔试题提到了输入输出的最大最小延时。因此想对这方面做更加深层次的理解。

这里借鉴大佬@屋檐下龙卷风的精彩分析让我对建立时间和保持时间以及两个板级时序路径有更深更通俗的理解。

详细分析见:FPGA静态时序分析——IO口时序(Input Delay /output Delay) - 屋檐下的龙卷风 - 博客园 (cnblogs.com)

此分析是在建立时间和保持时间分析的基础上,因此需要先理解建立时间和保持时间要求。这部分不再赘述。

直接进入正题:

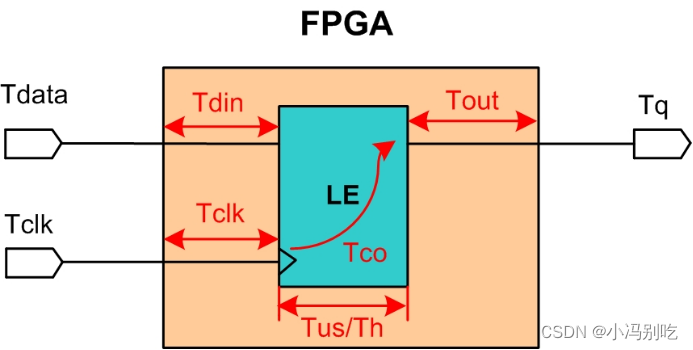

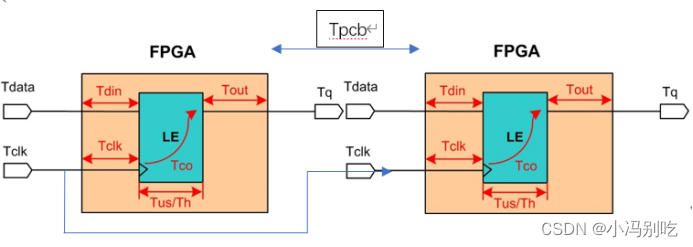

对于一个FPGA板子中的一个ff来说,它是时序路径可以简化为如下图所示:

先说注意事项:

(1)数据早来晚走可以避免时序违例。

分析最坏的情况那就是数据晚来早走。

晚来是由于Tco和Tdata太大,导致数据到下一个触发器的捕获沿更慢,很容易在Tsu内来,导致不满足建立时间要求。

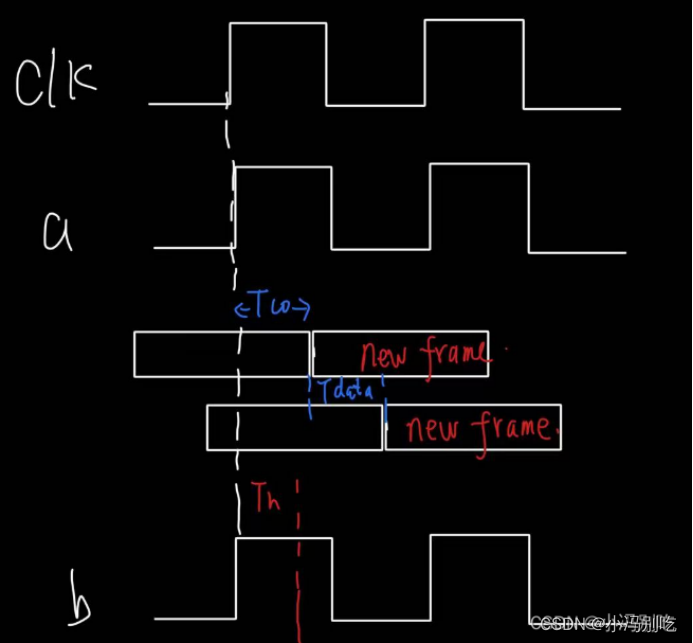

早走是因为Tco和Tdata太小,导致下一个数据到达太快,把上个数据挤走了,导致当前数据不满足建立时间要求。具体不太好理解,所以见下图:

无skew下满足建立时间要求

无skew下不满足建立时间要求。由于Tco+Tdata太小。

(2)明确set_input_delay 以及set_output_delay都是对本级FPGA来说,告诉本级FPGA如何对输入端的建立时间和保持时间约束之后,做Tdin做出限制,以及告诉本级FPGA如何对输出端的Tco+Tout做限制以满足下一级的建立时间与保持时间要求。

(3)如何去理解skew呢?它对建立时间有什么影响?在理解skew对Tsu的影响之后就很好理解输入最大延时的问题。在基本的两个触发器之间建立时间分析的时候从三个方面理解:

没有skew 由Tco+Tdata+Tsu<=Tcycle可知,需要在一个时钟周期Tcycle内完成三件事:内部寄存器传输(Tco)、走线延时(Tdata)以及建立时间要求(Tsu)。skew的出现会让这三件事的完成更加容易或者更加艰难。

skew为正 说明a的上升沿到b的上升沿中间的时间比无skew更大,对于Tsu来说更加有利,因为两个上升沿之间的时间更加充裕,换句话说,留给满足建立时间的余量更多。(同时更难满足保持时间要求)。skew为正值时,越小对满足建立时间要求好处就越小,只要skew存在且为正,就是对满足建立时间要求有利,

skew为负 说明a的上升沿到b的上升沿中间的时间比无skew更小,对于满足Tsu要求来说更加紧张,因为要在更少的时间内完成Tco和Tdata,所以这是最坏的情况。

正文:

1.set_input_delay 以及set_output_delay概述

- set_input_delay用于指定输入数据引脚相对于其时钟沿的路径延时,主要用于数据路径中的pin2reg,分析从外部芯片到自己内部寄存器的延迟,需要满足自己芯片内部寄存器的建立保持时间 ,设定的最大值和最小值分别用于建立和保持时间分析。对自己来说当然是要满足建立时间和保持时间要求,对建立时间和保持时间考虑。

- set_output_delay用于指定输出数据引脚相对于其时钟沿的路径延时,主要用于数据路径中的reg2pin,分析从自己内部寄存器到外部芯片的延迟,需要满足外部芯片中寄存器的建立保持时间,设定的最大值和最小值分别用于建立和保持时间分析。

2.输入最大延时

最大输入延时(input delay max),归根结底还是建立时间与保持时间分析,因此最大输入延时还是在建立时间与保持时间分析的基础上进行的,只不过是加入了最大的概念,换种说法来说,就是对本级满足建立时间要求最不友好的情况下仍然满足建立时间要求,能采集到从上一级传给本级的数据。可以认为Tsu为定值。

假设右边的FPGA为本级的FPGA,左边的FF为上一级输出的最后一个FF,右边的FF为本级接收到第一个FF的。

建立时间的影响因素主要有:TIco(上一级ff的Tco)、TIdata(Tout+Tpcb)表示输入路径延时、以及时钟偏移skew(默认指的是Tclk2-Tclk1)。建立时间要求在不考虑skew的情况下,需要的条件为

TIco+Tout+Tpcb+Tdin+Tsu<=Tcycle

加入skew之后变为:

TIco+Tout+Tpcb+Tdin-skew+Tsu <=Tcycle

对于FPGA的FF来说,它的Tco是一个参数值,这个值受器件工艺,温度等影响,它有一个最大值与最小值。在考虑对于本级FPGA的第一个FF建立时间要求最坏的情况下,那应该是上一级的TIco取最大值。

Tout+Tpcb可以把它理解为TIdata,一般来说两个FPGA之间的Tpcb是确定的(个人理解,因为板件的时延是在做板子的时候已经确定了)。那能变的就是Tout以及Tdin,考虑对于本级FPGA的第一个FF建立时间要求最坏的情况下,Tout的值肯定是越大越坏,Tdin是本级FPGA需要进行调节的。因此TIdata越大对本级PFGA的第一个FF建立时间要求越不友好,这个也很好理解,TIdata越大,因为在一个时钟周期内(不考虑skew的情况下),需要完成TIco,TIdata、Tdin和Tsu。Tdata变大,那么建立时间余量越小,对满足FF的建立时间要求要求越难。

由注意事项的(3)可知,如果存在skew且其为负值,对满足建立时间要求极不友好。

因此最大的输入延时为:TIco(max)+TIdata(max)-skew(min)。

换个熟悉的写法就是 Tco(max)+Board Delay(max)-clock delay(min)

其中Board Delay = Tout+Tpcb。

3、输入最小延时

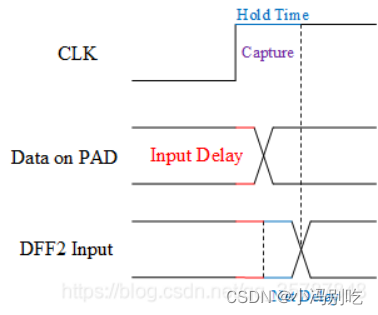

ok 这么理解之后就可以考虑最小输入延时,这个情况就是对本级满足保持时间要求最不友好的情况,在这种情况下,本级仍然满足保持时间要求,使得数据在保持时间内不变。可以认为Th为定值。

保持时间的影响因素主要有:TIco(上一级ff的Tco)、TIdata(Tout+Tpcb)、以及时钟偏移skew(默认指的是Tclk2-Tclk1)。建立时间要求在不考虑skew的情况下,需要的条件为

Tco+Tout+Tpcb+Tdin >=Th

加入skew之后变为:

Tco+Tout+Tpcb-skew+Tdin >=Th

这个公式也很好理解:

没有skew :new frame是新来的一个数据,这个数据不能来的太快,把上一帧挤走,下一个数据什么时候来呢,就是TIco+TIdata+Tdin,这个值一定要大,让数据晚点来,而且这个值应该至少为Th吧,这样才不会把上一帧挤到前面去,让上一帧不满足保持时间要求。

而我们现在考虑的是外部输入的最坏情况,也即TIco+TIdata最小,就是对本级建立时间最不友好的情况,这里借鉴一下(2条消息) vivado时序约束——(最大/最小)输入输出延时_vivado 输入输出约束参数说明_小裘HUST的博客-CSDN博客中的最小输入延时分析图。

红色即为TIco+TIdata,因此在它太小的情况下,还需要Tdin来进行时延补偿才能满足捕获沿的保持时间要求。

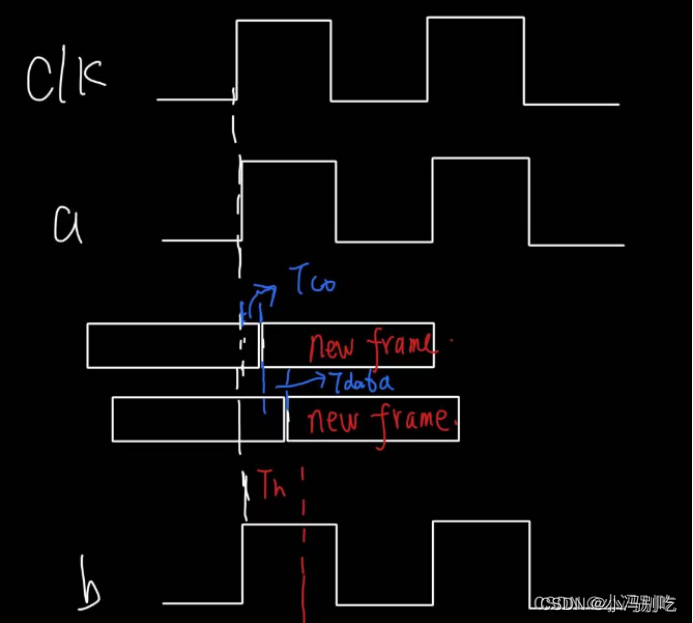

ok,现在加入skew(可以将上图中捕获沿往右移动进行理解分析,相当于skew使得TIco+TIdata变得更小了),在(3)讲过,skew为正是对建立时间有利,对保持时间有害;skew为负是对建立时间有害,对保持时间有利。我们就要考虑对建立时间最不利的情况。TIco+TIdata越小 ,越难满足保持时间要求,再火上浇油,雪上加霜,skew再来掺和一脚,让skew最大。在这种Tco+Tdata最小,skew最大的情况下,就是求得的最小输入延时。

根据上面的分析,就很容易得出最小输入延时为:

Tco(min)+Tdata(min)-skew(max)

换个熟悉的写法就是 Tco(min)+Board Delay(min)-clock delay(max)

其中Board Delay = Tout+Tpcb。

4、输出最大延时(output max)

还是这张图,只不过左边和右边的角色换了一下,左边是当前一级的FPGA,右边是下一级的FPGA,因此,需要约束的是本级的Tco+Tout。外部输出延时根据上一部分的分析可以知道是Tpcb+Tdin+Tsu。最大输出延时是指在下一级寄存器在对建立时间要求最不友好时,仍然刚好满足建立时间要求的情况。那么此时延时最大值很容易知道是board delay(max)+Tsu,若考虑skew,那么就要考虑对下一级建立时间最不友好的情况,也就是skew(min)。

所以最大输出延时为:board delay(max)+Tsu - skew(min)。

其中Board Delay = Tdin+Tpcb。

按照这个式子对Tco+Tout进行约束。

5、最小输出延时

由于输出最小延时是为了保证下一级芯片电路的保持时间来说的,假设已知下一级的建立时间要求为Th。在满足下一级保持时间前提下,对保持时间要求最不友好的情况下,线延迟很小,时钟偏移很大。本级FPGA应该做出的决策:Tco+Tout应该越大越好。

board delay(min)- Th - skew(max)

其中Board Delay = Tdin+Tpcb。

按照这个式子对Tco+Tout的值进行约束。

总结:

- 只要说到最大都是和建立时间Tsu有关,只要说到最小都是和保持时间Th有关。

- 求得最大最小输入延时对本级FPGA约束的是:

Tdin的最大值和最小值。最大输入延时对应的是最小值,最小输入延时对应的是最大值。

求得最大最小输出延时对本级FPGA约束的是:

Tco+Tout的最大值和最小值。最大输出延时对应的是最小值,最小输出延时对应的是最大值。

总结纯属个人理解,如果有误,欢迎交流指正。

1820

1820

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?