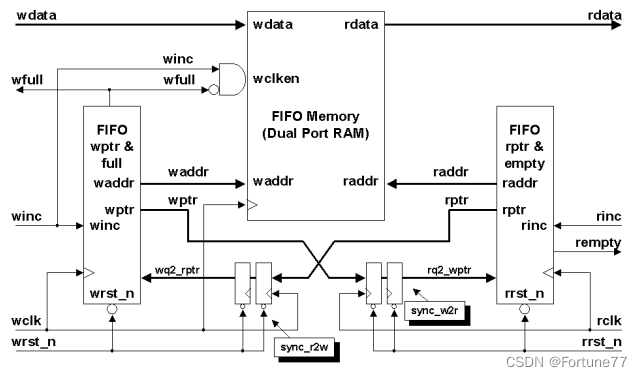

和同步fifo一样,中间是双口的ram,左右两个模块分别是读写地址的产生和判断空满信号。比如在FIFO wptr &waddr模块中产生ram的地址信号waddr,然后将waddr这个二进制编码的地址信号转换为格雷码来进行跨时钟域处理(注意,二进制编码转换格雷码是组合逻辑,组合逻辑的输出不能直接的进行跨时钟域,因为毛刺会影响跨时钟域的结果,需要将组合逻辑的输出放到寄存器中,之后再进行跨时钟域的处理)。在读时钟域下的rq2_wptr信号与原来的写时钟域的下的rptr信号来进行空状态的判断,以上是从写时钟域到读时钟域下的操作,从读时钟域到写时钟域同理。

使用格雷码的根本原因就是就算跨时钟域的时候,出现了亚稳态,整个fifo的功能也不会出现错误。比如用二进制的waddr来进行跨时钟域,比如waddr从7到8的变化(0111->1000),raddr此时处于6的位置,跨时钟域的时候,寄存器会随机的取到中间状态的一个值,所以在rq2_wptr处得到的结果可能是2,此时raddr是6,相当于fifo存就存到了2,读却读到了6,这样会使fifo的功能错误。如果使用格雷码,waddr从7到8的变化(0100->1100),中间就涉及到了一个值的变化,就算出现亚稳态,不是1100就是0100,是1100的话,正好功能正确,如果是0100的话,不影响fifo的读,最多可能出现fifo的假空判断,不会出现fifo功能的错误,即读大于写(读指针指向当前的值,写指针指向下一时刻的值)

在格雷码的基础上,扩展一位最高位,这个最高位可以方便判断空满,当写指针转了一圈又回来,说明把fifo写满了,此时读指针没有动的话,说明fifo是满的,此时扩展后的读指针和扩展后的写指针最高位不同,其他位置都一样。如果fifo是空的话,二者全相等。空标志在读时钟域判断,满标志在写时钟域判断

假空假满根本原因是因为打两拍的原因,比如写指针打两拍到了读时钟域,此时写指针已经大于了同步的写指针,如果此时判断为空的话,实际上,写指针在同步的时间里已经存了值进去,这样就是假空。假满同理,但是这个对fifo功能没有影响,比如fifo的深度是6,在1的时候空标志位拉高,只能说fifo实际的深度只有5,这是一种保守设计,对功能没影响。

关于异步FIFO设计,这7点你必须要搞清楚_孤独的单刀的博客-CSDN博客_异步fifo为什么要打两拍

这篇文章从快慢时钟详细的分析了空满的判断已经对fifo功能影响

二进制编码转换格雷码是组合逻辑,组合逻辑的输出不能直接的进行跨时钟域,因为毛刺会影响跨时钟域的结果,需要将组合逻辑的输出放到寄存器中,之后再进行跨时钟域的处理

async_fifo的设计代码(欢迎大家挑错)

module async_fifo(wclk,wr,din,full,rclk,rd,dout,empty,rst_n);

parameter data_width = 16;

parameter data_depth = 8;

parameter ram_depth = 256;

input rst_n;

input wclk;

input wr;

input [data_width-1:0] din;

output full;

input rclk;

input rd;

output [data_width-1:0] dout;

output empty;

reg [data_width-1:0] dout;

wire empty;

wire [data_depth-1:0] wr_addr;

wire [data_depth-1:0] rd_addr;

reg [data_depth:0] wr_addr_ptr;

reg [data_depth:0] rd_addr_ptr;

reg [data_depth:0] wr_addr_gray_rdy;

wire [data_depth:0] wr_addr_gray;

reg [data_depth:0] wr_addr_gray1;

reg [data_depth:0] wr_addr_gray2;

reg [data_depth:0] rd_addr_gray_rdy;

wire [data_depth:0] rd_addr_gray;

reg [data_depth:0] rd_addr_gray1;

reg [data_depth:0] rd_addr_gray2;

assign wr_addr = wr_addr_ptr[data_depth-1:0];

assign rd_addr = rd_addr_ptr[data_depth-1:0];

assign wr_addr_gray = (wr_addr_ptr >> 1) ^ wr_addr_ptr;

assign rd_addr_gray = (rd_addr_ptr >> 1) ^ rd_addr_ptr;

reg [data_width-1 : 0] ram_fifo [ram_depth-1:0];

integer i;

always@(posedge wclk or negedge rst_n)

if(!rst_n)begin

for(i=0;i<ram_depth;i=i+1)

ram_fifo[i] <= 0;

end

else if(wr && (!full))

ram_fifo[wr_addr] <= din;

always @(posedge rclk or negedge rst_n) begin

if(!rst_n)

dout <= 0;

else if(rd && (!empty))

dout <= ram_fifo[rd_addr];

end

always @(posedge wclk or negedge rst_n) begin

if(!rst_n)

wr_addr_ptr <= 0;

else if(wr &&(!full))

wr_addr_ptr <= wr_addr_ptr + 1;

end

always @(posedge rclk or negedge rst_n) begin

if(!rst_n)

rd_addr_ptr <= 0;

else if(rd &&(!empty))

rd_addr_ptr <= rd_addr_ptr + 1;

end

always@(posedge wclk or negedge rst_n) begin

if(!rst_n)

wr_addr_gray_rdy <= 0;

else

wr_addr_gray_rdy <= wr_addr_gray;

end

always@(posedge rclk or negedge rst_n) begin

if(!rst_n)

rd_addr_gray_rdy <= 0;

else

rd_addr_gray_rdy <= rd_addr_gray;

end

always@(posedge wclk or negedge rst_n)begin

if(!rst_n)begin

rd_addr_gray1 <=0;

rd_addr_gray2 <=0;

end

else begin

rd_addr_gray1 <= rd_addr_gray_rdy;

rd_addr_gray2 <= rd_addr_gray1;

end

end

always@(posedge rclk or negedge rst_n)begin

if(!rst_n)begin

wr_addr_gray1 <=0;

wr_addr_gray2 <=0;

end

else begin

wr_addr_gray1 <= wr_addr_gray_rdy;

wr_addr_gray2 <= wr_addr_gray1;

end

end

assign empty = (wr_addr_gray2 == rd_addr_gray)? 1'b1:1'b0;

assign full = (wr_addr_gray[data_depth:data_depth-1'b1] != rd_addr_gray2[data_depth:data_depth-1'b1]) && (wr_addr_gray[data_depth-1:0] == rd_addr_gray2[data_depth-1:0]);

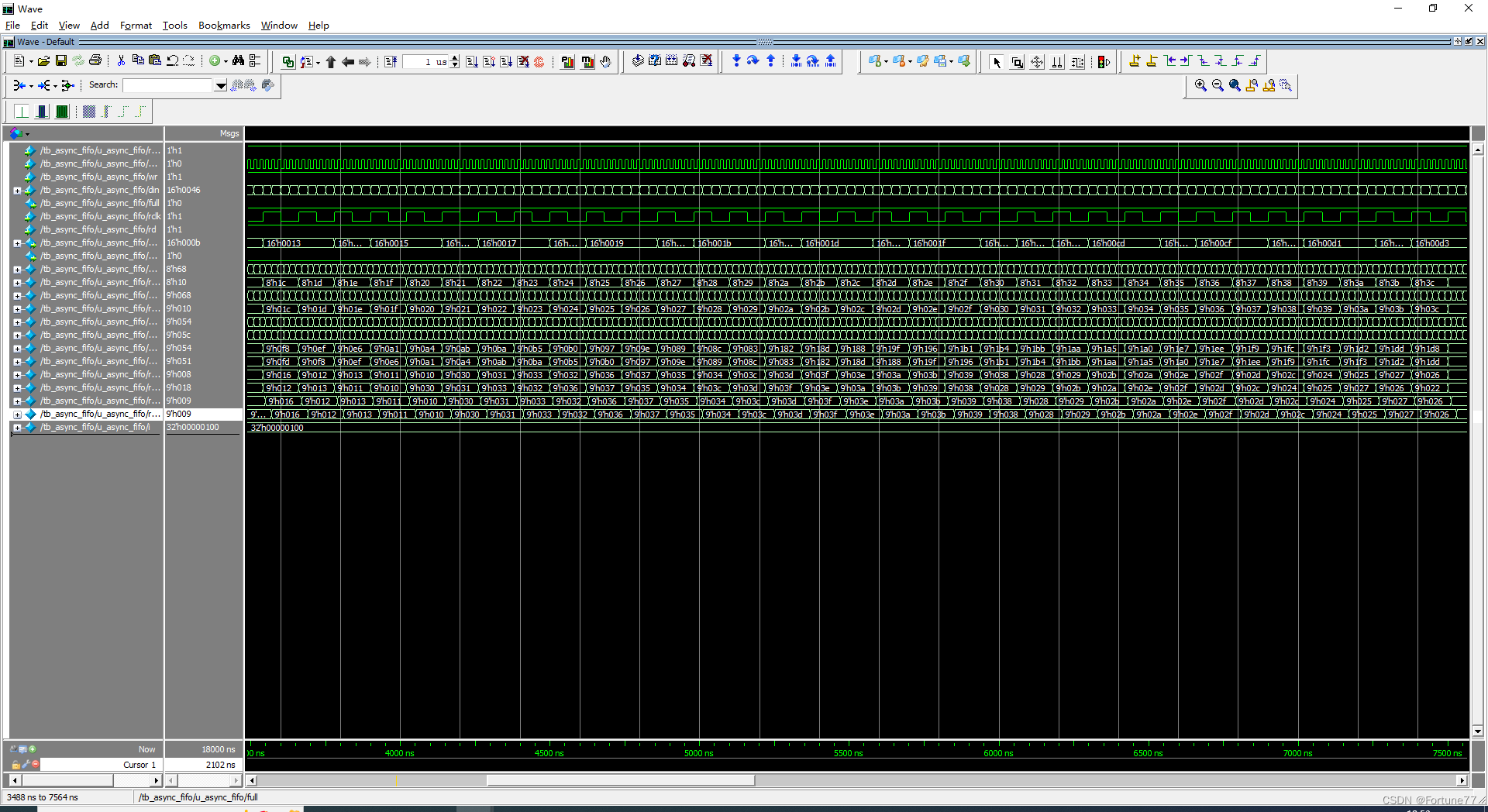

endmodule仿真波形

1198

1198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?