-

写在前面 ——Fraay

大家好,本人普通一本大学的电子信息工程小白一枚,在CSDN上面白嫖程序已经很久了,尤其是这一个多月一直在钻FPGA,现在稍微有点起色,于是把自己的一点心得记录一下。希望能用最详细的语言把我自己的全部体会讲清楚,给后来的朋友们学习提供更多的方便。本人写FPGA的LOG算是用爱发电,把每一步都尽可能地说的让我自己最大程度明白,如果有错误还望读者海涵、指正,真的对所有读者能够看我写的文章而感激。

是故无贵无贱,无长无少,道之所存,师之所存也。 ——韩愈 《师说》

本次文章内容具体是如何从创建vivado到点亮一个led上板观察现象。都说点亮一个led就代表开发板已经学会一半了,说明点亮led是完整的走了一遍基础开发流程

由于本人在看各种论坛中对于上板这一步都讲的较为粗浅,而安装vivado都有很详细的流程,所以这里默认大家已经安装上了vivado以及破成功解了。

-

创建工程

1、新建一个工程,并且

点击next弹出以下弹窗

根据自己的情况修改路径

点击下一步

这一步是选择器件,我用的板卡是xilinx的BASYS3---xc7a35tcpg236-1

点击完成之后,就可以看到下面这个界面(我已经做好了翻译核解释,为了大家能更快速的认识vivado)

vivado真的是不当人,设计颜值这么高的界面但是全英文很严谨难用,还好本人英语四六级轻松通过了,看简单的英文无压力

接下来就开始进入组装各个文件的阶段了

-

添加源设计文件

我用的verilog语言,如果用VHDL的话请自行选择

我用的verilog语言,如果用VHDL的话请自行选择

(纠正一下,最后一步是点finish不是next)

这里建议什么都不要写,并且工程名字要跟这个module name保持一致。如果你想写的话,它会自动帮你把配置了的管脚加入module();里面去

仿如果不是顶层文件,可以通过右键->Set as top来设置(这里已经是顶层了,所以无法设置)

双击led_test文件,写下面的代码

module led——test(

input [2:0] sw,

output [2:0] led

);

assign led[0] = sw[0];

assign led[1] = sw[1];

assign led[2] = sw[2];endmodule

本人在自学过程过看别人的帖子很多都是直接给出代码,这样看起来十分的凌乱,并且不是自己动脑筋想的逻辑,很容易看了跟没看效果一样,为了避免这种情况,以下特意对代码进行说明(有的代码我整理好了,已经在每一行下面做了注释)

然后我们创建仿真文件

_tb就表示仿真文件testbench

一路next点下去,打开仿真文件

然后打开仿真文件,编写

由于这个工程太简单了,就先不写了,后面复杂的工程我会把仿真文件贴出来

下一步,在左侧点击综合等待完成,如果有报错的话就根据下面的log日志的提示找到错误

我说一下,亲身经历,message的错误有的是不准确的,如果你实在找不到,看log是最靠谱的,并且每次只解决第一个log的问题然后再综合,找下一个问题(比较花费时间)有的时候可能一个分号中文英文就能给你报错位置定位错误导致很久找不到错误,编程请细心噢

并且,请在每次修改完错误之后,保存文件,不然vivado不会更新的

-

管脚分配

成功后会弹出这个界面👇

直接点击取消

然后进行RTL门级电路设计

之后就会弹出下面的界面

这里我说一下,在进行管脚的分配,效果跟网上的添加.XDC管脚约束文件一样,但是由于那个约束文件我不会写,而且网上资料非常少,实验教材里面一般都是让你直接复制粘贴。所以我再经历了漫长的寻找之后发现了这个途径解决管脚约束问题

接下来我将讲解一下如何通过BASYS3的数据手册来配置管脚

https://www.stepfpga.com/doc/basys3%E5%BC%80%E5%8F%91%E6%9D%BF

打开这个网页,找到原理图

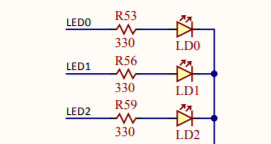

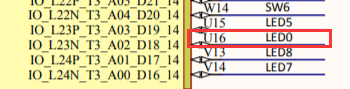

然后看这个界面,这些BANK就是所有可以外部用的io的集合找到我们要的sw和led

以下的界面是开关电路,可以看到在硬件连接方面,拨码开关连在sw0-15上,然后再👆那张bank图看到sw0,1,2分别是BANK14里面V17,V16,W16

接着我们找一下led的位置,同理

然后回到vivado界面,用刚刚的对应关系配置管脚,以及电平设置(我设置的是1.8V,有的板子也支持3.3V)

看到Fixed有勾勾就行了,然后按ctrl+s保存,就会弹出这个界面,他就已经帮你做好了xdc的书写

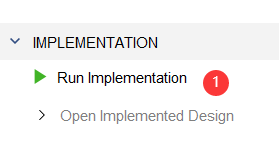

下一步时进行布局布线,非常的慢,不要以为卡了

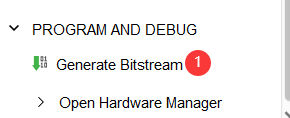

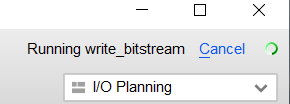

然后点击下载比特流文件,同样很慢

然后把板子跟电脑连起来(我的这个直接可以用usb连)找到Hardwork Managera

点击自动连接

点开program

之后就可以成功正常上板子观察现象了,大功告成

写在结尾,一篇文档写了大概两个小时,写的非常的详细。用爱发电属实不易,希望可以给大家带来帮助,以后有空会继续更新一些我做过的项目。

有问题可以留言

尤其希望能给在被FPGA折磨的的小丁同学一点帮助,加油吧D!

2020.9.4 于湖北工业大学

1200

1200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?