VIVADO 工具与 Verilog 语言的使用

一、实验目的和要求

熟悉 Vivado 的开发环境及开发流程,掌握 Vivado 中 Verilog HDL 文本输入设计方法, 包括仿真、综合、实现与下载。熟悉 Minisys 开发板的功能和使用方法。

二、实验内容和原理

以一个简单的 24 位拨码开关的读和 24 位 LED 灯的输出电路为例,利用 Verilog HDL 语言,在 Vivado 中创建简单的 24 位拨码开关的输入和 24 位 LED 灯的输出电路会将设计下载到 Minisys 实验平台。

三、主要仪器设备

个人电脑:Huawei Matebook 14 Windows 11 家庭中文版

类型:64位

处理器:Intel® Core™ i5-10210U CPU @ 1.60GHz 2.11 GHz

内存:16GB

四、操作方法与实验步骤

1. 拨码开关与LED灯

1.1 创建新项目

-

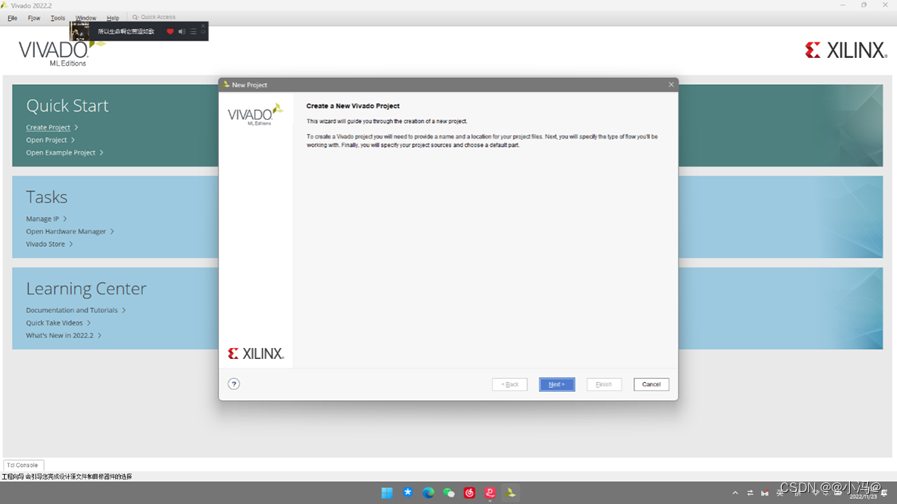

打开vivado并且点击Create Project创建一个新项目,在弹出的窗口中点击next

图 1-1 New Project

图 1-1 New Project -

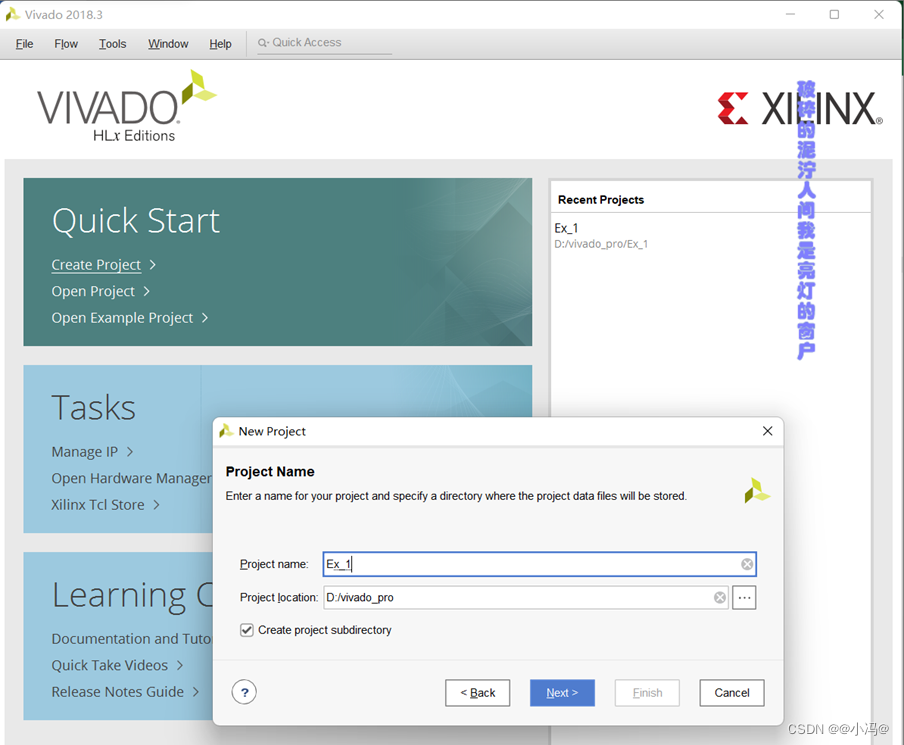

按照图示填好项目的名称和项目的路径,点击创建,最后,项目将会被创建在D:/vivado_pro/Ex_1的位置。

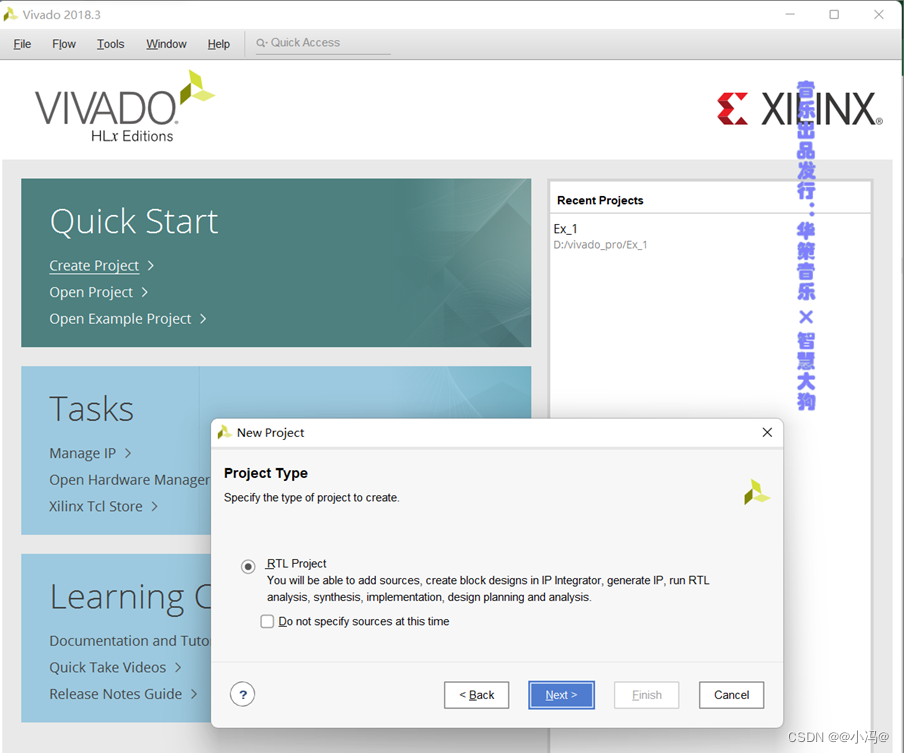

3. 选择RTL Project

3. 选择RTL Project 图 1-3 项目类型

图 1-3 项目类型 -

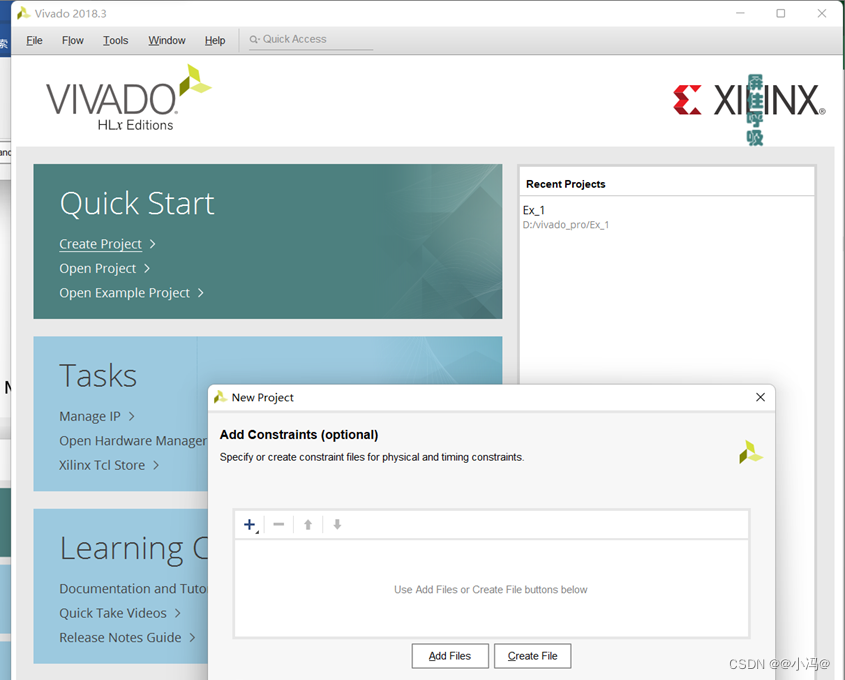

我们暂时还不添加源文件和约束文件,所以接下来的两步都直接点Next

因为不需要增加源文件,所以 Add source 窗口点击 Next(但 Target Language 选择 Verilog)。

不增加 IP 核,所以 Add ExistingIP 窗口点击 Next。

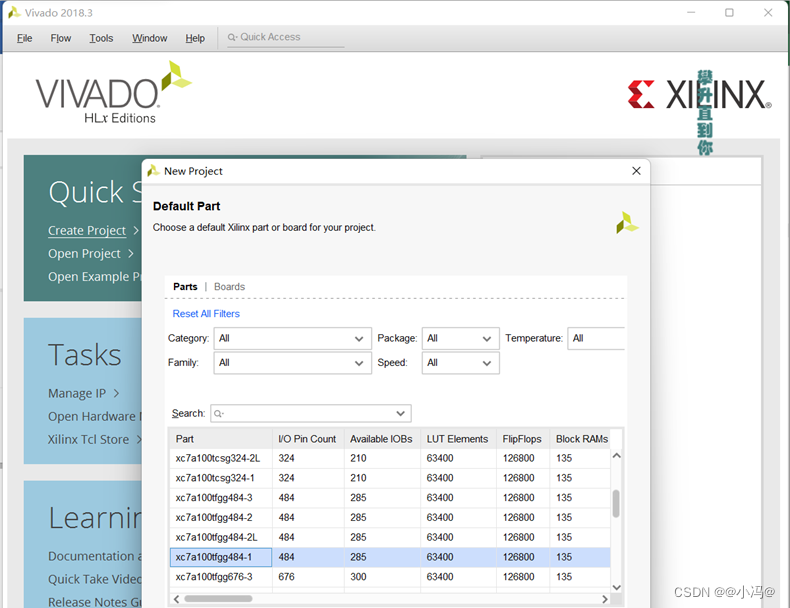

不增加约束文件,所以 Add Constraints 窗口点击 Next。 按图 1-4 选择器件为 xc7a100tfgg484-1。点击 Next。 5. 选择的芯片型号是xc7a100tfgg484-1,之后点next

5. 选择的芯片型号是xc7a100tfgg484-1,之后点next 6. 点击Finish完成项目的创建

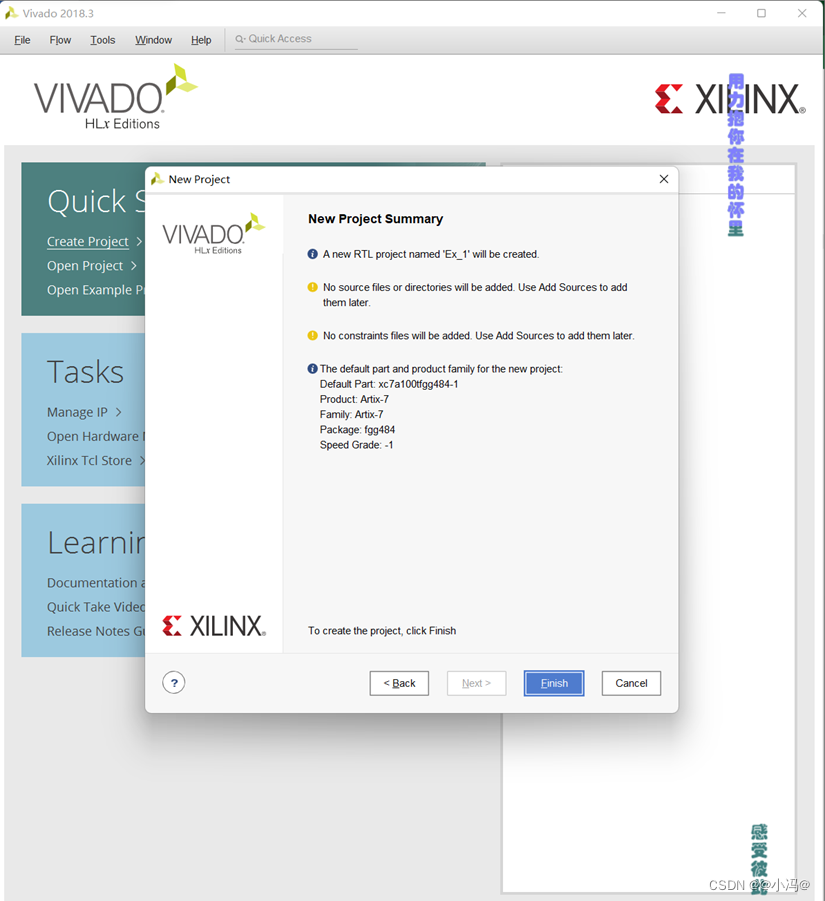

6. 点击Finish完成项目的创建 图 1-6 新项目概览

图 1-6 新项目概览

1.2 添加源代码

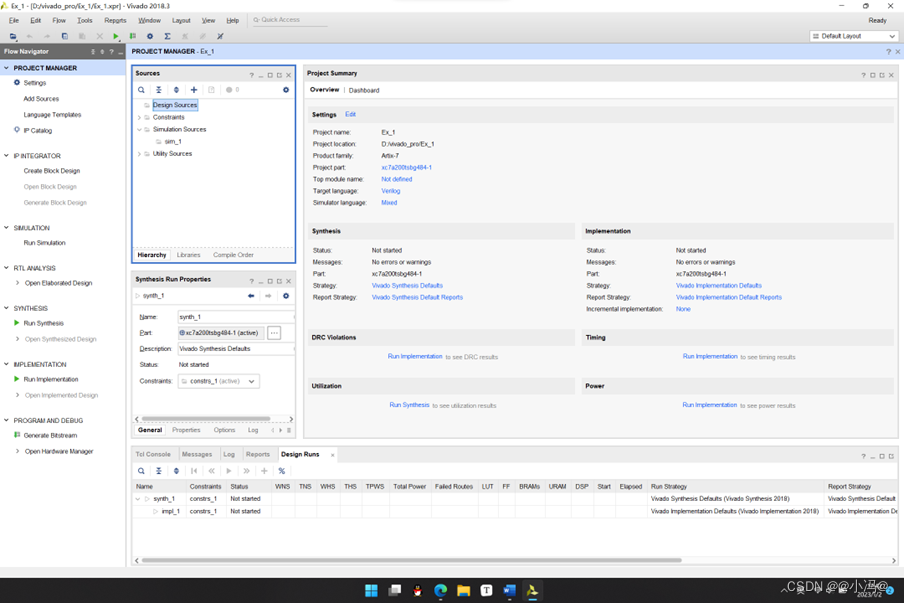

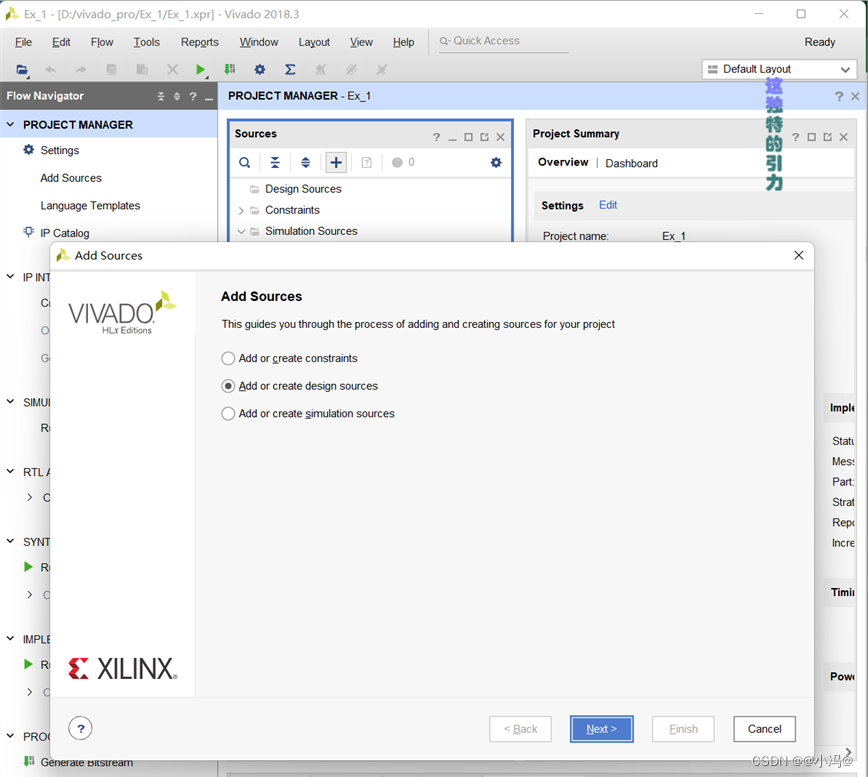

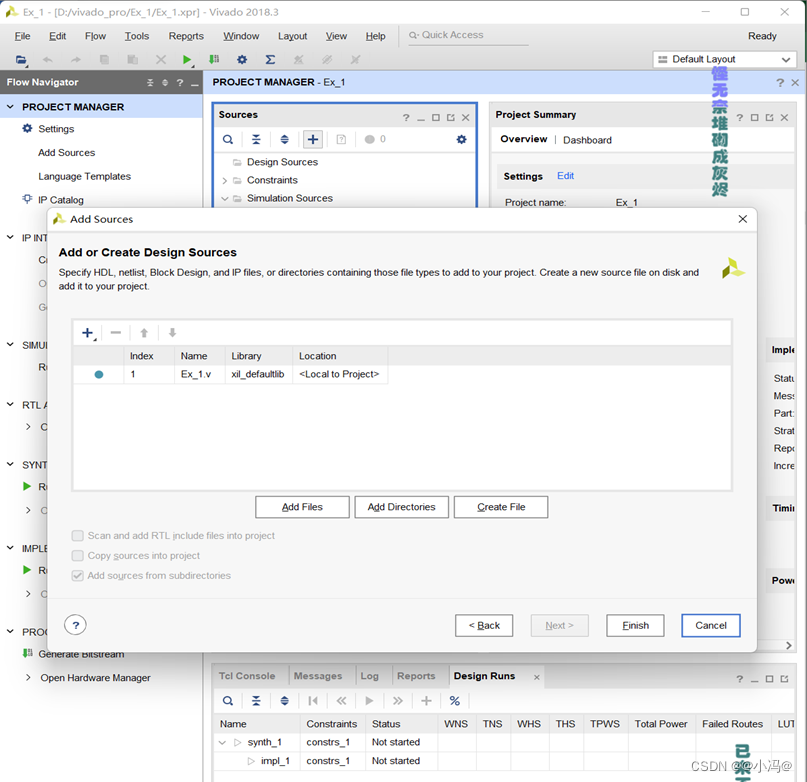

4. 选择Add sources添加源代码 图 1-7 创建新项目后的界面

图 1-7 创建新项目后的界面 图 1-8 添加源程序对话框

图 1-8 添加源程序对话框

5. 选择create file,表示我们要给项目创建新文件 图 1-9 Create Souese File 对话框

图 1-9 Create Souese File 对话框

- 点击Finish完成文件的创建

图 1-10 创建设计文件后的添加或创建设计文件对话框

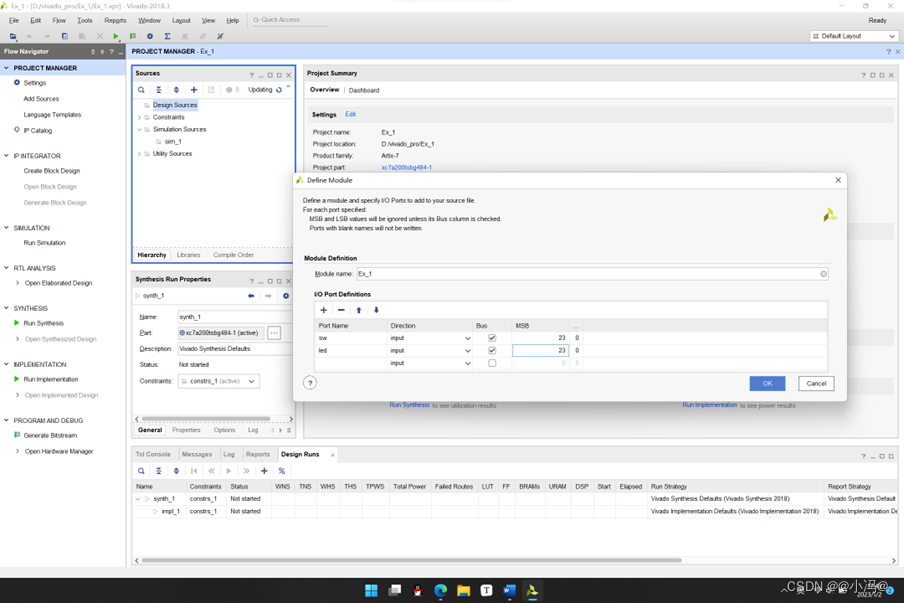

图 1-10 创建设计文件后的添加或创建设计文件对话框 图 1-11 Define Module 对话框

图 1-11 Define Module 对话框 - 这里就可以看到我们创建的文件已经出现在项目文件夹中了

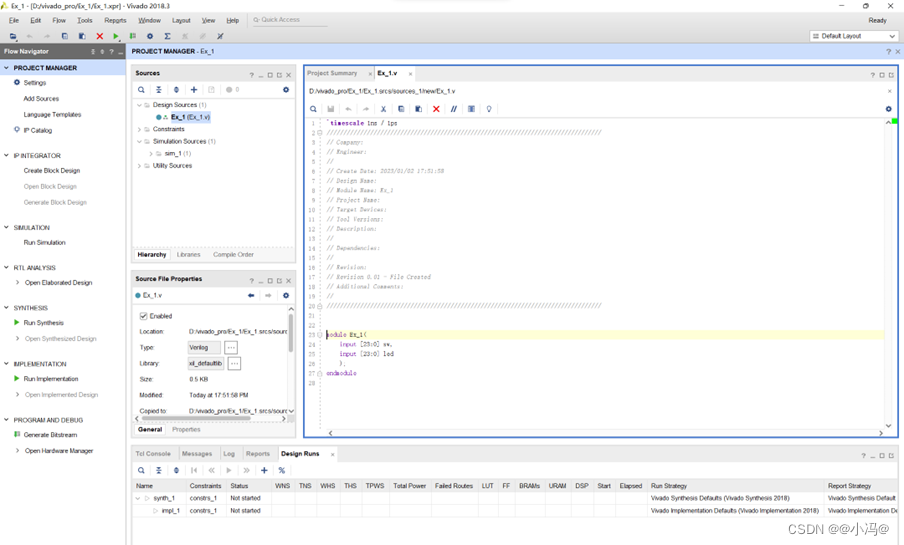

图 1-12 打开 Ex_1.v

图 1-12 打开 Ex_1.v - 双击文件打开并编辑以下内容

`timescale 1ns / 1ps

module Ex_1(

input [23:0] sw,

output [23:0] led

);

assign led = sw;

endmodule

图 1-13 编辑 Ex_1.v

1.3 仿真

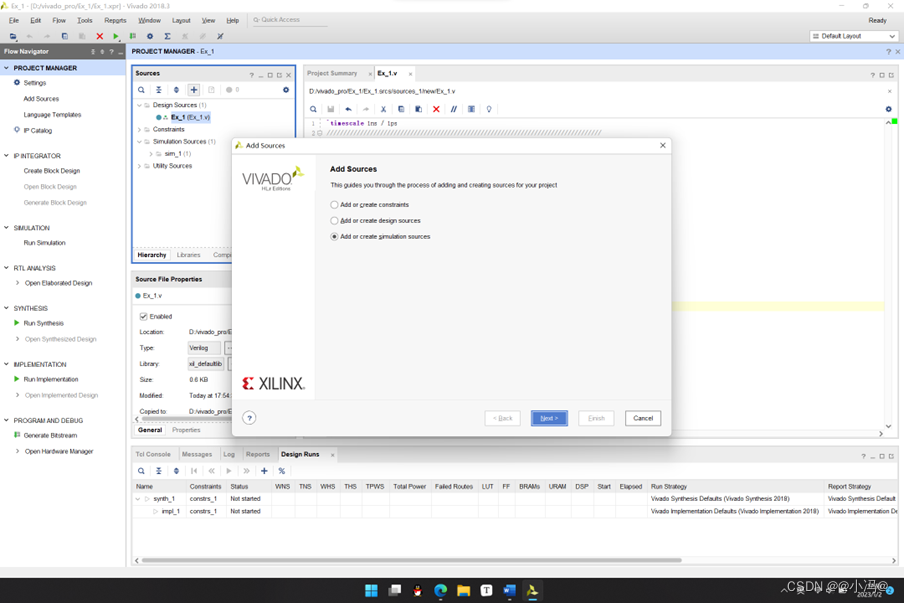

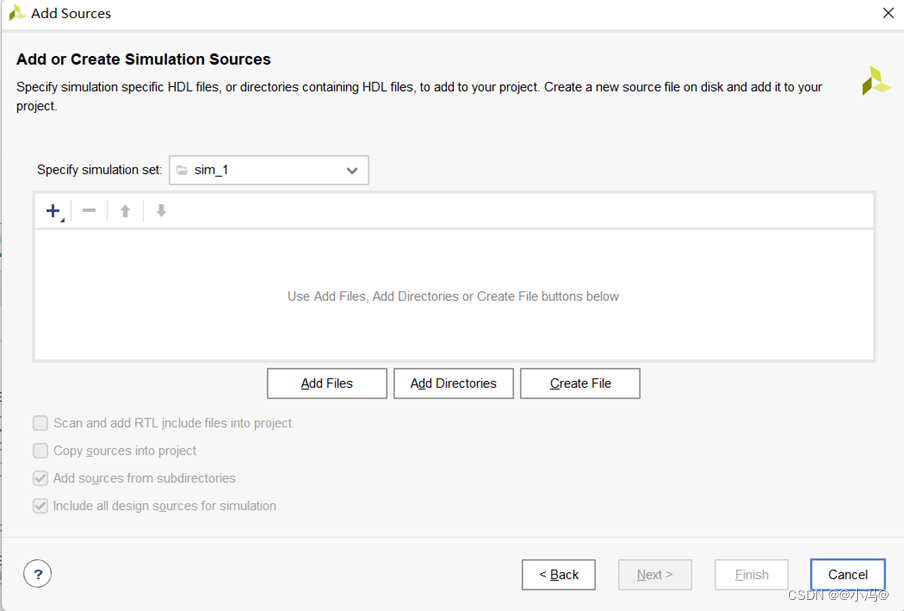

9. 点击Add sources。本次我们要添加仿真文件,因此本次我们选择simulation sources,再点击next 图 1-14 添加仿真源程序

图 1-14 添加仿真源程序

2. 创建一个名为Ex_1_sim的仿真文件

1-15 增加仿真源程序第二步-、Add Sources 对话框

1-15 增加仿真源程序第二步-、Add Sources 对话框

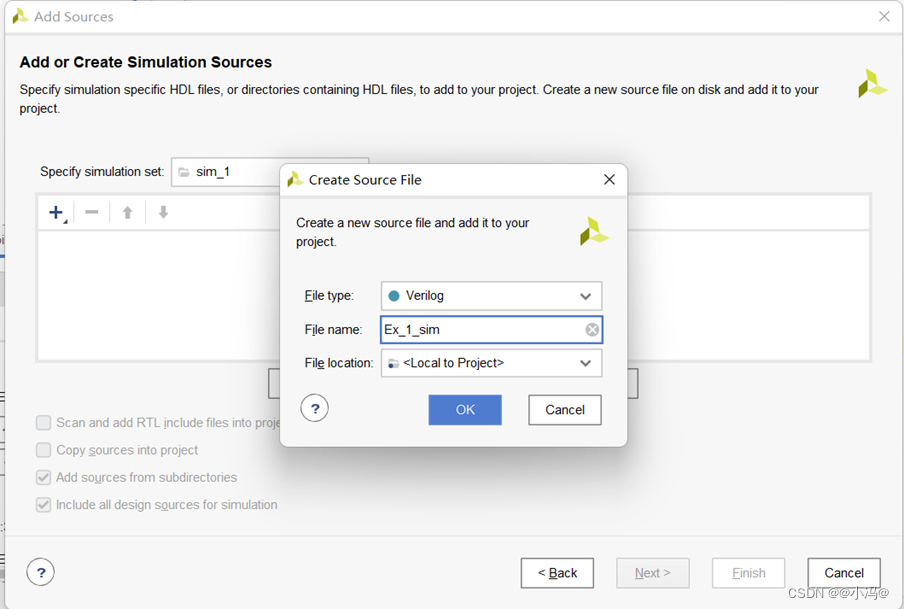

在创建文件的窗口如图 1-15 那样设置仿真源文件的文件名为 Ex_1_sim,并点击 OK。

图 1-16 设置仿真源文件文件名

图 1-16 设置仿真源文件文件名

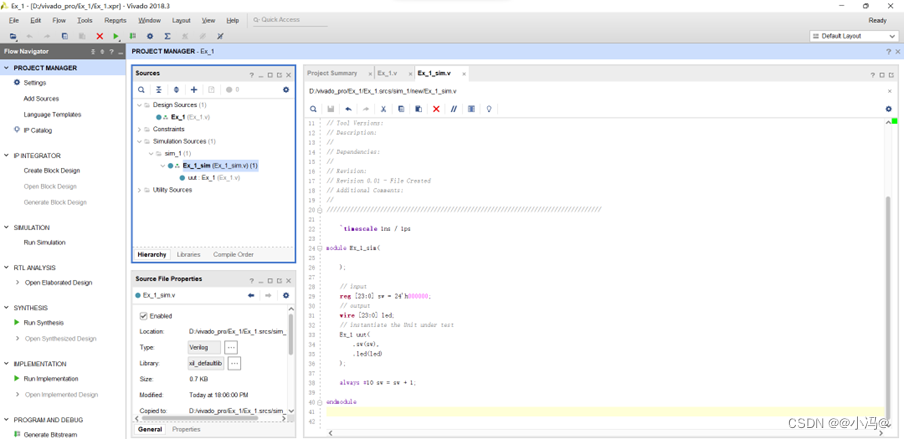

3. 编辑Ex_1_sim.v文件为如下内容:

`timescale 1ns / 1ps

module Ex_1_sim(

);

// input

reg [23:0] sw = 24'h000000;

// output

wire [23:0] led;

// instantiate the Unit under test

Ex_1 uut(

.sw(sw),

.led(led)

);

always #10 sw = sw + 1;

endmodule

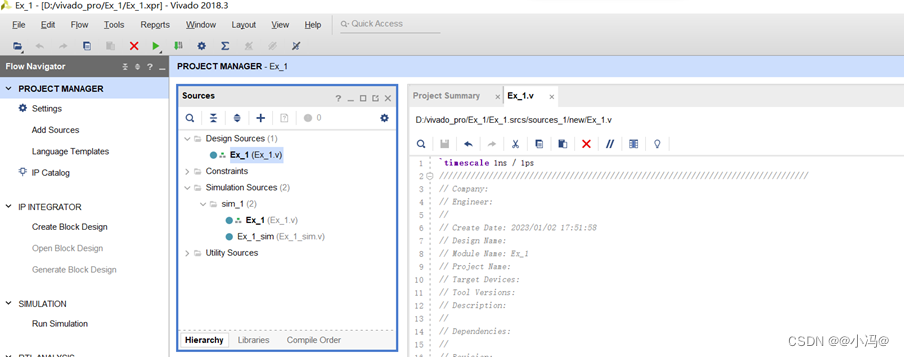

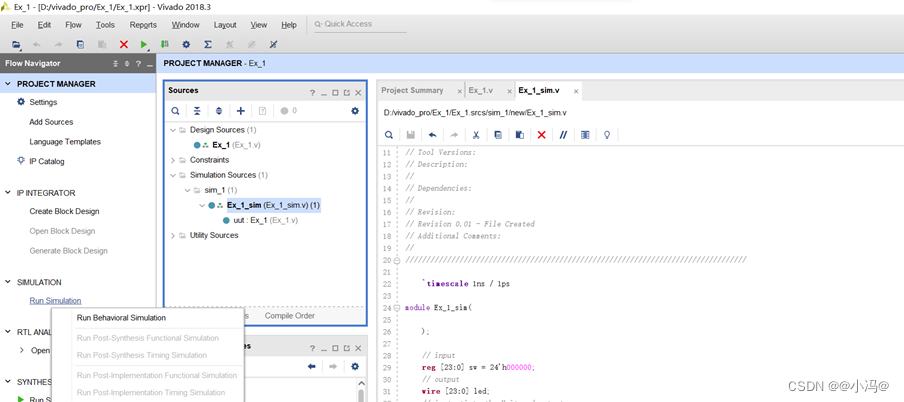

图 1-17 项目中的仿真源文件

图 1-17 项目中的仿真源文件

-

从这里可以看到我们的文件已经添加成功了

图 1-18 编辑完 Ex_1_sim.v 后的项目文件层次

图 1-18 编辑完 Ex_1_sim.v 后的项目文件层次 -

点击图示内容开始运行仿真

图 1-19 点击 Run Simulation

图 1-19 点击 Run Simulation

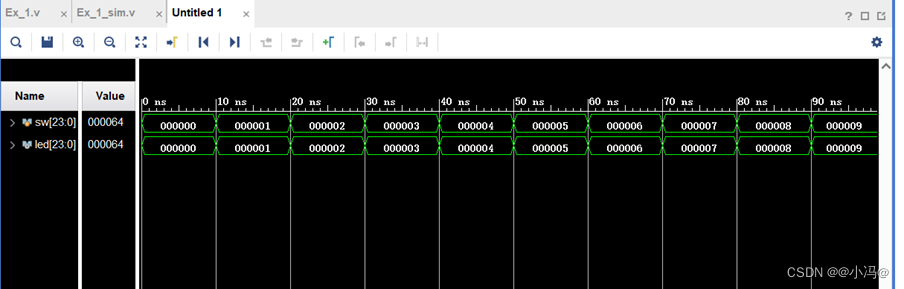

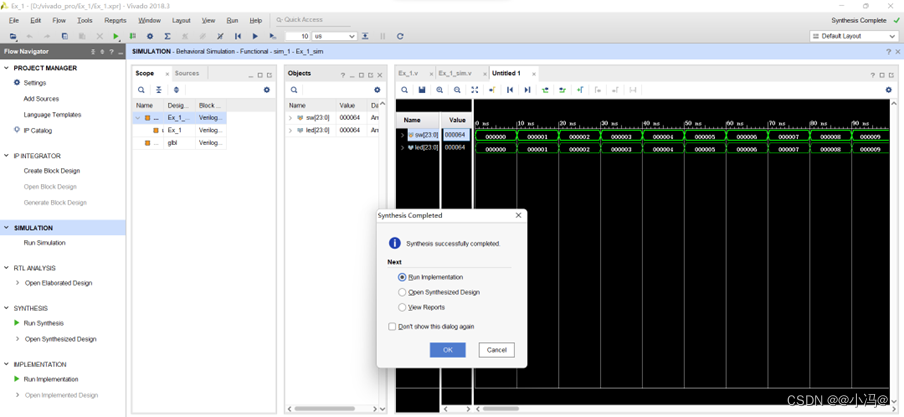

- 得到仿真波形图

图 1-20 仿真波形图

图 1-20 仿真波形图

从图上我们可以明显地看到,每隔 10n,输入数据 SW 加 1,输出数据 led 紧跟着变化

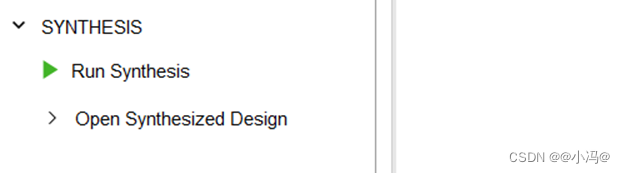

1.4 综合

- 按照下图的选项进行综合

图 1-21 Run Synthesis_1

图 1-21 Run Synthesis_1

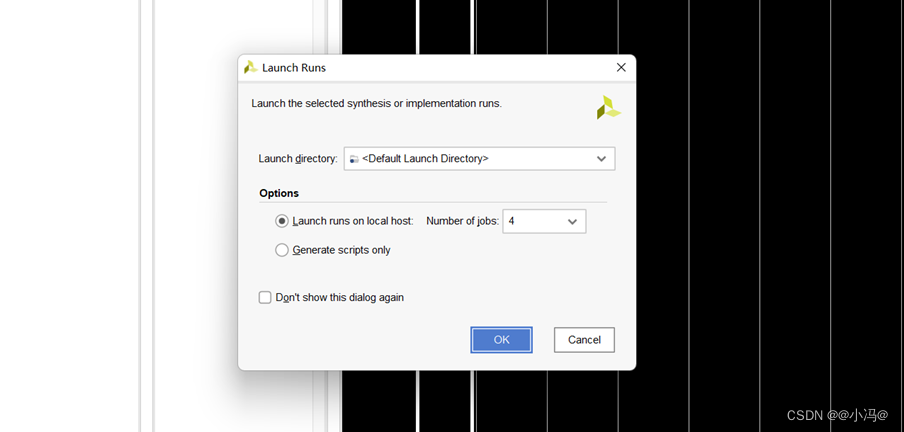

图 1-22 Run Synthesis_2

图 1-22 Run Synthesis_2 - 出现图示窗口表示综合已经完成

图 1-23 综合以后的窗口_1

图 1-23 综合以后的窗口_1

由于我们还没有进行管脚分配,所以按照图 1-23 的选择,点击 OK,对设计进行管脚分 配,如果已经管脚分配过了,那么图 1-23 中选择 Run Implementation 来运行实现。

图 1-24 综合以后的窗口_2

图 1-24 综合以后的窗口_2

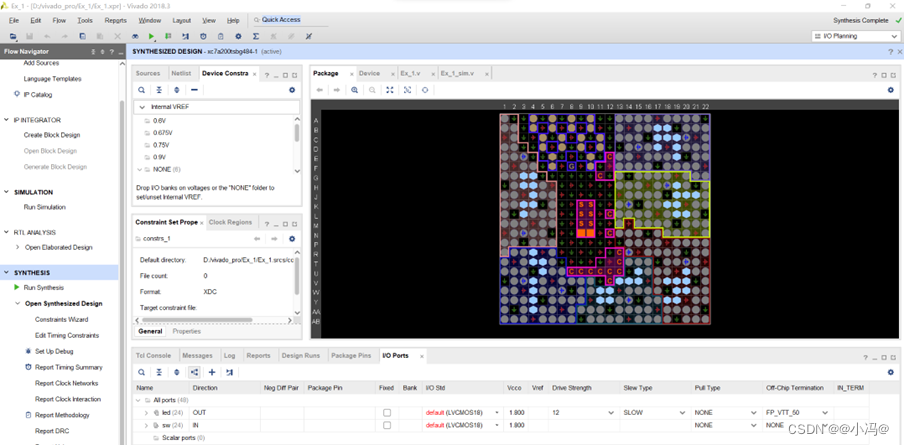

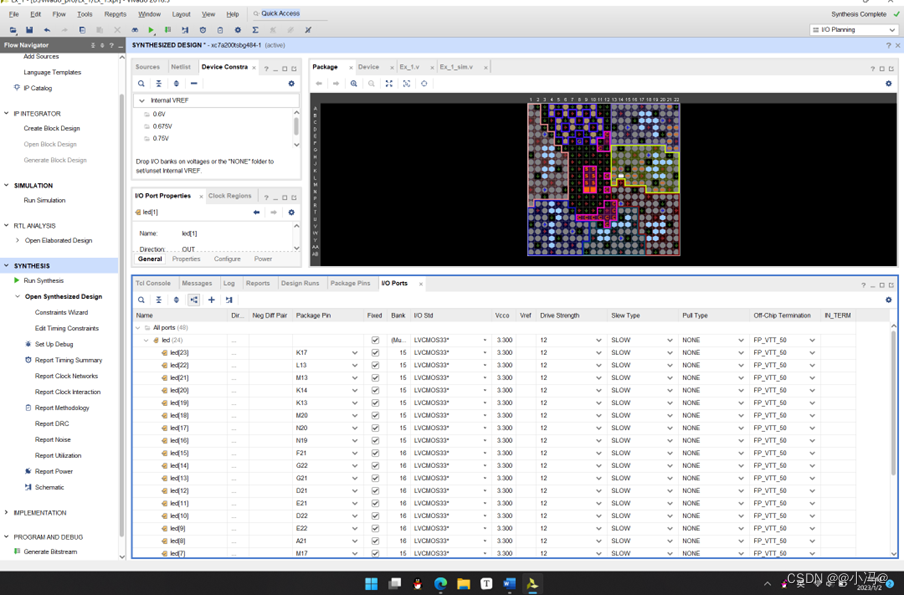

按照图 1-24 的选择,点击 OK 或在 Project Manager 中点击 Open Synthesized Design。有 一个滚动条说明进度。滚动条结束后,选择菜单 Layout->I/O Planning。出现如图 1-25 所示 的管脚分配表。

1.5. 管脚分配

按照图 1-24 的选择,点击 OK 或在 Project Manager 中点击 Open Synthesized Design。有 一个滚动条说明进度。滚动条结束后,选择菜单 Layout->I/O Planning。出现如图 1-25 所示 的管脚分配表。

图 1-25 管脚分配表

图 1-25 管脚分配表

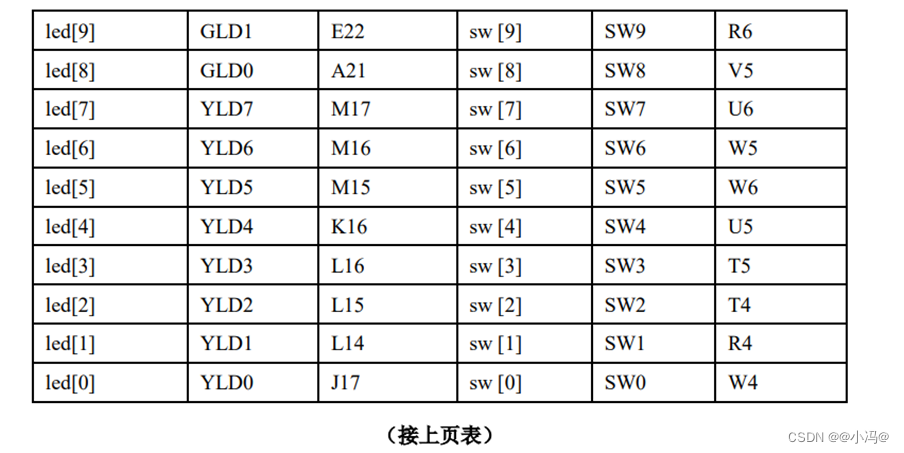

现将 I/O Std 这一列全部改成 LVCMOS33。然后根据表 2-1,点击 site 对每个管脚进行 分配。

管脚分配好后,如图 1-26 所示。

管脚分配好后,如图 1-26 所示。

图 1-26 管脚分配后

图 1-26 管脚分配后

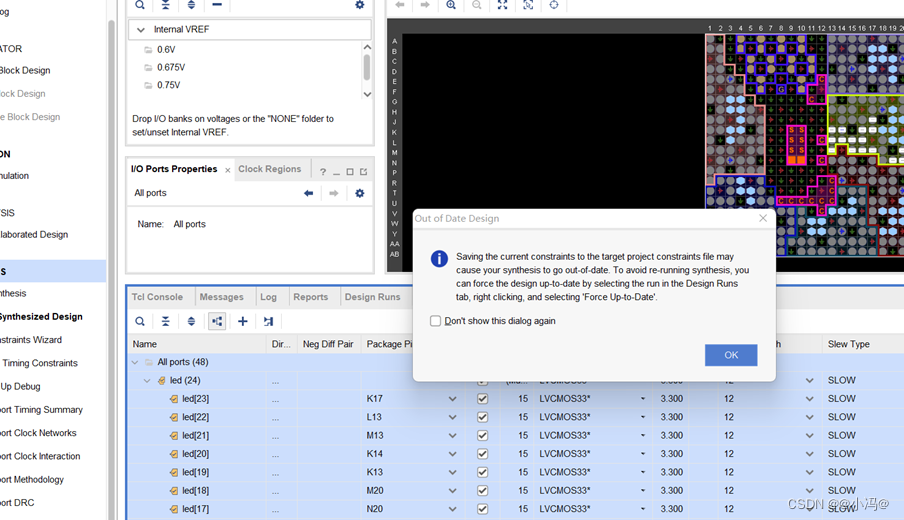

按 Ctrl+S,出现如图 1-27 所示的窗口,点击 OK。

图 1-27 保存管脚分配设置

图 1-27 保存管脚分配设置

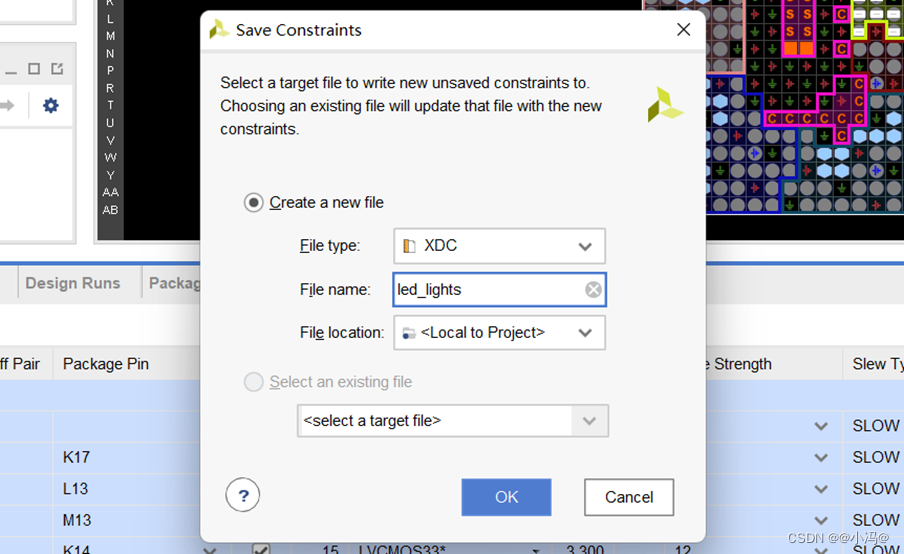

在出现的如图 1-28 所示的窗口中填写约束文件名为 led_lights

图 1-28 命名约束文件

图 1-28 命名约束文件

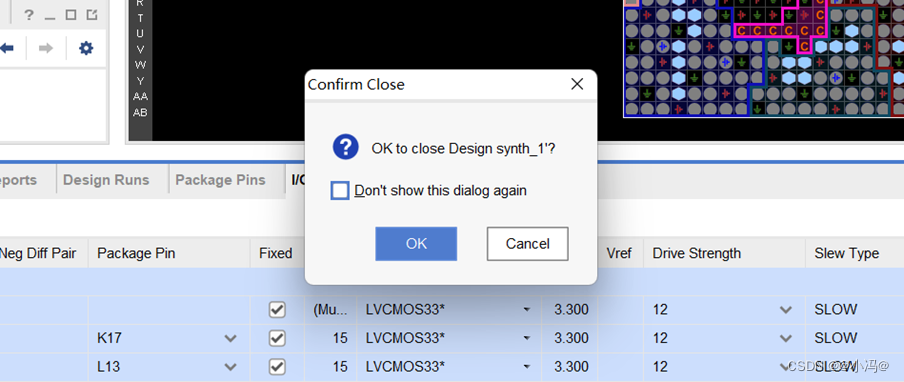

点击 OK。然后选择 File->Close Synthesized Design 关闭综合设计窗口。

图 1-29关闭综合设计窗口

图 1-29关闭综合设计窗口

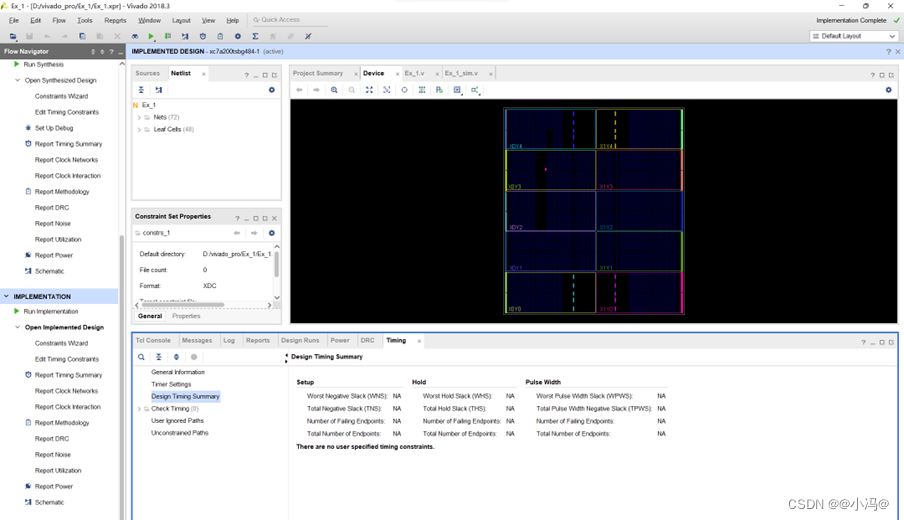

1.6.实现

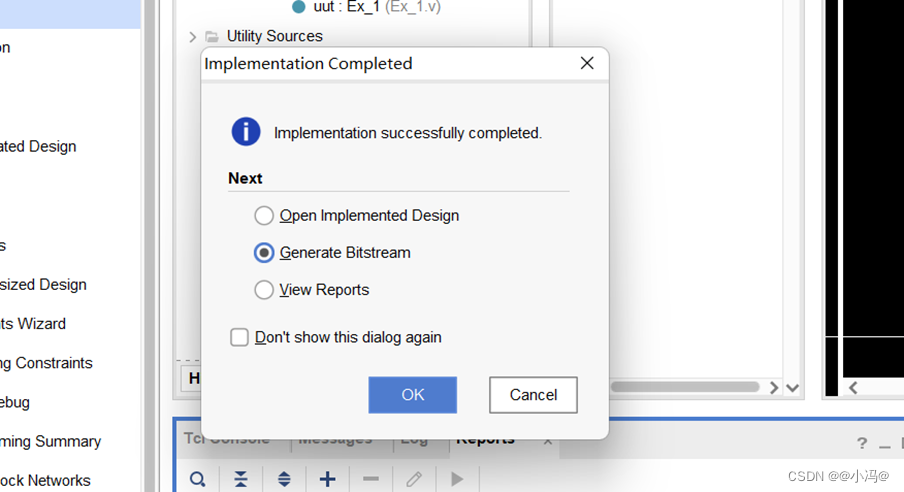

点击工具条中的 按钮或者在Project Manager中点击Run Implementation来对设计进 行实现。 实现完后出现图 1-30 的窗口。

图 1-30 实现后的窗口

图 1-30 实现后的窗口

1.7. 产生比特流文件并下载

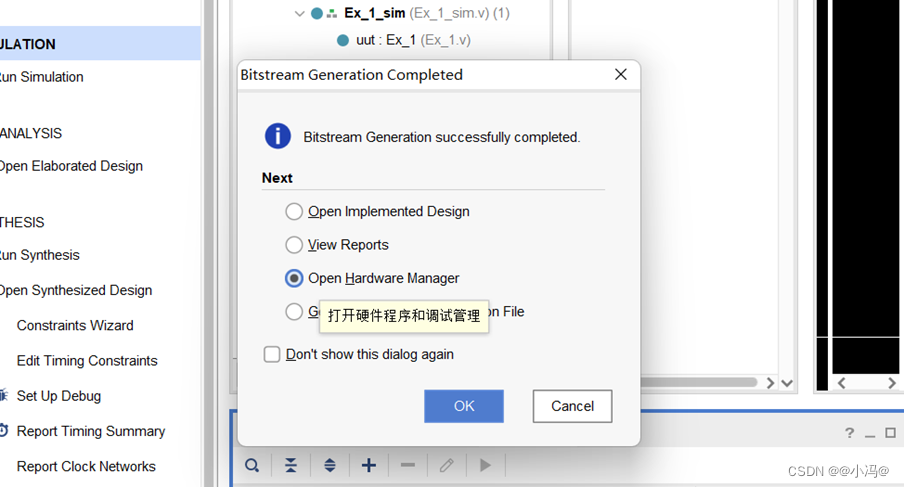

按照图 1-30 的设置点击 OK,或者在 Project Manager 中点击 Generate Bitstream 或者工 具条上的 按钮。比特流生成后会出现图 1-31 所示的对话框 图 1-31 比特流生成完成

图 1-31 比特流生成完成

用 USB 下载线将 Minisys 板的 PROG UART 与 PC 机的 USB 相连,打开 Minisys 板的 电源。按照图 1-31所示选中 Open Hardware Manager。点击 OK。(在 Project Manager 中点 击 Hardware Manager)。出现图 1-32 所示的界面。

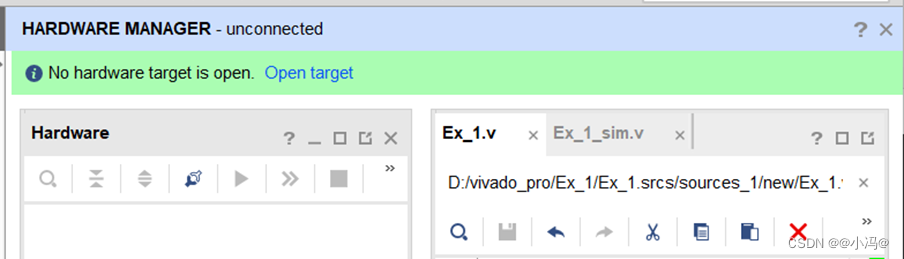

图 1-32 Hardware Manager

图 1-32 Hardware Manager

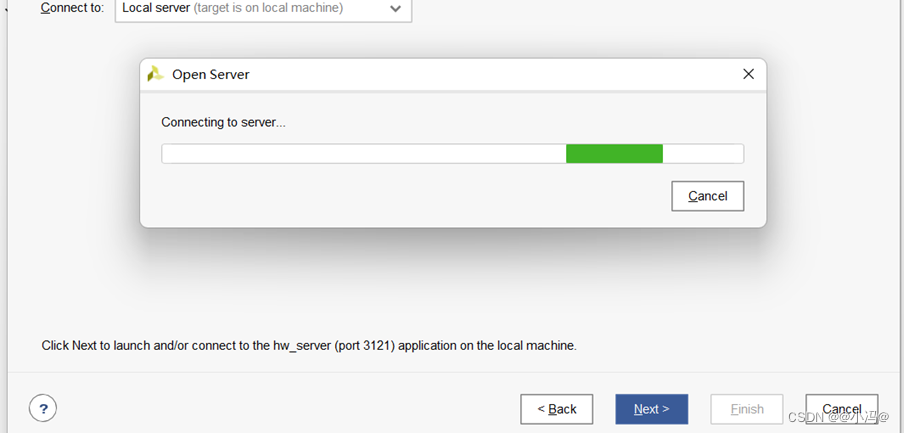

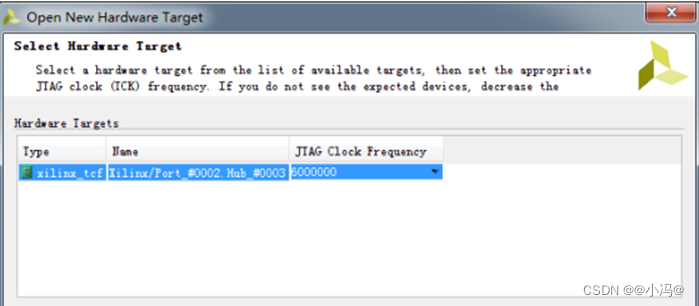

点击 Open target->Open new target。在弹出的窗口中点击 Next,再次点击 Next。此时出 现图 1-33 所示的滚动条。 图 1-33 寻找硬件

图 1-33 寻找硬件

硬件连接上后,会出现图 1-34 所示界面。

图 1-34 找到硬件

图 1-34 找到硬件

所列的正是我们接到 PC 上的板子的主芯片。点击 Next,然后点击 Finish。

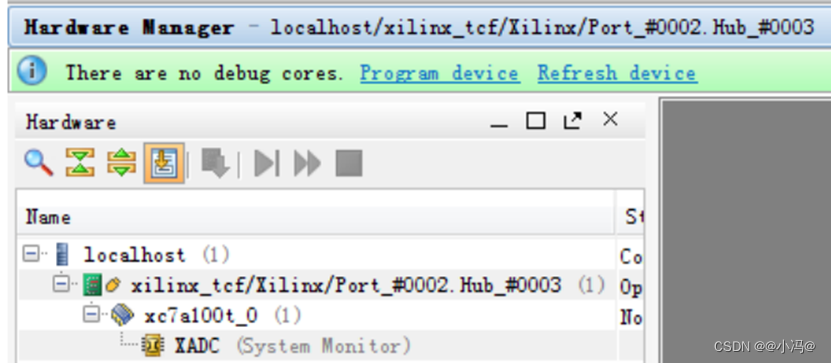

出现如图 1-35 所示界面。 图 1-35 连接上硬件后

图 1-35 连接上硬件后

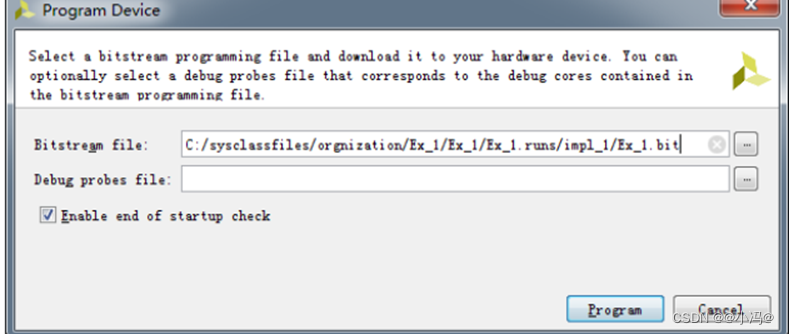

点击 Program devices->xc7a100t_0。出现的 Program Device 窗口(如图 1-36)中点击 Program 图 1-36 Program Device 窗口

图 1-36 Program Device 窗口

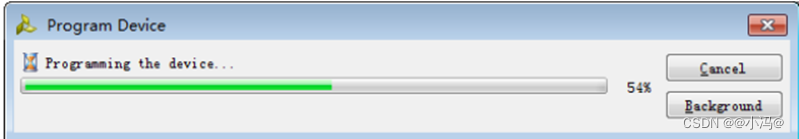

出现如图 1-37 所示的正在下载的进度条。

4509

4509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?