目录

二、【利用Excle表格】如何更加高效的创建原理图库封装(以FPGA为例)

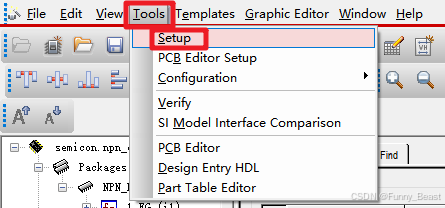

一、HDL添加原理图库

1.1 添加原理图库操作如下

先右击package,创建一个新的new

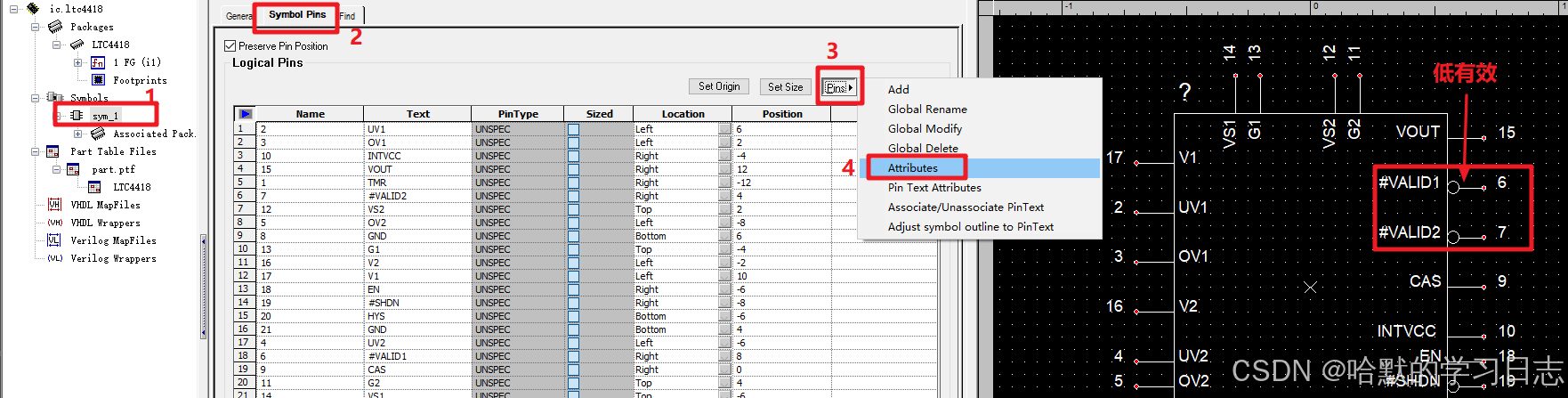

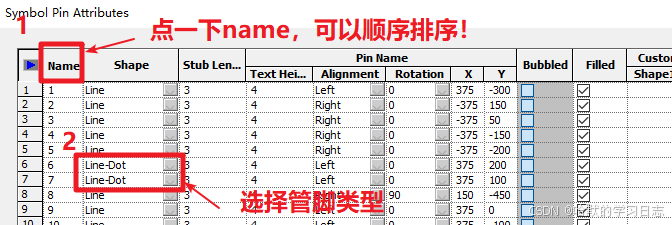

设置低电平有效标志Line-Dot

点击保存!结束!

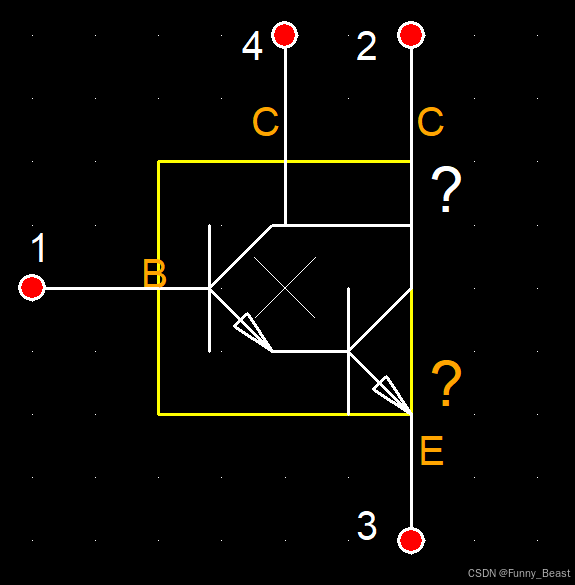

1.2 原理图标志图形绘制技巧:

eg:

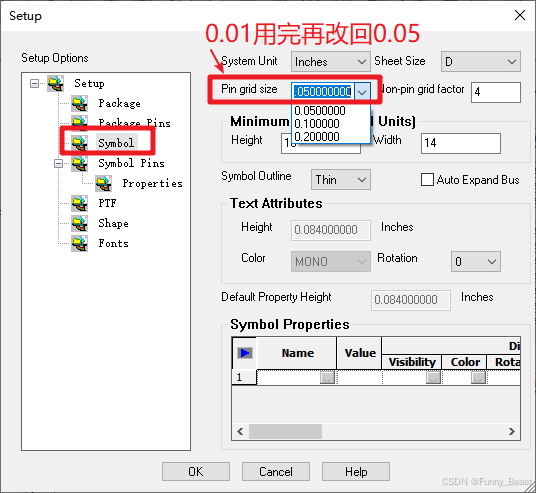

需要将栅格大小调小至0.01,绘制完小箭头等短线后,再将栅格调整为0.05即可。

1.3 引脚长度修改:

(以上)

2024.7.4 更新

1.4 器件原理图封装库创建时!

报错:Cell 'lmv321_1' : Pin(s) V-,V+ is (are) not present in any package or symbol. You can choose Pins - Add from the Package Pin page and delete these pins. If the HAS_FIXED_SIZE value has been reduced, reload the part.

背景:添加了隐藏引脚!!!直接在文件夹内copy封装库重新建的时候,发现只删除隐藏引,仍然会报错再删除

解决办法:没有删除干净!!!

应该在add里面也删除一次!!!!!

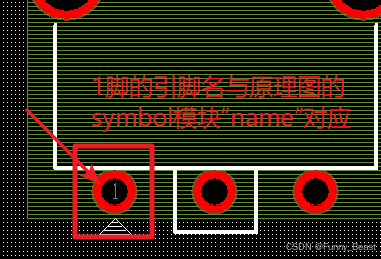

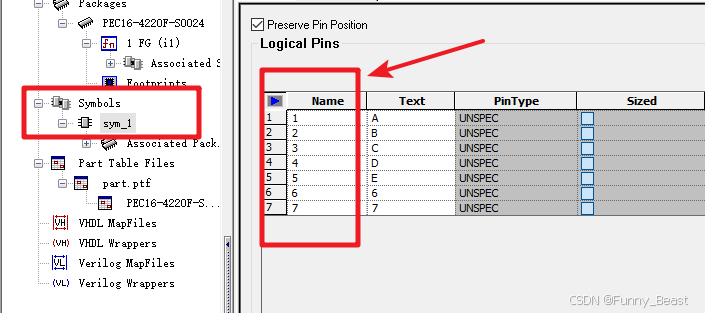

1.5 原理图与PCB器件symbol的对应关系

symbol的引脚:

原理图引脚:

二、【利用Excle表格】如何更加高效的创建原理图库封装

(以FPGA为例)

1. 先在PKG文档中找引脚文件(ASCII Pinout Files)!!!

2. 点击所选型号芯片,之后会跳出引脚网页,可以直接复制,并在excle中拷贝。

3. 拷贝后,通过“分列”进行分开为两列。

4. 再点击完成即可。

5. 如上图,拆分为两列。成功将引脚名拆开。

三、如何实现插入序号列,下来后自动填充?

【删除某一列后序号可自动改为连续!!!】

四、如何对分块后的引脚按类别拷贝,制作拆分模块?

1. 先选择所需列,再点击“筛选”,可实现只显示某一类引脚,从而进行复制粘贴。

2086

2086

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?