1、USB3.0 AC耦合电容

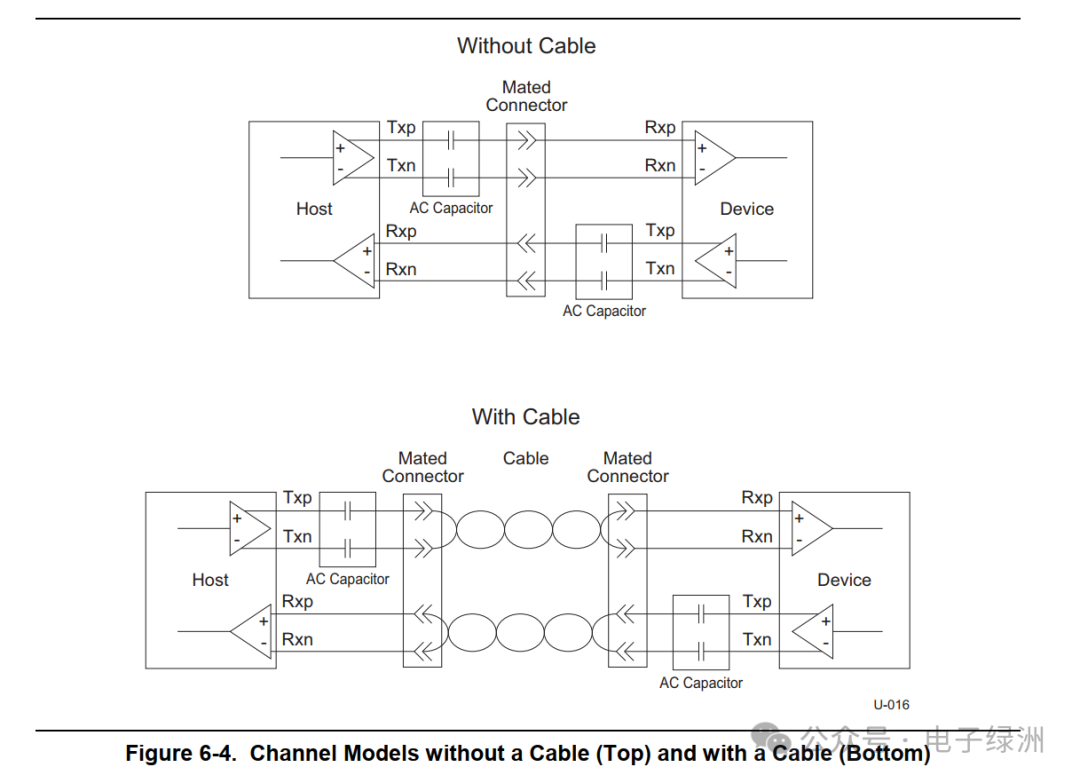

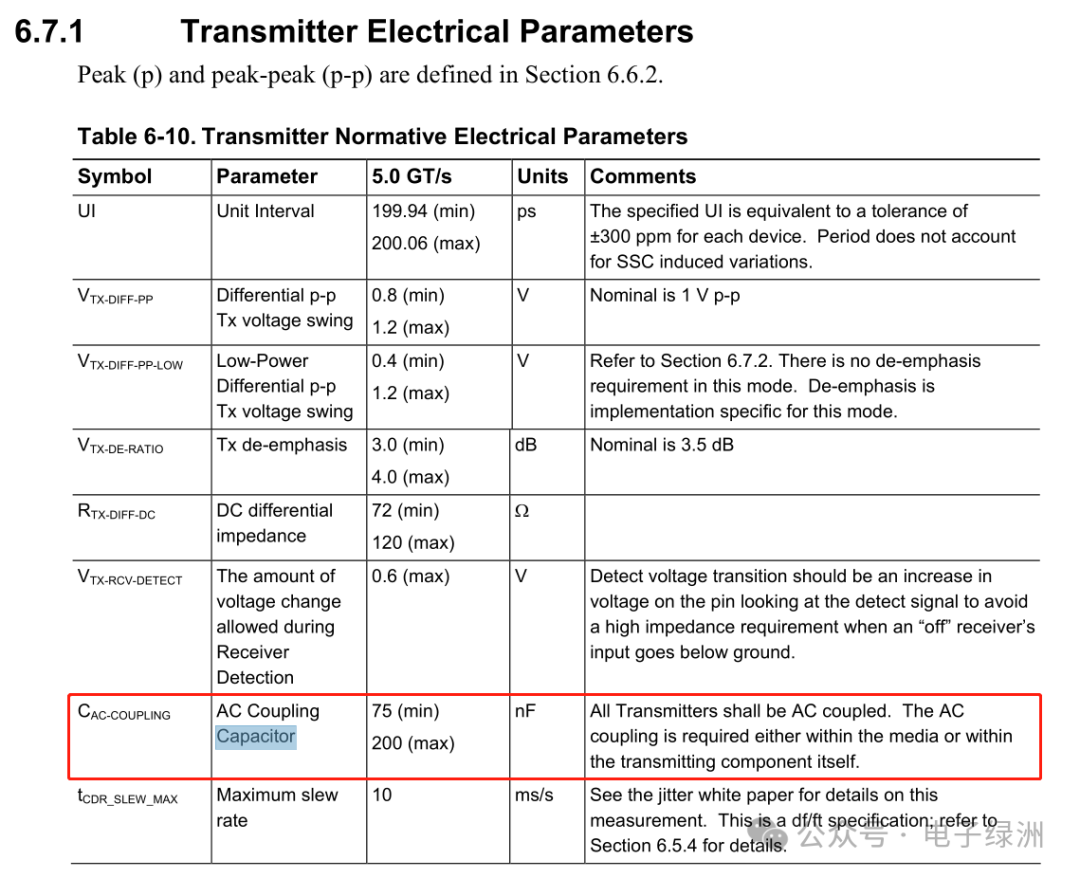

在《Universal Serial Bus 3.0 Specification,Revision 1.0》的标准中,规定在host的TX端要放置耦合电容(范围是75nF~200nF),在devices的TX端也放置耦合电容(范围是75nF~200nF),host和device的RX端都不需要放置电容。

而在USB3.0设计电路上,经常看到host的TX端放置100nF电容,而host端的RX放置的是0欧姆电阻(因为外设的USB设备,在其TX端一定会放置耦合电容的)。而在芯片与芯片之间的USB3.0的TX端和RX端都是要放置100nF电容的,在设计时很多人会忽略这一点。通常,电容放置位置优先参考开发板demo,或按协议规定,板级连接靠近座子,芯片之间连接靠近发送端。

AC耦合电容的作用:host端和device端的偏置直流电压值不一样,起到隔直流作用,也可以更好的预制共模噪声。

而USB2.0要兼容原来的USB1.0和USB1.1,正负线上有同时为高或为低的状态,不能用AC耦合。

选择的电容太大的话,电容端的电压稳定时间需要比较长,信号边沿会比较缓慢,眼图的眼高变小,信号衰减。

选择的电容太小的话,根据f=1/2ΠRC,影响信号本身传输。通带的最小频率要大于传输信号的最小频率。

由于耦合电容的存在,当码型为连续0或者1的时候,电容的损耗就很大(即频率低,阻抗大),导致幅度不断降低,最严重的后果就是无法识别到底是0还是1。因此,USB3.0的8b/10b编码,就是为了尽量把低频的码型优化成较高频率的码型,从而降低阻抗带来的损耗。

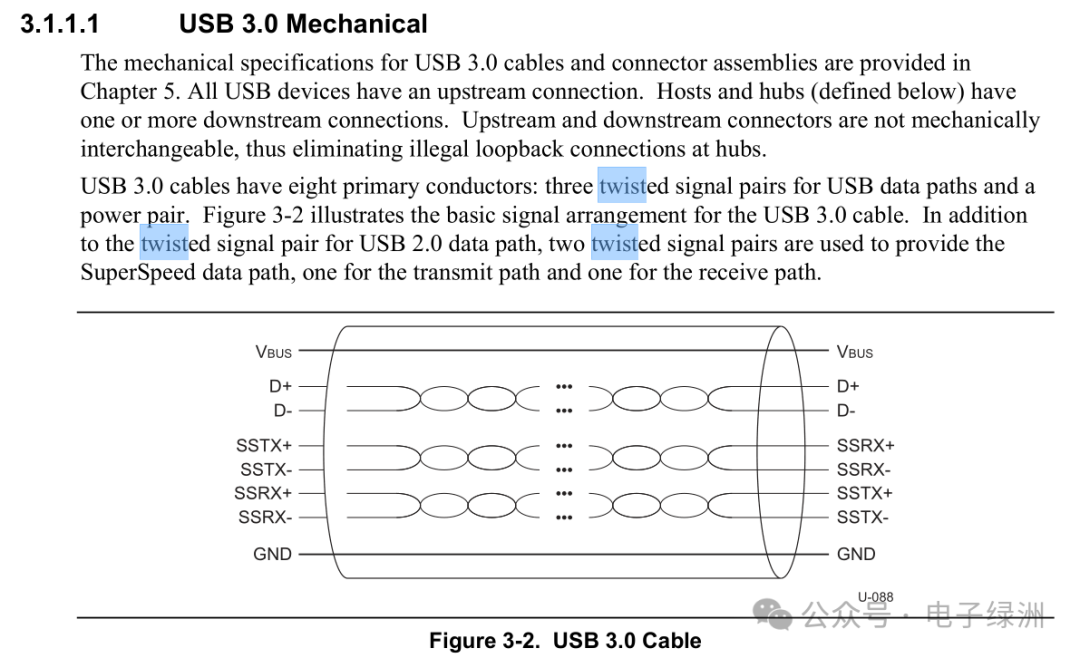

如下图是USB3.0标准协议的AC Capacitor框图,cable采用的是双绞线(抗干扰和防辐射效果好)。

2、USB3.0 Layout

-

由于在layout时,通常走线是0.1mm宽度左右,如果AC耦合电容的封装较大的话,如0603封装,长度1.6mm宽度0.8mm,比走线宽度大很多,根据Z=根号L/C,阻抗变低,引起阻抗不连续(有的layout会在焊盘下挖空,加大参考层之间的距离,提高阻抗,使之匹配)。因此,通常要选择小封装的,低ESR和ESL的,比如0201封装,尺寸长度0.6mm宽度0.3mm。

-

差分对要等长(时序要求);

-

信号线要由参考地(高速信号的回流还是从参考地回流);

3、USB3.0座子

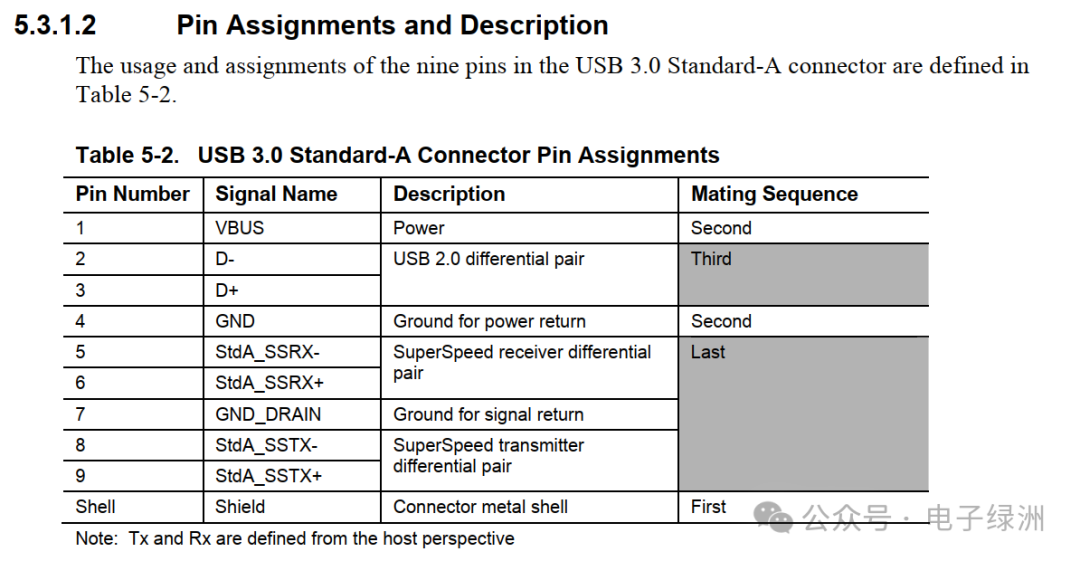

USB3.0中有八根信号线:Vbus,D+,D-,SSTX+,SSTX-,SSRX+,SSRX-,GND。

其中,D+和D-属于USB2.0信号,SSTX+,SSTX-,SSRX+,SSRX-属于USB3.0信号。

对于接口来说,USB2.0和USB3.0的PHY是独立的。

USB3.0 type-A的颜色规定是蓝色,且pin的尺寸是有差异的。

Mating Sequence:

1、host和外设的device是线屏蔽层接触;

2、Vbus和地接触;

3、USB2.0 DM DP接触;

4、USB3.0 SSRX和SSTX接触,实现热插拔。

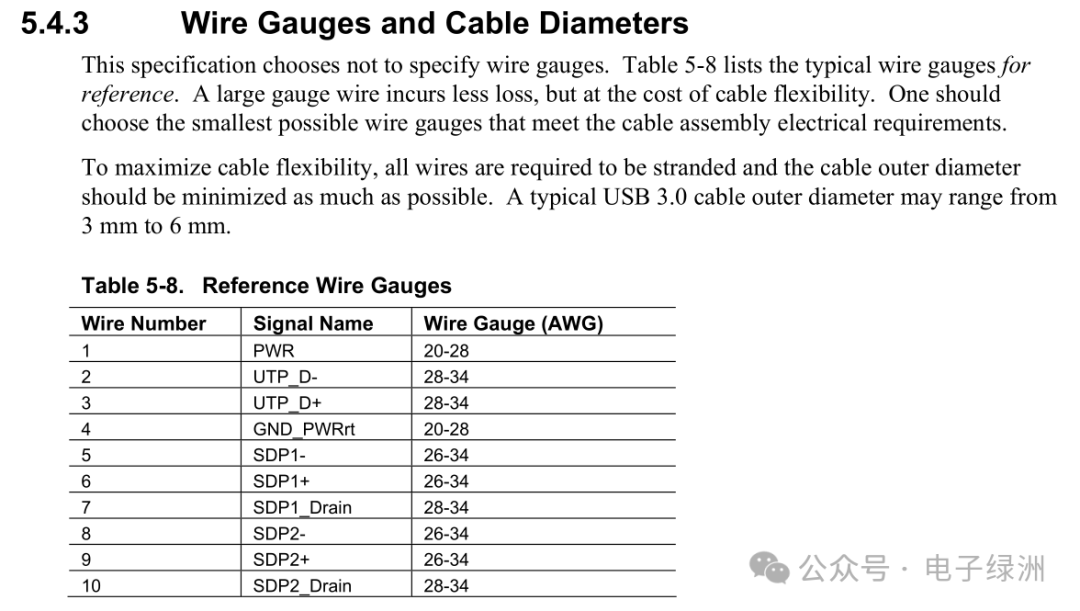

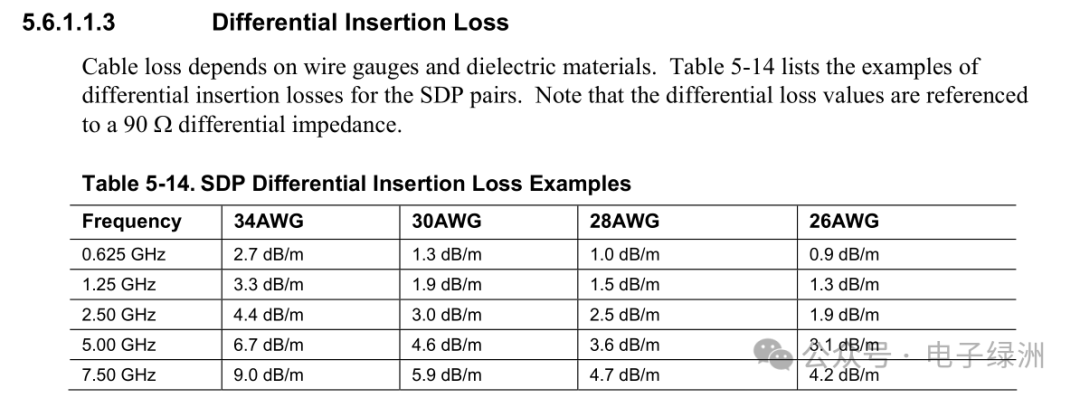

4、USB线材线径

USB3.0标准规范里也有对线材直径大小的说明,线径越小损耗越大。

对于低频来说,线径小,阻值大,损耗大。

对于高频来说,由于趋肤效应,电流倾向于在导体表面流动,线径小的横截面积也越小,交流电阻也增加,信号衰减也增加。

用USB接口供电涉及时,要注意产品的电流大小和使用的线材线径要匹配,避免线材上的压降比较大,导致板子上电压不足。

5、关于NRZI编码和8b/10b编码

NRZI编码:USB2.0采用的是NRZI编码,当数据为0时,电平翻转;数据为1时,电平不翻转。所以,当数据为连续的0时,数据会是一个不停翻转的波形,电压呈交流形式。而当原数据连续为1时,会呈现短暂的直流形式,即会出现一段时间电平不再变化。

对于上面的连续的电平不再变化,NRZI编码给的的解决方案是当原始数据中出现连续的7个1时,强行插入一个原始数据0,实现编码后的电来翻转,减少发送端与收入端的时钟误差而导致数据的接收错误。

8b/10b编码(USB3.0编码):将串行的数据以8bit为一个单位进行编码处理得到一个10bit的数据,具体怎么操作呢,假设原始8位数据从高到低用HGFEDCBA表示,将8位数据分成高3位HGF和低5位EDCBA两个子组。经过5B/6B编码,将低5位EDCBA映射成abcdei;高3位经过3B/4B编码,映射成fghj,最后合成abcdeifghj发送。因此,保证DC平衡(直流平衡)。

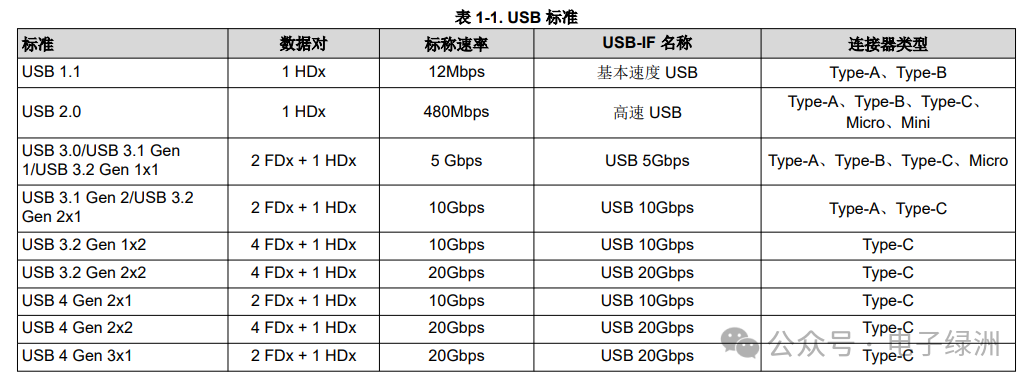

6、ESD寄生电容要求

USB1.0/1.1:信号速率12Mbps,电容要求20pF以下;

USB2.0:信号速率480Mbps,电容要求4pF以下;

USB3.0,USB3.1 Gen1,USB3.2 Gen 1x1:信号速率5Gbps,电容要求0.5pF以下;

USB3.1 Gen2,USB3.2 Genx1,USB3.2 Gen 1x2,USB4 Gen 2x1:信号速率10Gbps,电容要求0.3pF以下;

USB4 Gen 3x1:信号速率20Gbps,电容要求0.25pF以下;

参考文献:

TI《用于USB接口的ESD和浪涌保护》

https://www.ti.com.cn/cn/lit/an/zhcabr8b/zhcabr8b.pdf?ts=1732486096996

TI公司《高速信号的电容要求》

https://www.ti.com.cn/cn/lit/an/zhcad11a/zhcad11a.pdf?ts=1732431665897

——END——

丛林社会,从来不相信眼泪;再多的抱怨也没有用,不会有人可怜的

推荐阅读

2726

2726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?