视频链接

USB 3.0电路设计(视频类)

- USB 3.0基本介绍

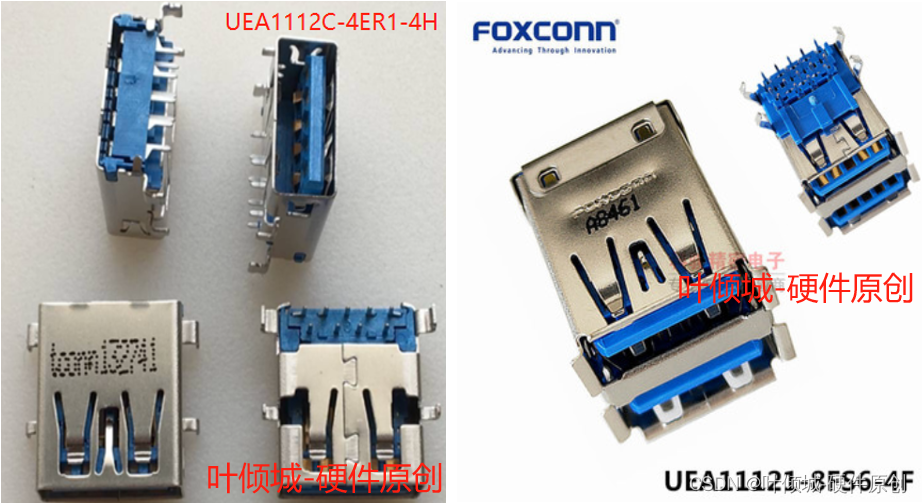

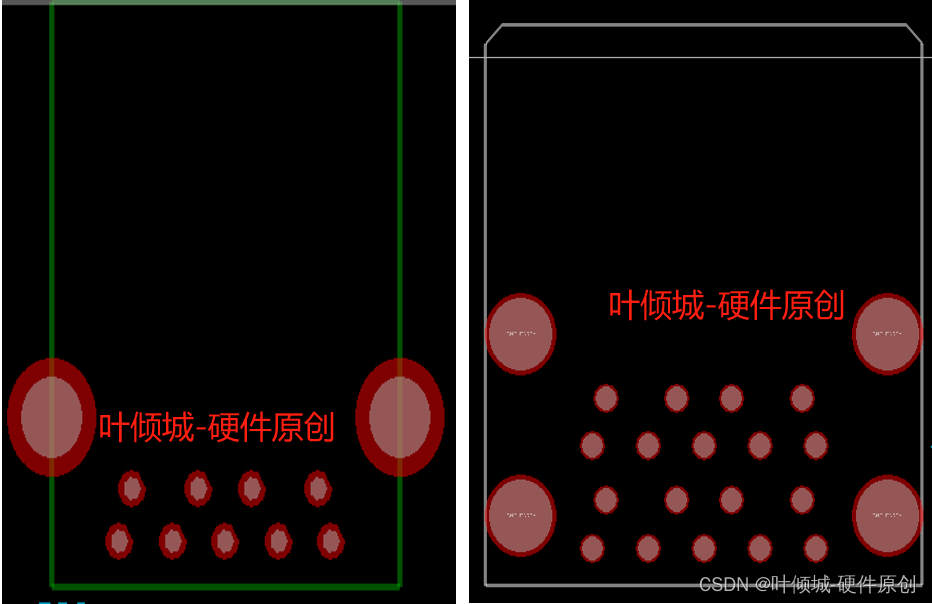

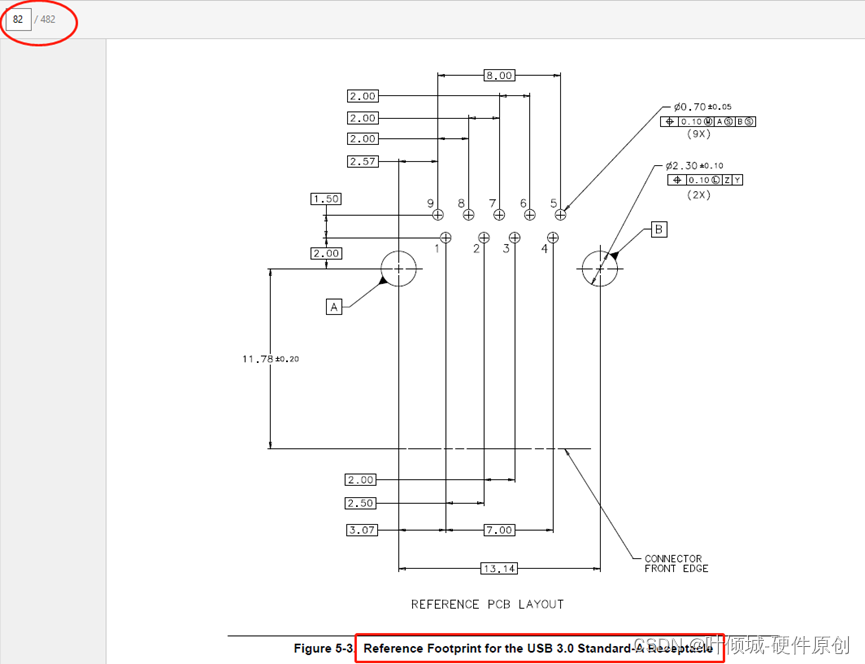

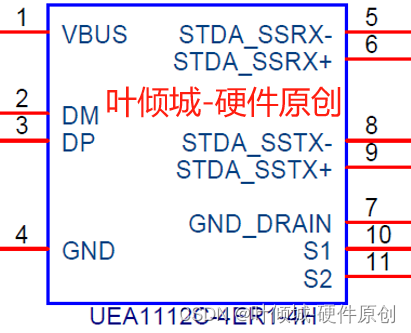

《USB 3.0 specification》 P82 USB 3.0 Standard-A Receptacle

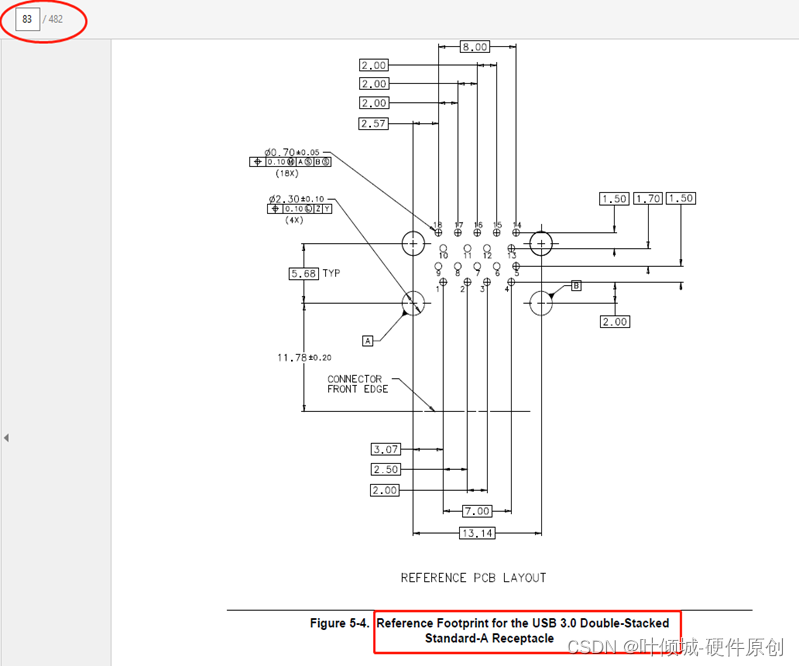

《USB 3.0 specification》 P83 USB 3.0 Double Standard-A Receptacle

USB 3.0 type-A管脚定义

| 引脚 | A管脚定义 | 线缆颜色 | 描述 |

| 1 | VBUS | 红色 | 5V供电 |

| 2 | D- | 白色 | 2.0数据差分对 |

| 3 | D+ | 绿色 | |

| 4 | GND | 黑色 | 电源地 |

| 5 | StdA_SSRX- | 蓝色 | 3.0高速数据差分对 |

| 6 | StdA_SSRX+ | 黄色 | |

| 7 | GND_DRAIN | N/A | 信号地 用于降低噪声干扰 |

| 8 | StdA_SSTX- | 紫色 | 3.0高速数据差分对 |

| 9 | StdA_SSTX+ | 橙色 |

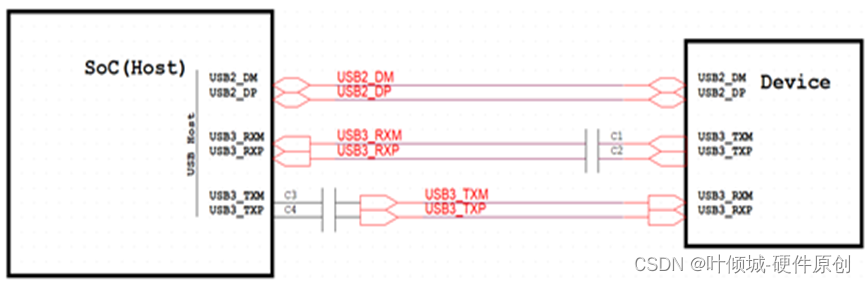

USB3.0相比2.0在硬件物理连接上有较大的改变,采用的是RX/TX全双工链路设计,由2对差分信号组成,同时向下兼容USB2.0,所以整个接口有3对差分信号,分别为USB3_RXM/USB3_RXP,USB3_TXM/USB3_TXP,USB2_DM/USB2_DP,USB3.0的传输速率可达到5Gbps。

下图为USB3.0的Data数据连接原理图,从电路上可以看是USB2.0为半双工,数据收发在一对差分信号上传输。

USB3.0为全双工,收发信号为独立的传输路径;其次,由于Sink端的直流偏置电压和source端的直流偏置电压不一样,故要需要串入AC耦合电容,电容一般取100nF,一般靠近驱动端放置,电容在设计上要求ESR ESL(特别重要)尽量小。

USB 3.0的Host的RX连接到Device Tx,Host的Tx连接到Device的Rx,类似于我们常用的UART接口的连接。

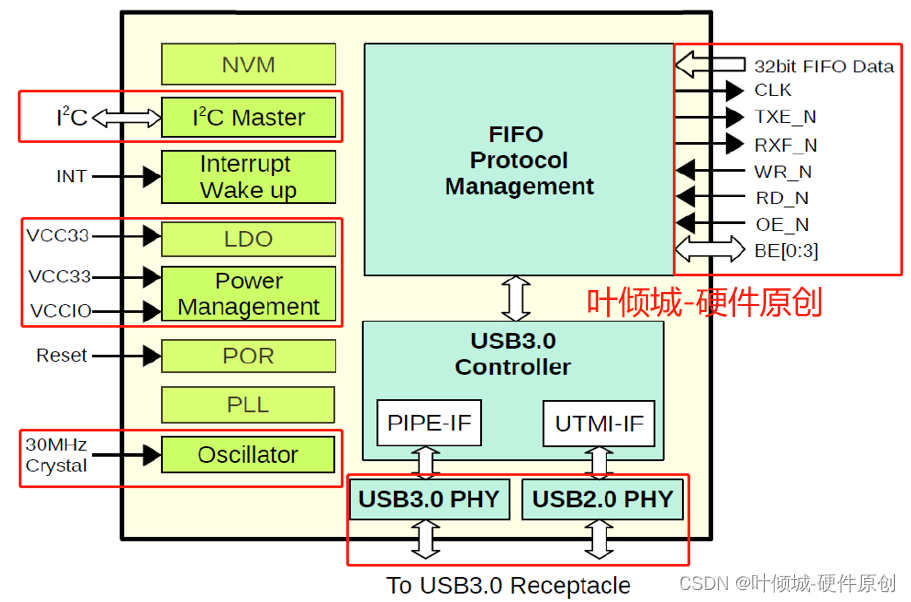

2、USB 3.0 视频类(UVC-以FT602Q为例)

2.1、结构框图

2.2、信号定义

2.1、电源管脚

对于电源电压,系统要求。

| 管脚符号 | 类型 | 描述 |

| VCC33 | PWR | +3.3V power input for chip and internal LDO. |

| DV10 | O | +1.0V power output from internal LDO. Connecting to VD10 and AVDD, with a 4.7uF cap to ground is recommended. |

| VD10 | PWR | +1.0V core voltage input. |

| VCCIO | PWR | Power input for I/O block, supports +2.5/+3.3V |

| VDDA | PWR | +3.3V power input for USB2.0 and USB3.0 PHYs. |

| AVDD | PWR | +1.0V power input for PLL. |

| GND | GND | Ground |

2.2、USB管脚

| 管脚 | 类型 | 描述 |

| DP | I/O | High-speed USB differential transceiver (positive) |

| DM | I/O | High-speed USB differential transceiver (negative) |

| TODN | O | Super Speed USB transmitter differential pair (negative) |

| TODP | O | Super Speed USB transmitter differential pair (positive) |

| RIDN | I | Super Speed USB receiver differential pair (negative) |

| RIDP | I | Super Speed USB receiver differential pair (positive) |

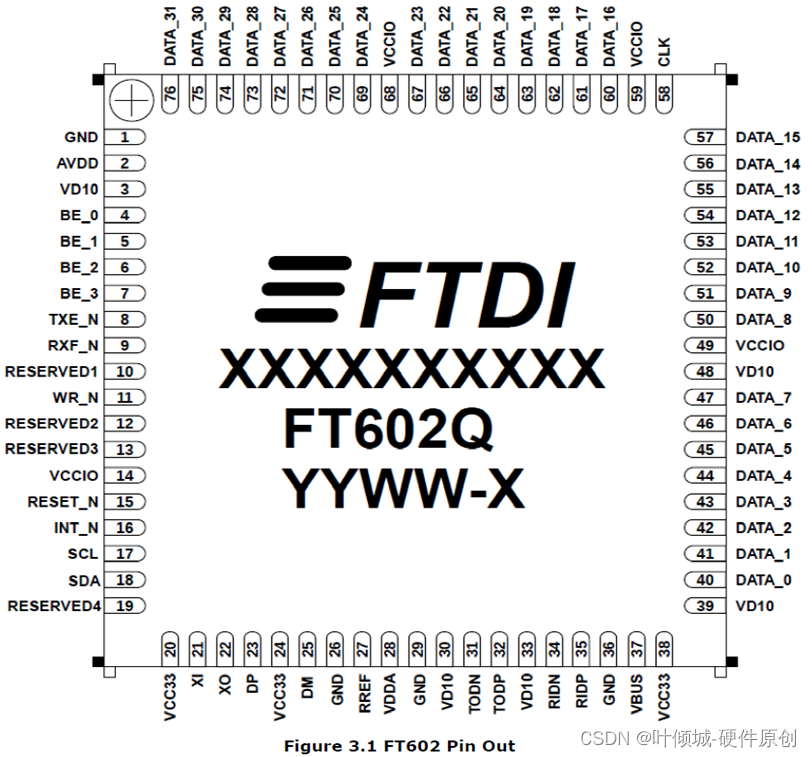

2.3、其他管脚

| 管脚 | 类型 | 描述 |

| RREF | I | PHY reference resistor input pin. Connect 1.6K Ω 1% resistor to ground, provides reference voltage to USB2 PHY. |

| XI | I | Crystal input. |

| XO | O | Crystal Output. |

| VBUS | I | USB BUS power detect pin. The input voltage should be greater than 2.7V. |

| CLK | O | Parallel FIFO bus clock output pin to FIFO bus master, the Frequency can be configured as 66Mhz or 100Mhz for both FIFO bus modes. |

| TXE_N | O | 245 Synchronous FIFO mode: Transmit FIFO Empty output signal. The signal indicates there is a minimum of 1 byte of space available to write to. Only write to the FIFO when the signal is logic 0. Multi-Channel FIFO mode: Status Valid output signal (optional). |

| RXF_N | O | 245 Synchronous FIFO mode: Add external pull up in normal operation. Multi-Channel FIFO mode: Data Receive Acknowledge output signal. |

| WR_N | I | 245 Synchronous FIFO mode: Write Enable input signal. Multi-Channel FIFO mode: Data Transaction Request input signal. The signal is active low. |

| RESERVED1 | I | (10pin) Reserved. Add external pull up in normal operation. |

| RESERVED2 | I | (12pin) Add external pull up in normal operation. |

| RESERVED3 | I | (13pin) Add external pull up in normal operation. |

| RESERVED4 | NC | (19pin) Do not connect. |

| RESET_N | I | Chip Reset input, Active low. |

| INT_N | I | Interrupt input pin, active low.(中断) |

| SCL | OD | I2C Serial Clock line |

| SDA | OD | I2C Serial Data line |

| BE_[0:3] | I/O | Parallel FIFO bus byte enable I/O bit X. |

| DATA_[0:7] | I | Parallel FIFO bus data input bit X. |

| DATA_[8:15] | I/O | Parallel FIFO bus data I/O bit X. |

| DATA_[16:31] | I | Parallel FIFO bus data input bit X. |

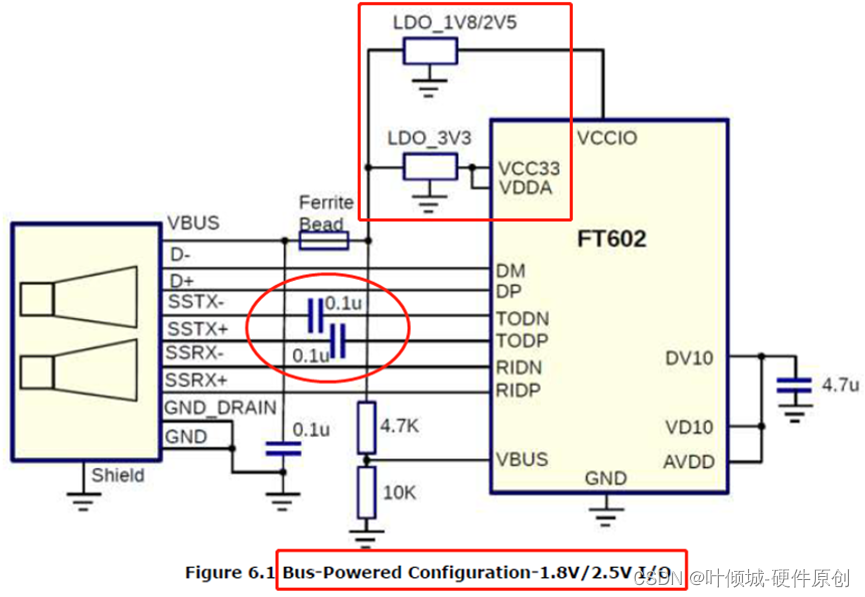

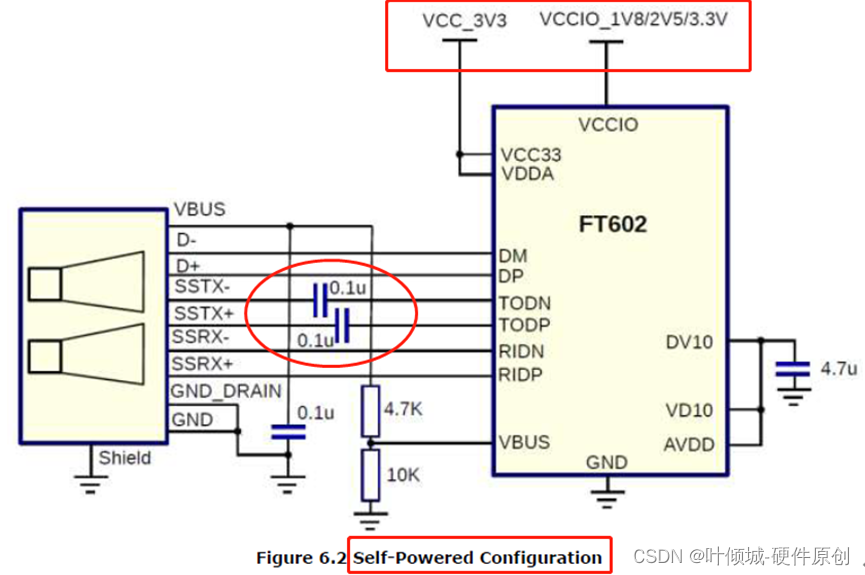

2.3、BUS供电和自供电

2.3.1、BUS供电

2.3.2、self供电

2.4、硬件实战

2.4.1、FT602 Connect to FIFO Master Interface

1、Multi-Channel FIFO Mode

2、245 Synchronous FIFO Mode

注:I2C总线可以连接到其他I2C从设备。

2.4.2、FT602硬件实战

2.5、FT602Q硬件实战注意点

1、host端的TX处加上AC耦合电容,PCB布局的尤其要注意!

2、注意VCCIO的电平问题

3、其余标注颜色的重点

3、USB3.0 XCZU28DR-2FFVG1517E 硬件实战

4、USB3.0 硬件设计要点

5、USB3.0 layout设计要点

PCB走线要求:5Gbps的速率需要以高速线的设计规则来严格把关走线,充分考虑PCB的设计细节。

4.1 PCB出线要求尽可能平等出线。

4.2 走线换层需要在信号过孔旁边增加地过孔,用于信号的回流。

4.3 USB信号测试点的放置建议如下图,“一”字形放置在路径上,非Y字形或T字形放置,并且测试焊盘如果走线不连续的较大焊盘,请将相邻层的GND层垂直于测试焊盘掏空,避免出现影响信号的寄生电容或等效电容。测试点的焊盘尺寸,应尽可能的小,如果必需要放置测试点的话,比照0402封装的焊盘尺寸或直接将测试点放置在信号线的过孔上。

4.4 关于等长匹配蛇形线的走线方式,建议按下图方式走线

4.5 阻抗:90Ω±10%。

4.6按高速规范设计,伴地孔、过孔隔离、圆弧、Stub最短等原则布线。

4.7保持有完整的参考平面,确保阻抗的连续性。

本文详细介绍了USB3.0的电路设计,包括接口的物理连接变化、全双工特性、电源和信号定义,以及针对FT602Q和XCZU28DR-2FFVG1517E的硬件实战和设计要点,强调了高速PCB走线和阻抗控制的重要性。

本文详细介绍了USB3.0的电路设计,包括接口的物理连接变化、全双工特性、电源和信号定义,以及针对FT602Q和XCZU28DR-2FFVG1517E的硬件实战和设计要点,强调了高速PCB走线和阻抗控制的重要性。

418

418

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?