PCIE耦合电容位置

以下为引用内容,为记录而做的本篇文章:

1、PCIe标准里面明确规定:当两个设备通过连接器互联时,必须放置交流耦合电容到TX端;

2、放远放近最大的不同时高速信号传输中的介质损耗和趋肤效应不同,当放置靠近rx端时,介质损耗和趋肤效应产生的衰减较大,因此,电容引发的阻抗不连续反射效应降低,可以通过高速互联模型推导出,在靠近rx端的1/4处是比较理想的,实测也是如此;但是当距离不远时,区别不是特别大,因此,pcie标准中,对于板级的电容放置并没有要求。

3、当加入连接器时,串扰和寄生电容/电感增加,互联线上损耗增多,其损耗减小了低频分量信号幅度,对于高频虽有减小但是减小幅度倍数没有低频多,如果放置在rx端,低频信号就衰减的太多了,但是,并不是不行;实测信号,也会发现放置在tx端时信号完整性更好一些(相对而言),而放置在rx端,如果距离长,信号整体衰减的比较厉害;

4、为了完善高速信号的可靠性,pcie在发送端加入了去加重技术,这进一步衰减了低频信号,如果再将电容放置远端,那么低频信号就是“雪上加霜”了;但是,也并不是不行;因此,有些设计里面,在tx和rx端都加电容,根据实际效果选择使用。同时都用的也存在,但是不建议这种用法,效果比较差!

综上:因为:连接器带来的信号干扰+去加重技术,导致低频信号幅度加剧衰减,没有和高频信号幅值同等衰减,信号整体“形状”发生畸变了,在这种情况下,要适当的调整低频信号衰减,因此,放置在tx端是非常必要的!但是这种做法加剧了容抗不连续反射的影响,因此,信号比起没有使用连接器还是要差的!

另推广:

1、凡是使用连接器的高速信号(背板高速信号设计),一般都是放置在tx端!

2、上述条件的例外是:如果使用了均衡器或预加重技术,当然还是放在rx端好了!

3、因此,放置在哪一端,必须要根据该信号的处理技术和构成而言,要分析驱动器的方式、电平逻辑构成、信号类型等,传统经验放置在rx端并不一定好用!

参考原文:《高速差分信号PCIe的耦合电容为什么要放在TX端?》

USB耦合电容位置

USB3.0只在SSTX信号放置AC耦合电容的疑惑与猜测

查看很多资料和电路图,发现在超高速差分信号中,只对SSTX信号放置AC交流耦合电容,对此很不理解,百度也没有百度出具体原因,只偶尔有看到说规范中是这样说的,好吧,实在没辙了,正好手中有此规范查阅规范,那就自己也找找看。一通乱找,终于看到了一点点信息,可是结果也是一样,只提到这样接,但是没有具体说明原因,当然本人英文能力有限,即使提到可能也找不到,尴尬尴尬啊!

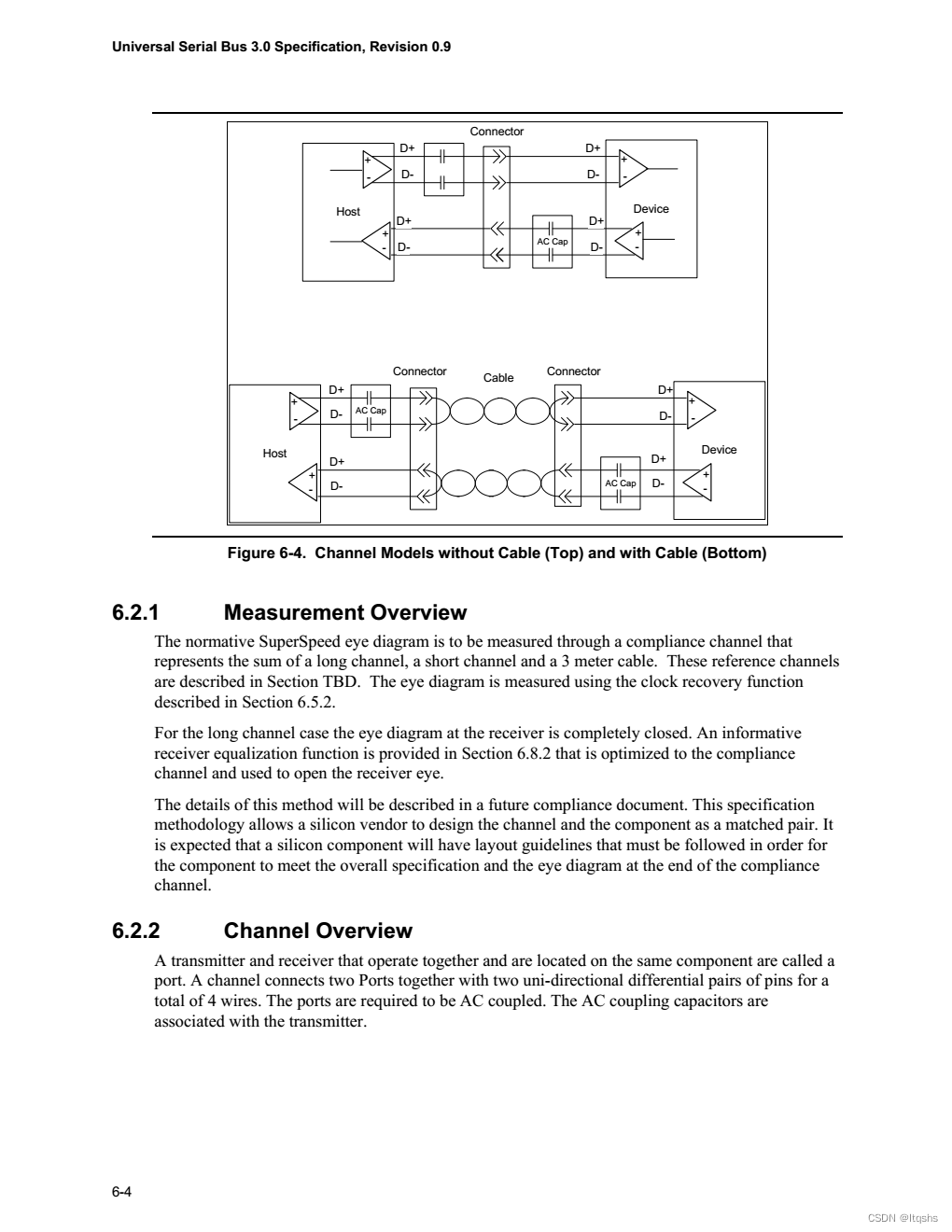

好了,在USB3.0 0.9版本第六章第二节中有提到如下截图信息。如下是个人猜测,很有可能是错误的,对于单独一个Host、Device来说,都只在TX信号接耦合电容,当Host与Device对接时,从整个链路来看,其实TX、RX都放置了AC耦合耦合电容,因为Host、Device的TX都是相对的,所以这样看就好了?所以也就不存在问题?所以也就要求不管你是Host,还是Device,只要在TX端放置耦合电容,在整个链路上都避免了因各自所在系统直流不一致的问题!难道这就其原理?!

参考原文:《USB3.0只在SSTX信号放置AC耦合电容的疑惑与猜想》

文章讨论了PCIe和USB高速信号中耦合电容放置的位置选择,强调了在TX端放置的重要性,尤其是在PCIe中考虑到连接器影响和去加重技术的影响。USB3.0中SSTX信号的特殊处理也做了说明。

文章讨论了PCIe和USB高速信号中耦合电容放置的位置选择,强调了在TX端放置的重要性,尤其是在PCIe中考虑到连接器影响和去加重技术的影响。USB3.0中SSTX信号的特殊处理也做了说明。

1751

1751

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?