在国内FPGA工程师圈里,VHDL用户其实并不多。

更多人选择Verilog或SystemVerilog来完成设计输入、验证和优化。

前段时间,我们介绍过《AMD FPGA设计优化宝典:面向Vivado/VHDL》,那本书以VHDL语言为主线,深入讲解了FPGA结构、代码风格与设计收敛方法,让不少使用VHDL的工程师直呼“终于有系统教材了”。

而今天要推荐的这本—— 《AMD FPGA设计优化宝典:面向Vivado/SystemVerilog》, 可以说是同一体系下的“姊妹篇”,但同时更贴近国内主流工程师的设计习惯。

📘正文内容

这本书以AMD(原Xilinx)7系列、UltraScale/UltraScale+、Versal ACAP为核心架构蓝本,从FPGA内部结构出发,系统讲解如何通过良好的RTL代码风格(SystemVerilog)与Vivado分析方法实现设计优化与时序收敛。

与传统教材不同,它并不只是罗列语法或工具功能,而是强调架构—代码—工具三者的联动关系。作者高亚军老师将多年的设计与支持经验提炼成具体的工程原则,帮助读者真正做到“理解FPGA、驾驭Vivado”。

📗 全书三大亮点:

1️⃣ 面向架构的代码风格 —— 每一条SystemVerilog语句都与硬件单元一一对应,避免“综合不匹配”的隐患。

2️⃣ Vivado与Tcl双路径分析 —— 不仅教你看报告,更教你“找问题”。

3️⃣ 思考与练习并重 —— 每章末尾附常见问题与思考题,共100个,帮助读者形成“优化思维”。

🧭主要内容概览

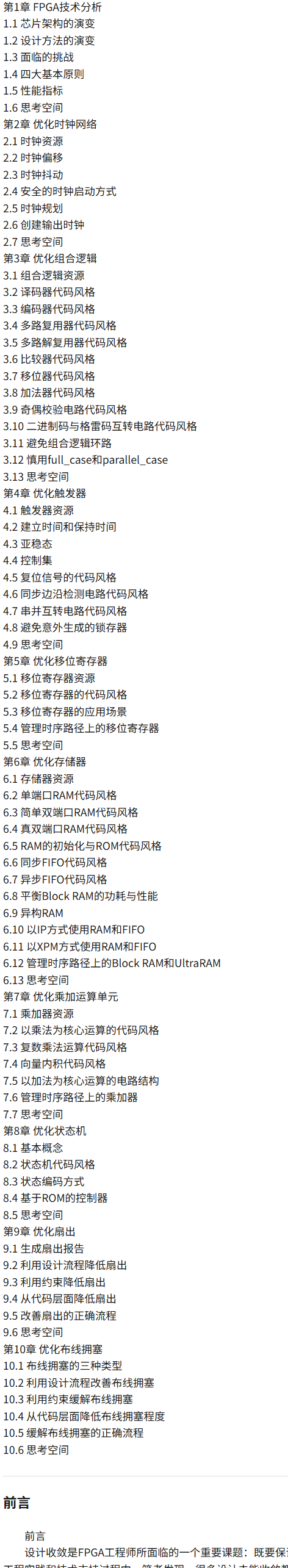

第1章 FPGA技术分析

从架构演进到设计挑战,建立整体优化思维。

第2章 优化时钟网络

时钟偏移、抖动与规划的系统方法。

第3章 优化组合逻辑

译码器、比较器、加法器等电路的SystemVerilog实现策略。

第4章 优化触发器

复位信号、控制集与亚稳态的管理。

第5章 优化移位寄存器

移位寄存器的结构与路径平衡。

第6章 优化存储器

RAM、FIFO与XPM的正确使用方式。

第7章 优化乘加运算单元

DSP48E单元的高效调用与乘法器设计。

第8章 优化状态机

两段式/三段式FSM设计与编码技巧。

第9章 优化扇出

多层次扇出优化策略。

第10章 优化布线拥塞

布局布线瓶颈的代码级化解方法。

💬结语 / 观点

如果说VHDL版的《AMD FPGA设计优化宝典》让我们理解了FPGA的“结构之美”, 那么这本SystemVerilog版,则带我们走进FPGA的“实现之道”。

它让RTL不再是抽象的描述,而是贴合架构、直达性能的工程语言。 对于使用Vivado的开发者来说,这本书,不仅是一本教程,更是一份系统化的优化指南。

图书链接

通过网盘分享的文件:AMD FPGA设计优化宝典:面向Vivado System Verilog_2023.pdf 链接: https://pan.baidu.com/s/1dDF98mkLjLMLJGBoa5cIwA?pwd=open 提取码: open

PS:如果本书对您有帮助,请购买正版书籍。另,本文分享资源只为了学习沟通,切勿商用,商用引起的任何纠纷与本公众号无关~

6868

6868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?