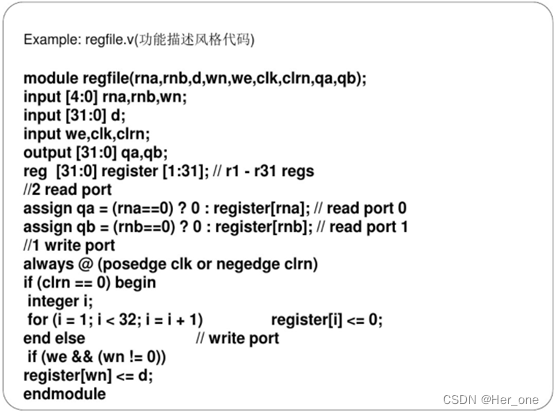

1.寄存器堆设计

用5位地址编码32个寄存器的地址。每个寄存器都是32位,每个寄存器都有写使能端信号。

函数原型:

module regfile (rna,rnb,d,wn,we,clk,clrn,qa,qb);

rna: 读寄存器地址1 5位

rnb: 读寄存器地址2 5位

d: 写数据 32位

wn: 写地址 5位

qa: 读出操作数1 32位

qb: 读出操作数2 32位

we: 使能端 1位

clk: 时钟 1位

clrn:复位 1位

代码:

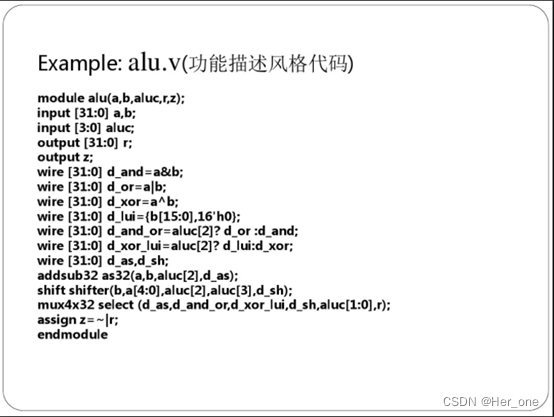

2.ALU

alu算术逻辑单元要实现ADD(加)、SUB(减)、AND(寄存器与)、OR(寄存器或)、X0R(异或)、SLL(左移)、SRL(逻辑右移)、SRA(算术右移)、LUI(立即数左移)等计算功能,具体执行什么运算由4位aluc决定。

函数原型:module alu (a,b,aluc,r,z);

a: 源操作数1 32位

b: 源操作数2 32位

aluc: 操作控制码 4位

r: 目的操作数 32位

z: 零标志位 1位

ALU使用到的模块:

1) addsub32模块:32位加减运算模块利用并行进位加法器(cla32模块)

2) shift模块:实现移位

3) mux4x32:32位四选一选择器

代码:

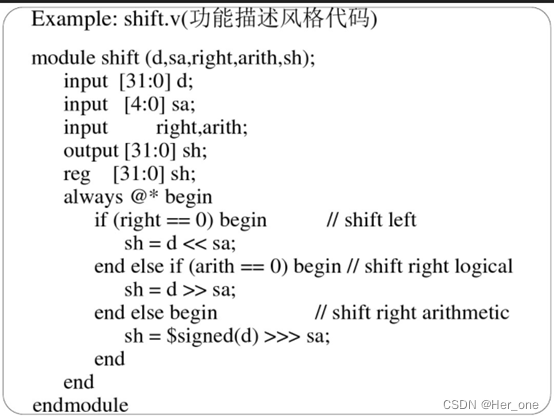

3.32位移位器

d是32位输入信号

sh是 32位输出信号

sa是5位移位位数控制信号

right是右移控制信号

arith是算数右移控制引号

代码:

1444

1444

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?