大家好!好久不见,前一段时间出差没有来得及更新Blog,小小的愧疚一下。今天,主要介绍的是Xilinx 7 Series FIFO的结构,以及代码实现。

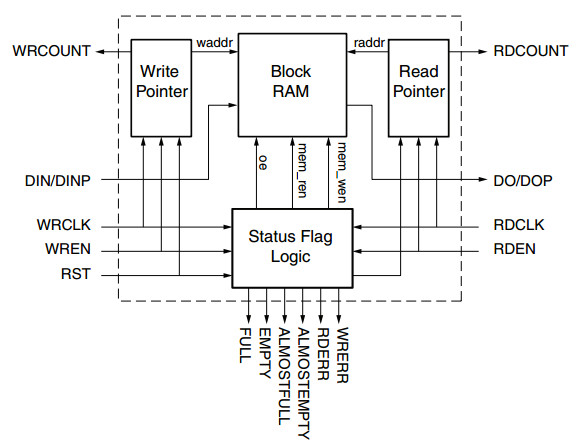

FIFO的结构如下图所示,分为状态标志产生模块、写指针模块、双端口Ram以及读指针模块。

本文先介绍一下同步FIFO的实现方式,next time详细介绍异步FIFO。其中,同步FIFO的状态标志产生模块,主要根据写/读的指针与设定的深度/Almost Full/Almost Empty进行比较,来产生Full/Afull/Empty/Aempty的标志信号,并在FIFO出现Full和Empty时对写/读进行保护。满标志信号产生代码如下:

always @(posedge clk or posedge rst)

if (rst)

full <= 1'b0;

else

case(winc,rinc)

2'b10 : full <= (left == C_DEP - 1) ? 1'b1 : 1'b0;

2'b01 : full <= (left == C_DEP) ? 1'b0 : 1'b1;

default : full <= full;

endcase空标志产生代码如下:

always @(posedge clk or posedge rst)

if (rst)

empty <= 1'b0;

else

case(winc,rinc)

2'b01 : empty <= (left == 1) ? 1'b1 : 1'b0;

2'b10 : empty <= (left == 0) ? 1'b0 : 1'b1;

default : empty <= empty;

endcase同理与以上full和empty的产生过程,afull和aempty只需要改变left的判断数值就可以了。

若full和empty的时候,则需要对写和读进行保护,代码如下:

winc = wr_en && !full;

rinc = rd_en && !empty;Left状态产生代码如下:

always @(posedge clk or posedge rst)

if (rst)

left <= {C_PW{1'b0}}:

else

case(winc,rinc)

2'b10 : left <= left + 1'b1;

2'b01 : left <= left - 1'b1;

default : left <= left;

endcase写/读指针产生模块代码:

always @(posedge clk or posedge rst)

if (rst)

wr_pointer <= {C_PW{1'b0}};

else if (winc)

wr_pointer <= wr_pointer + 1'b1;

always @(posedge clk or posedge rst)

if (rst)

rd_pointer <= {C_PW{1'b0}};

else if (rinc)

rd_pointer <= rd_pointer + 1'b1;同步FIFO的实现较为简洁,也比较理解。异步FIFO不同与同步FIFO的时,读/写端口的时钟不同,其内部比较产生状态信号的指针不同,他是将二进制指针转化为格雷码指针,然后进行比对,下一篇bolg会进行详细介绍。

2385

2385

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?