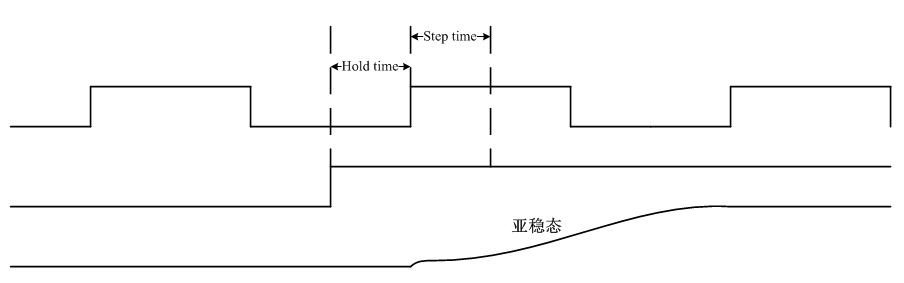

FPGA设计中,复位方式分为异步复位和同步复位。其中,异步复位较为常见,但是异步复位常会遇到亚稳态的问题,如下图所示:

当异步复位信号在释放时,Hold time不满足时,D触发器的内部寄存器数值会出现亚稳态的状态。

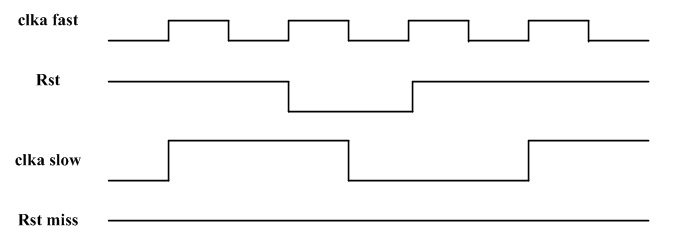

同步复位方式,如果该复位信号需要进行跨时钟域的话,很有可能会出现如下所示的情况:

时钟域clka的reset信号,打两拍进行跨时钟域处理,但clkb的时钟较慢,导致clkb没能采集到rst信号,从而丢失reset复位信号。

综上所述,异步复位容易导致亚稳态,但不会丢失reset;同步信号不会出现亚稳态,但可能会丢失复位信号。将两种方法进行结合,”异步复位,同步释放“能够避免亚稳态的出现,而且能够保证复位信号的保持。

常用的FPGA实现方法如下,其中rst_n为clka时钟域下的复位信号,rst_b_n为clkb时钟域下的复位信号。

always @(posedge clkb or posedge rst_n)

if (!rst_n)

i_rst_n <= 1'b0;

rst_b_n <= 1'b0;

else

i_rst_n <= 1'b1;

rst_b_n <= i_rst_n;

1109

1109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?