基于fpga生成高斯白噪声信号,能仿真和上板,附带仿真说明文档。

代码有Verilog和VHDL两个版本。

ID:53400723550055922

芳草街有志秋葵

基于FPGA生成高斯白噪声信号:Verilog与VHDL双版本实现

一、引言

在通信系统中,噪声是信号传输中不可避免的一部分。而高斯白噪声(Gaussian White Noise)是通信领域常见的一种噪声模型,它对于系统性能的分析和评估至关重要。在硬件实现中,FPGA(Field Programmable Gate Array)由于其并行处理能力和灵活性,成为生成高斯白噪声信号的理想选择。本文将介绍如何使用FPGA生成高斯白噪声信号,并提供基于Verilog和VHDL两种硬件描述语言的实现方法。

二、高斯白噪声简介

高斯白噪声是一种连续的概率分布,其概率密度函数服从正态分布。在通信系统中,高斯白噪声具有均值为0,方差为σ^2的特性。由于其概率分布特性,它在通信系统中被广泛用作一种干扰模型,用于评估系统的抗干扰能力和性能。

三、FPGA实现高斯白噪声信号生成

- 总体设计

在FPGA上生成高斯白噪声信号,需要设计一种随机数生成器,并对其进行适当的滤波处理,以满足高斯分布特性。同时,需要考虑信号的功率控制,以确保其满足系统需求。

- 随机数生成器设计

在FPGA上生成随机数,常用的方法包括线性同余法、Mersenne Twister法等。为了简化设计,我们可以采用线性同余法生成伪随机数。线性同余法的优点是生成速度快,但缺点是随机性不如真正的随机数。

- 滤波处理

为了得到高斯分布的特性,需要对生成的随机数进行滤波处理。常用的滤波方法包括Box-Muller变换、Ziggurat算法等。Box-Muller变换是一种常用的方法,它可以将均匀分布的随机数转换为服从正态分布的随机数。

- 功率控制

在生成高斯白噪声信号时,需要考虑信号的功率控制。常用的方法包括调整信号的幅度或调整滤波器的系数。

四、Verilog与VHDL双版本实现

- Verilog版本

在Verilog中,我们可以使用内建的随机数生成器(如$random)和滤波处理函数,来实现高斯白噪声的生成。具体实现时,需要注意随机数的生成频率和滤波器的设计。

- VHDL版本

在VHDL中,我们可以使用内建的随机数生成函数(如RANDOM)和滤波处理逻辑,来实现高斯白噪声的生成。与Verilog类似,需要注意随机数的生成频率和滤波器的设计。

五、仿真与上板测试

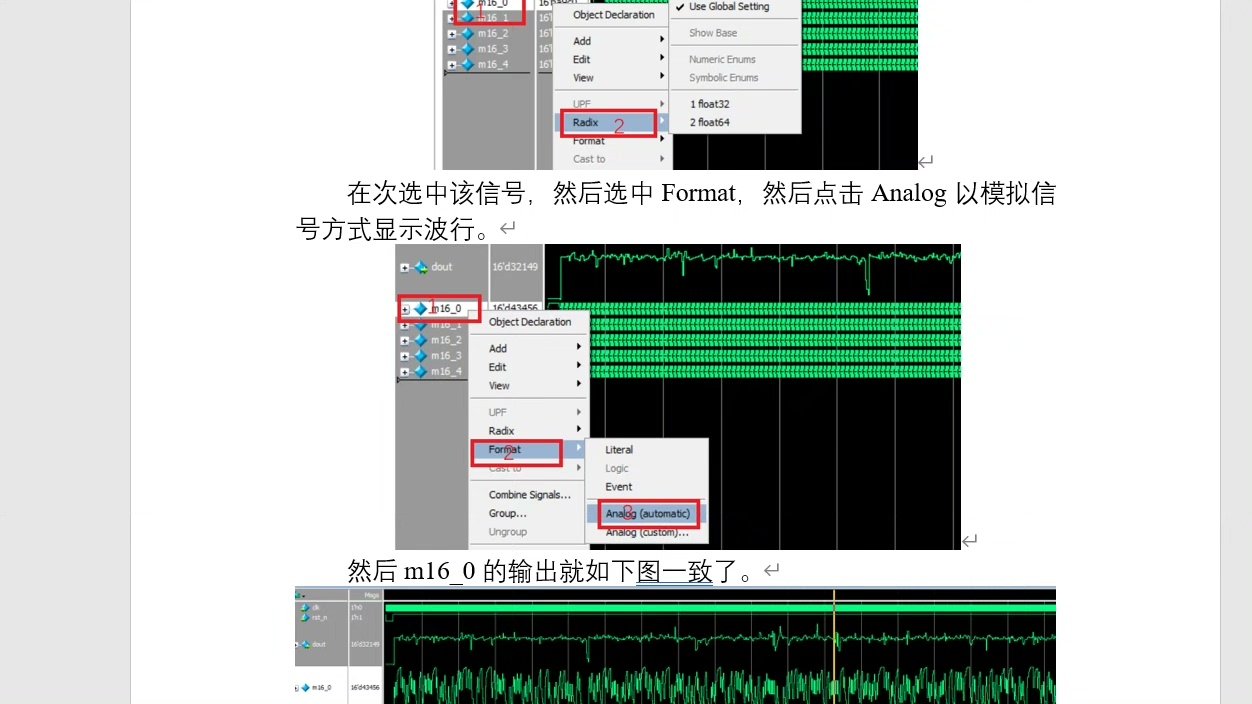

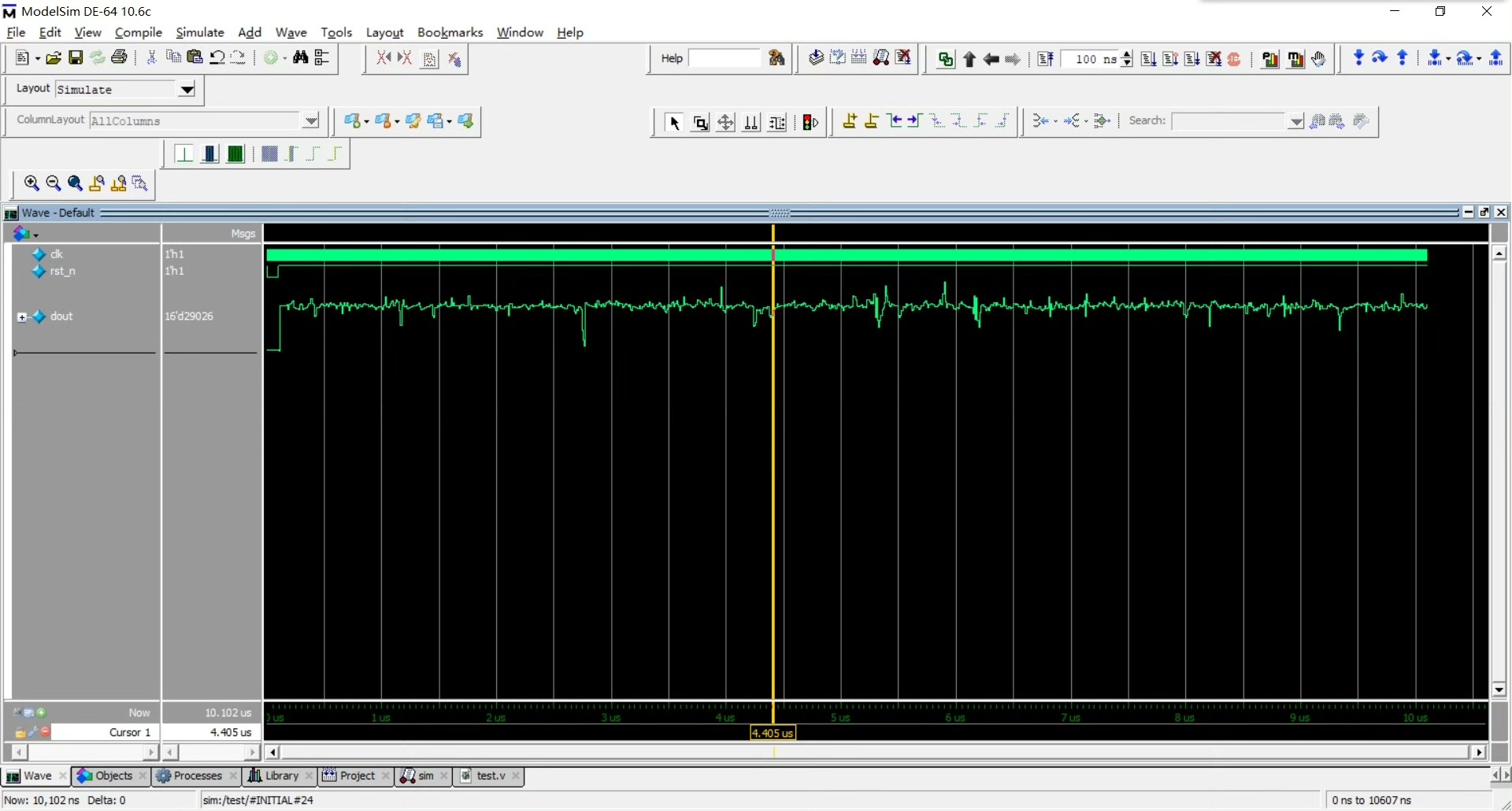

- 仿真

在FPGA开发环境中,我们可以使用仿真工具(如ModelSim、Vivado等)对生成的高斯白噪声信号进行仿真验证。仿真过程中,可以观察信号的分布特性、功率等参数,以确保其满足设计要求。

- 上板测试

在FPGA板上测试时,需要确保信号的生成、传输和接收都符合预期。在测试过程中,需要注意信号的稳定性和可靠性,以及系统的性能表现。

六、结论

基于FPGA生成高斯白噪声信号,可以方便地评估通信系统的抗干扰能力和性能。本文介绍了基于Verilog和VHDL两种硬件描述语言的实现方法,并给出了仿真和上板测试的说明。在实际应用中,可以根据具体需求选择适合的硬件描述语言实现。

具体的代码,程序如下地址:http://wekup.cn/723550055922.html

2073

2073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?