基于fpga的DES加解密算法。

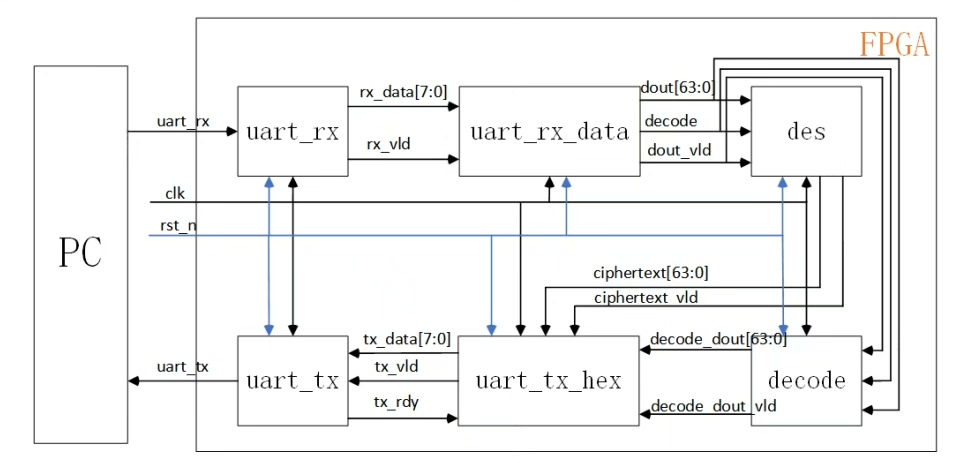

利uart串接收PC端发送的数据,根据数据类型,对数据进DES加密或者解密处理。

将处理的数据通过uart传回PC端。

可以通过上位机对64位密钥进行设置,另外加解密模块是独立的,如果需要,完全可以加入其他模块,对数据进行加解密操作。

提供完整设计文档,可以提供上板验证。

ID:16900723223553603

芳草街有志秋葵

基于FPGA的DES加解密算法实现与应用

一、引言

随着信息技术的飞速发展,数据加密已成为保护信息安全的重要手段。DES(Data Encryption Standard)作为一种经典的对称加密算法,在现代通信系统中有着广泛的应用。本文将介绍一种基于FPGA(Field Programmable Gate Array)的DES加解密算法实现,通过UART串口实现数据的收发,并对数据类型进行DES加密或解密处理。

二、FPGA与DES算法的结合

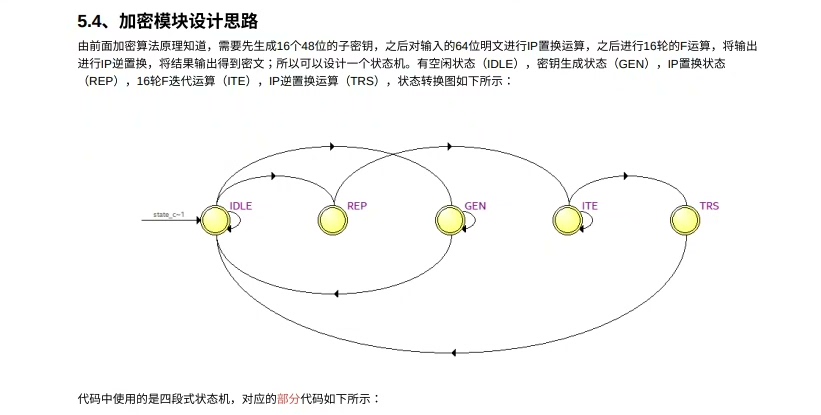

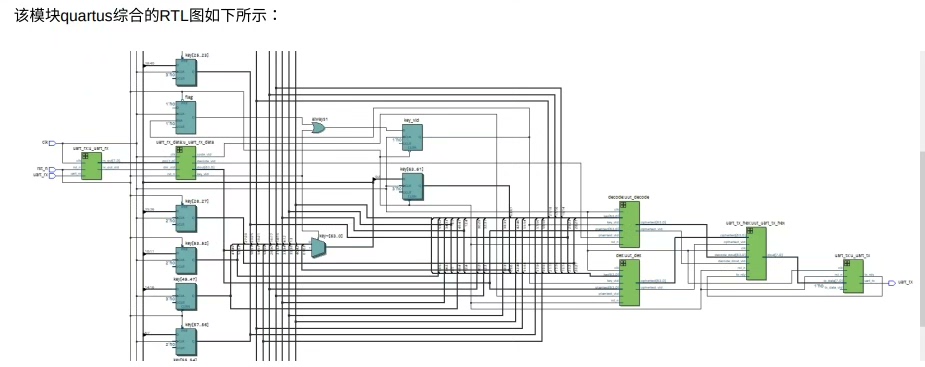

FPGA是一种可重构的数字电路,具有高度的灵活性和可编程性。将其应用于DES算法的实现,可以有效地提高数据处理的速度和效率。在FPGA上实现DES算法的主要步骤包括:设计DES算法的硬件描述语言(HDL)代码,进行功能仿真和验证,然后将验证无误的代码烧录到FPGA芯片中。

三、基于UART串口的通信设计

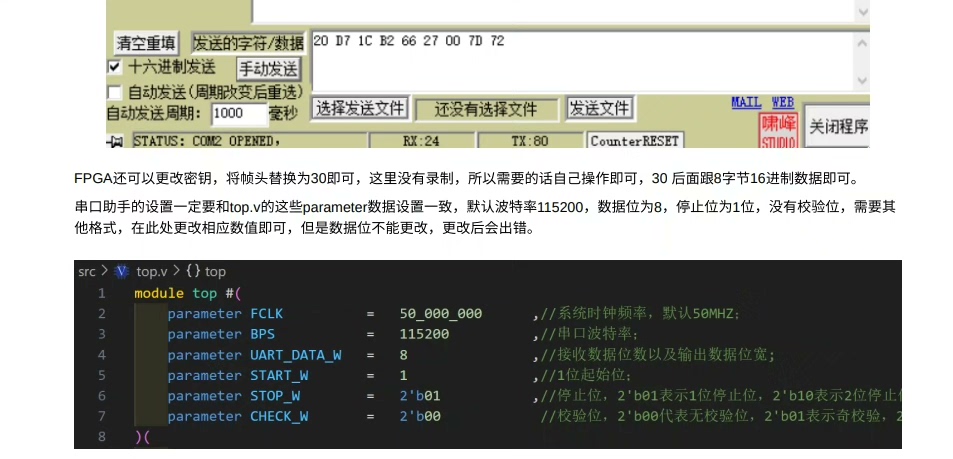

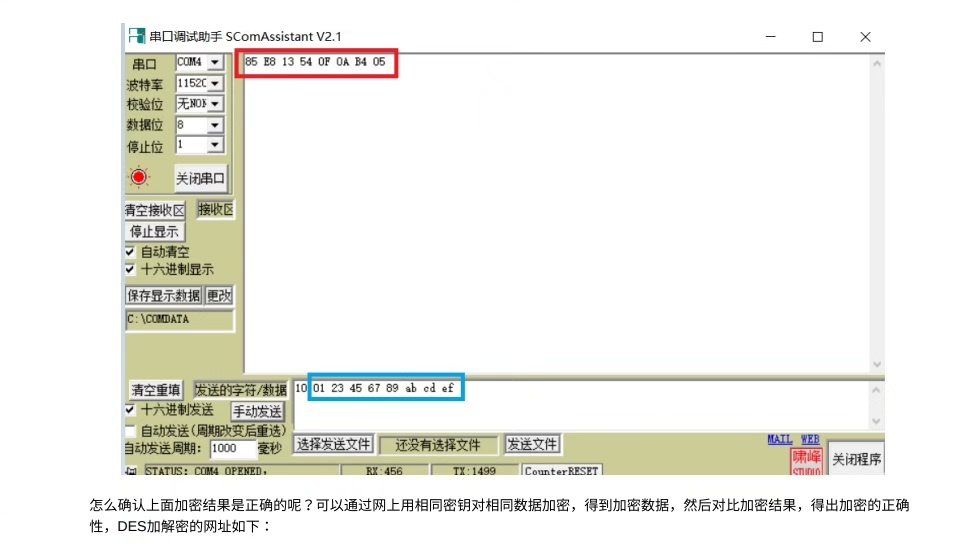

为了实现与PC端的通信,我们采用UART串口进行数据收发。通过UART串口,PC端可以向FPGA发送数据,FPGA接收数据后根据数据类型进行DES加密或解密处理,然后将处理后的数据通过UART串口传回PC端。这一设计过程中,需要编写串口通信协议,确保数据的正确传输和处理。

四、密钥管理模块的设计

为了实现对DES算法的密钥管理,我们设计了一个上位机软件,用于设置和管理64位密钥。用户可以通过上位机软件方便地修改和更新密钥,确保系统的安全性。加解密模块是独立的,可以与其他模块无缝集成,实现对数据的加解密操作。

五、系统实现与测试

在实际系统中,我们完成了基于FPGA的DES加解密算法的实现,并进行了严格的测试。测试结果表明,系统能够实现数据的正确加解密处理,且处理速度较快。此外,我们还提供了完整的设计文档,包括硬件设计、软件设计、测试报告等,方便其他开发者进行学习和参考。

六、模块的扩展性与可维护性

基于FPGA的DES加解密模块具有良好的扩展性和可维护性。由于FPGA的可重构性,我们可以方便地添加其他模块,如AES加密模块、哈希函数模块等,以满足不同的需求。此外,通过上位机软件,我们可以实现对系统的远程管理和维护,方便用户进行系统的升级和维护操作。

七、实际应用场景

基于FPGA的DES加解密算法可以广泛应用于各种需要数据加密的场合。例如,在物联网领域,可以对传感器采集的数据进行加密传输,确保数据的安全性;在通信系统中,可以对通信数据进行加解密处理,防止通信内容被窃取或篡改;在存储系统中,可以对存储数据进行加密存储,防止数据泄露。

八、总结

本文介绍了一种基于FPGA的DES加解密算法实现,通过UART串口实现数据的收发,并对数据类型进行DES加密或解密处理。系统具有较高的处理速度和安全性,具有良好的扩展性和可维护性。实际应用中,可以根据需求添加其他模块,满足不同的加解密需求。未来,我们将继续优化系统性能,提高系统的安全性和稳定性,为数据安全保护提供更好的解决方案。

具体的代码,程序如下地址:http://wekup.cn/723223553603.html

186

186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?