《IPcore-SoC设计》

作者:AlphawaveIP:TonyPialis,ClintWalker

本文摘要:

-

简要介绍高速接口基础知识,以及推动200Gbps连接需求的行业动机。

-

回顾在将速率提升到200Gbps时所面临的挑战,以及实现这一壮举所需的不同调制方案。

-

描述用于实现200Gbps接收机的各种方法,以及用于提高相关误码率的纠错和编码方法。

-

回顾一些实际的200Gbps信道和仿真结果。

-

给出在200Gbps串行链路上的结论、发现和预测。

高速接口基础介绍

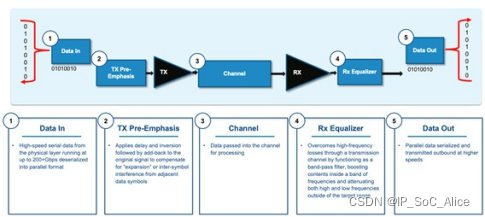

图1展示了任何连接接口的基本组成模块。

图1:通信系统图

在电子系统中,连接功能无处不在,并应用在一个芯片必须与另一个芯片建立连接的任何地方。连接长度可以从跨越数千英里的距离(传统上由高速光网络解决),到用于将芯片直接相互连接的短距chip-to-chip链接。由于每个芯片内部都使用电信号工作,因此电气连接接口是半导体设计的一个重要功能块。

所有计算机芯片都使用数字数据。它们以字节和字的形式出现。一个字节最多包含8位数据,而一个字包含1到16个字节。串行器/解串器(SerDes)在集成电路中被用作与其他芯片的接口,通过将集成电路中使用的并行数据流转换为串行数据流,用于芯片外部和芯片之间的长距离传输,反之亦然。通常,由于时序、同步和占用空间的优势,串行传输在更长的距离上效率更高,复杂性更低,而并行传输对于实现吞吐量和性能的芯片内部至关重要。由于这一关键差异,每个需要快速可靠外部连接的集成电路都需要SerDes。

SerDes由发送器和接收器组成。发送器接收并行数据字,将其串行化并为信道预处理。预处理将数字字转换为真实世界的模拟波形,发送器根据该波形驱动信道上的信号。信道可以是铜缆、光缆、电子板等。

最终,接收器从信道接受真实世界的数据。然后对其进行调节、均衡和重新采样,以补偿信道引入的噪声和干扰。最终,接收器将真实世界的信号转换回数字1和0、数据字节和数据字。

行业需要200G连接!

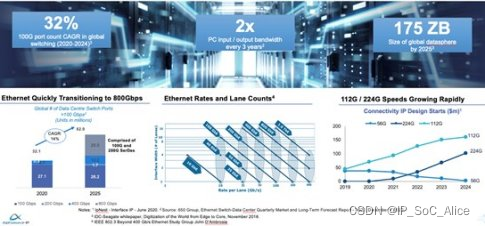

图2:推动采用224Gbps标准的行业趋势

在过去十年中,新技术、应用、基于云服务和互联网连接设备的激增导致数据流量和拥塞水平的增加,从而推动了对更大带宽的需求。全球数据领域或创建、捕获、复制和消费的数据将从2019年的40兆字节增长到2025年的175兆字节,复合年增长率(CAGR)为28%。这些数据的很大一部分必须使用有线网络基础设施进行传输。以下因素推动了数据的快速创建和使用,包括:

随着云服务、5G、物联网及人工智能的快速发展,对高速连接的需求激增,200Gbps串行互连成为关键。本文探讨了高速接口的基础、行业需求、挑战以及应对策略,包括PAM4调制、高级DSP检测器和FEC技术在提升信道性能和SNR方面的作用。通过实际仿真和测试,证明224Gbps连接在长距离传输中是可行的,未来可能在不同应用场景中采用不同的调制方案,如PAM4和PAM6。

随着云服务、5G、物联网及人工智能的快速发展,对高速连接的需求激增,200Gbps串行互连成为关键。本文探讨了高速接口的基础、行业需求、挑战以及应对策略,包括PAM4调制、高级DSP检测器和FEC技术在提升信道性能和SNR方面的作用。通过实际仿真和测试,证明224Gbps连接在长距离传输中是可行的,未来可能在不同应用场景中采用不同的调制方案,如PAM4和PAM6。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?