这篇文章主要讲一下基于扫描路径的可测性设计。

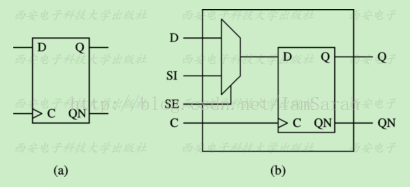

对于一个组合逻辑的电路,电路中的故障可以通过输入端口施加向量进行激励。而对于一个复杂、端口有限的时序电路,只能采用基于扫描路径的可测性设计方法来实现对电路的可控制性和可观测性。在该方法中首先需要将非扫描单元如寄存器用扫描单元取代,如下图所示:

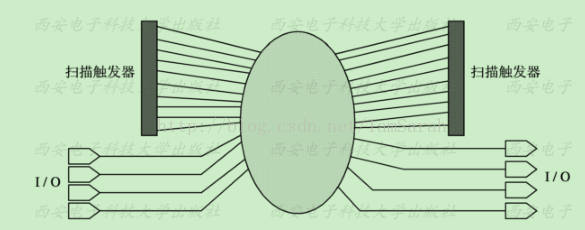

这种结构非常简单,但却非常巧妙。当电路中的寄存器用扫描寄存器取代以后,在扫描模式下,电路中的时序路径可以变成下图的结构。这样组合逻辑的输入激励可以通过输入端口及扫描寄存器来输入,组合逻辑的输出可以通过扫描寄存器移出到输出端口,从而实现激励的施加和响应的捕获。

本文深入探讨基于扫描路径的可测性设计在集成电路中的应用,解释如何通过扫描链实现时序电路的控制和观测。内容包括扫描路径的结构、工作原理、测试步骤以及面向扫描测试的RTL设计注意事项,如时钟边沿、多时域、门控时钟等问题的处理。

本文深入探讨基于扫描路径的可测性设计在集成电路中的应用,解释如何通过扫描链实现时序电路的控制和观测。内容包括扫描路径的结构、工作原理、测试步骤以及面向扫描测试的RTL设计注意事项,如时钟边沿、多时域、门控时钟等问题的处理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4455

4455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?