#前言:

通信领域可分细支众多,在通信过程中总会用到各种各样的协议,而根据通信的对象不同,协议不同,实现方法不同。但大致可分为两类硬件通信和软件通信。从事务逻辑发展角度来说,通信是结果,不论软硬件,只是对应不同的应用场景手段不同罢了。

之前我就有个很silly的问题,学硬件好还是软件好?其实现在看看这个问题,这两个没有好坏之分,前提是你得学,这不就巧了吗?偏偏那时候我没学,等到现在才学,一晃,两年过去了。浪费生命啊!!!痛心疾首中~如果非要杠工资高低,其实在各行各业做到顶尖的人工资都会差,而硬件软件做出来的产品的售价、销量等多方面因素都会影响,重要的还是自身的能力吧。

从专业角度分析FPGA火在哪里?

一、FPGA是什么?

FPGA到底是什么?简单来说,就是一块可由工程师反复编程的逻辑器件,本体是一种数字集成电路,一个可以通过编程来改变内部结构的芯片。

电子专业的同学基本上是ASIC(特定应用集成电路)这里插入下关于ASIC的知识:

ASIC(Application-Specific Integrated Circuit,特定应用集成电路)是一种定制的、专门为特定应用设计的集成电路。与通用处理器(如CPU和GPU)不同,ASIC 被定制为执行特定任务或应用,通常以高度优化的方式执行特定的计算操作。ASIC 的设计旨在提供最佳性能和效率,因为它专门用于执行一种或几种紧密相关的任务。

在与CPU、GPU和NPU的比较中,ASIC 有一些独特的特点:

- 定制性: ASIC 的设计是为了满足特定的应用需求,因此它可以在硬件级别上进行高度的定制,以实现最佳性能。

- 性能和效率: 由于 ASIC 专注于特定应用,它通常能够提供比通用处理器更高的性能和效率。这使得 ASIC 在特定领域的计算任务中表现出色。

- 电力效率: ASIC 的设计优化通常使其在特定任务上更为节能,因为它仅执行特定的计算操作,避免了通用处理器可能面临的冗余计算。

- 应用范围: ASIC 可以用于各种应用,包括密码学、信号处理、网络通信和各种专门的计算任务。

二、ASIC问题出现

ASIC一旦被设计好,其固定结构已经成型 ,后期将无法更改。why?给你看

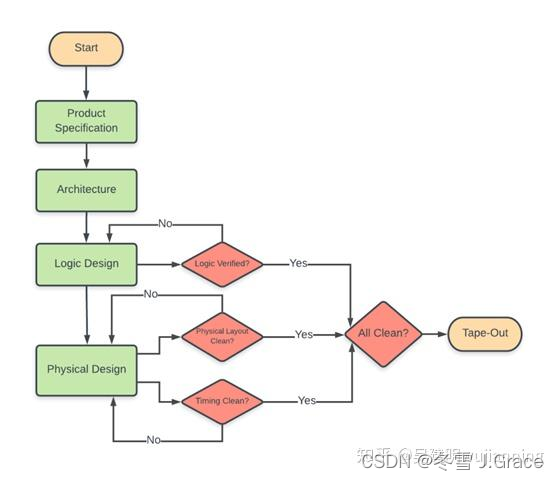

Figure 1: ASIC Design Flow

ASIC Specification

ASIC设计流程的第一步是在开始设计之前定义产品的规格。

这一阶段通常包括与潜在客户进行市场调查,以确定需求,并与技术专家交谈以判断未来趋势。后者尤其重要,因为ASIC设计周期可能在6个月到2年之间。因此,重要的是要预见和预测未来1-2年内的趋势,如果一个人需要向广泛的消费者销售他们的产品。

这项市场调查转化为高水平的产品规格。制定一个全面和正确的规范通常为ASIC设计奠定了坚实的基础。技术规范需要随着时间的推移对技术要求进行细化,但以明确的方式涵盖这些信息是很重要的。

ASIC Architecture

在删减规范之后,现在是将整个ASIC功能划分为多个功能块的时候了。架构师喜欢集思广益地讨论架构的许多可能选项,并在考虑性能影响、技术可行性以及成本和时间方面的资源分配时讨论它们的优缺点。

一个好的架构专注于收集ASIC芯片的最佳性能,同时最小化硬件资源,这直接有助于将芯片的总体成本保持在分配的预算内。在此阶段,架构师定义不同功能块之间的关系,并为每个功能块分配时间预算。所有这些技术细节都包含在架构文档中。

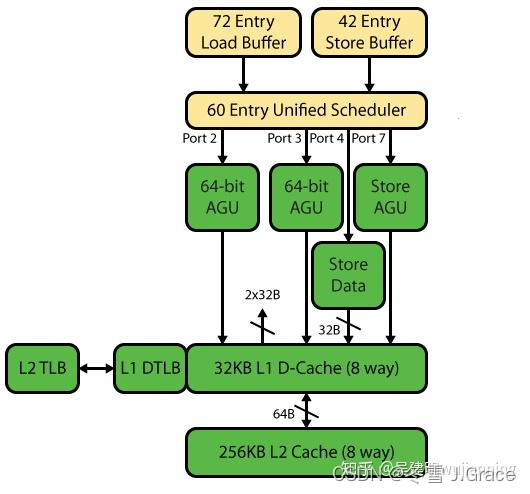

Figure 2: Micro-architecture of Intel’s Haswell Processor.

一旦您对所需的所有功能块有了较高的了解,那么就应该谨慎地确定关键模块,并可能就是否需要重新使用以前项目中的这些IP、对现有IP进行必要的更改或从其他方获得它们。

硬件和软件块之间的划分也是ASIC设计阶段的一个关键部分。设计是用C++或C语言的高级编程语言来捕获的。

Logic Design and Verification

他的步骤是指ASIC设计流程的前端部分,包括用Verilog、VHDL或systemverilog等硬件描述语言对每个功能块的数据流进行编码。功能块之间的交互也被编码。逻辑设计通常包括:

组合逻辑Combinational Logic:

组合逻辑通常指布尔组合门,如OR、AND、NAND、NOR等。虽然这些门很简单,但它们可以组合起来执行复杂的数字运算。

序列元素Sequential Elements:

序列元素通过临时存储其输出,在执行不同功能的不同组合逻辑云之间的接口中起着关键作用。这些时序元件,如触发器和锁存器也被称为存储器元件,由时钟的同步或控制信号控制。触发器和锁存器都是双稳态元件,因为它们有两种稳定状态:0或1。

有限状态机(FSMs)Finite State Machines (FSMs):

它们是顺序逻辑的高级抽象,可以在硬件和软件中实现。有限状态机模拟数字机器对一组输入的响应,以产生确定的一组输出,是逻辑设计者的重要组成部分。

算术逻辑块Arithmetic Logic Blocks:

算术运算是计算逻辑的核心,通常是高性能CPU核心性能的瓶颈。算术运算包括加法、减法、乘法和除法。这些电路有很多种可能的实现方式,它们在性能、面积和功率之间进行权衡。逻辑设计者可以选择一个最适合他们的应用程序来优化一个或多个参数。

数据路径设计Data-path Design:

除了上述元素的编码组合外,硬件描述语言(hdl)可以像编程语言一样以抽象的方式对数据路径设计进行建模,这种方法可以被EDA工具正确地解释。这些可以是多路复用、解码、case语句等。

模拟设计Analog Design:

除了数字逻辑之外,ASIC还可以有许多模拟组件来帮助与现实世界接口,并且可以包括温度传感器、模数转换器(ADC)和数模转换器(DAC),最重要的是时钟产生单元锁相环(pll)。Physical Design

这是指后端设计周期。如果后端设计和前端设计只有一个区别,那就是延迟。前端设计虽然认识到了逻辑延迟和速度,但在RTL编码和验证的大部分工作中却忽略了这一点。而另一方面,物理设计从一开始就看到了真正的延迟。

Figure 3: Gate level implementation of 2:1 Multiplexer

平面规划

布局规划步骤正式化并细化了在架构(architecture)规划步骤中首次出现的平面图。在这一步中,整个模具区域被划分为物理分区,并在成型时考虑到区域要求、顶层数据和控制总线的流动、未来增长的可能性。管脚和端口被指定一个粗略的位置,可以根据位置和路由结果进一步细化。

Figure 4: Floorplanning the blocks relative to each other.

对于物理设计工程师来说,并行处理一个以上的平面图是很常见的,并试图评估哪一个最适合总体设计的QoR(结果质量)。这通常是物理设计周期中最关键的一步,需要多次迭代。考虑到它对路由routing congestion, cell density, timing QoR and DRCs拥塞、单元密度、时间QoR和DRC的长期影响,在这里花费的任何额外时间都是值得的。

一个强大的功率交付-解决静态和动态红外衰弱也是一个关键的功能规划步骤。

安置

在放置期间,所有标准单元都放置在站点行的合法位置。这一步的目标是最小化导线长度,同时确保最佳布局,这将有助于更快的定时收敛。

Figure 5: Standard Cells arranged on site rows.

在此步骤中没有铺设真正的路线。Placement通过一个称为全局路由的步骤来估计路由,在这个步骤中,它估计总的线路长度和全局路由拥塞。许多现代布局引擎能够考虑SAIF或VCD文件的切换活动,并尝试优化布局以获得更低的动态功率。

Figure 6: Placed design.

Clock Tree Synthesis

到目前为止,时钟网络是理想的。在时钟树合成过程中,时钟被传播并且时钟树被使用时钟缓冲器合成。这一步的主要目标是在最小化时钟偏差的同时实现最佳的时钟延迟。设计最佳时钟树的算法有很多种——H树、Steiner树等。除此之外,还可以选择时钟树网格、多源时钟树综合或传统的单点时钟树综合,这些方法在动态功率、路由资源和OCV调整等方面进行了权衡。

Figure 7: Typical H tree clock distribution.

时钟是本设计中开关频率最高的信号,时钟缓冲树占专用集成电路动态功耗的75%以上。架构可以支持时钟门控关闭芯片的空闲部分,以节省动态功耗。

随着所有实例的放置和时钟的路由,现在是时候路由信号网络了。现代工艺支持10-12金属层堆叠,M0-M1为标准单元布线预留。用于详细路由的算法通常是一个美化的迷宫路由器,并添加了约束,以确保更快的运行时间。元组资源被划分为元组路线的合法位置。详细布线的目的是确保最少的绕道,因为这些可能会影响时间,并确保最小的DRC(设计规则检查)违规,如开路、短路等。此步骤执行多个搜索和修复循环(10-20),以保持总体DRC计数较低。

Figure 8: Routed Design.

Physical and Timing Verification

逻辑验证确保功能正确,物理验证确保布局正确。物理验证检查增加了,包括-DRC(设计规则检查)、LVS(布局与原理图)、电迁移、静电放电违规(ESD)、天线违规、模式匹配(PM)违规、短路、开路,漂浮网等(includes- DRC (Design Rule Checks), LVS (Layout versus Schematic), Electromigration, Electro-static discharge violations (ESD), Antenna violations, Pattern Match (PM) violations, Shorts, Opens, Floating nets etc.)。重要的是要跟踪这些违反的地方和路线,以避免任何意外前几天关闭。

时序验证通过确保设计中所有时序路径都满足设置和保持,验证芯片以指定频率运行

Figure 9: FRICO ASIC, 350 nm technology

ASIC设计是一个复杂的工程问题,从概念到硅都要经历很多步骤。虽然有些步骤更像是艺术而不是工程(如平面布置图),但其他一些步骤需要合理的工程权衡(如物理设计和时间安排)。随着对更好性能和缩短上市时间的需求增加,ASIC设计流程在未来十年将继续变得更加复杂。然而,核心动机和设计理念将保持不变。

so 复杂 right?所以,不能改动。那么如果我们只是想要实现一些简单的功能,对一些参数的要求并非那么adequate,那么我们需要的只是简单的电路板,一个可以完成简单重复功能且可修改的电路板。well,that is FPGA.which you need it excatly!

三、FPGA神兵天降

而FPGA正是可以通过编程来改变内部结构,可以对后期的升级带来极大的便利。

1.基础构成:

FPGA芯片主要由六部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

2、FPGA的应用

FPGA 介于软件和硬件之间,用它做接口、做通信,它就偏向硬件;用它做算法、做控制,它就偏向软件。随着人工智能、机器视觉的崛起,FPGA 更加偏向软件算法的异构,有和 GPU 一争高下的潜力。

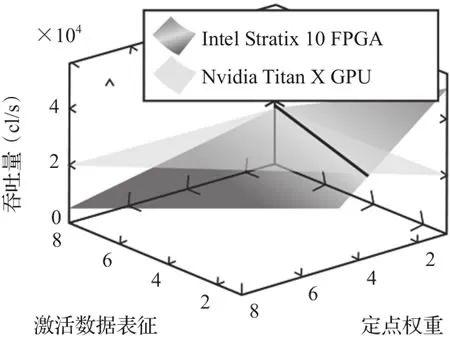

FPGA 与 GPU 性能对比图如图 10 所示:

图 10 FPGA与GPU的性能对比图

FPGA 软件方向:以软件开发为主,开发 FPGA 在数据分析、人工智能、机器视觉等领域的加速应用能力,主要采用 OpenCL 和 HLS 技术实现软硬件协同开发。

FPGA 硬件方向:以逻辑设计为主,针对FPGA特定领域的应用设计、集成电路设计以及芯片验证能力。

FPGA 最初的应用领域是通信领域(没错,就是我的专业,通信工程!!!),但是随着信息产业和微电子技术的发展,FPGA 技术已经成为信息产业最热门的技术之一,应用范围扩大,遍及航空航天、汽车、医疗、广播、测试测量、消费电子、工业控制等热门领域,而且随着工艺的发展和技术的进步,从各个角度开始渗透到生活当中。

从商业角度分析FPGA火在哪里?

许多读者都知道 FPGA 功能强大,但它强大在哪儿?

以单片机举例说明,我们都知道,单片机功能强大,几乎无所不能,而 FPGA 与之相比只强不弱。因为只要单片机能实现的功能,FPGA 就一定能实现,当然这需要加一个大前提——在 FPGA 资源足够多的情况下。但是 FPGA 能实现的功能,单片机却不一定能够轻松实现,这是不争的事实,如果你不相信,那只能说明你还不了解 FPGA。

说到这里,读者不禁要问,既然 FPGA 这么厉害,为什么单片机的使用范围更广?那是因为在商业中,价格往往是影响产品的重要因素之一。

单片机的价格要远远低于 FPGA,而且根据性能和资源的不同,FPGA 的价格也存在很大差异,单枚 FPGA 芯片的价格从几十元到几十万元不等。与之相比,单片机的价格要便宜很多,同样的功能我们如果可以用价格低廉的单片机实现,就不会选择相对昂贵的 FPGA 了,除非单片机满足不了功能需求。所以公司自己进行开发时,为了节约成本,可能会选择更加便宜的单片机,而不会选择相对昂贵的 FPGA,因为单片机、ARM 这种微处理器的需求量很大,所以价格上更有优势。

但无论是单片机、ARM 还是 FPGA,它们都只是一种帮助我们实现功能的工具,具体如何选择,需要根据具体问题具体分析。总之,没有万能的工具,只有符合生产需求的工具。我们不应对某种工具存在偏见,要综合考虑。同样,当你了解得更多的时候,你会发现这些工具都需要掌握。

FPGA 的应用场景远没有单片机和 ARM 这么多,主要针对单片机和 ARM 无法解决的问题。比如要求灵活高效、高吞吐量、低批量延时、快速并行运算、可重构、可重复编程、可实现定制性能和定制功耗的情况,这些工作只能由FPGA承担。

而相对于出于专门目的而设计的集成电路(Application Specific Integrated Circuit,ASIC),FPGA 具有 3 点优势:

1) 灵活性

通过对 FPGA 编程,FPGA 可以执行 ASIC 能够执行的任何逻辑功能。FPGA 的独特优势在于其灵活性,即随时可以改变芯片功能,在技术还未成熟的阶段,这种特性能够降低产品的成本与风险,在 5G 技术普及初期,这种特性尤为重要。

2) 上市时间缩短

对 FPGA 编程后即可直接使用,FPGA 方案无须经历三个月至一年的芯片流片周期,为企业争取了产品上市时间。

3) 有一定成本优势

FPGA 与 ASIC 的主要区别在于 ASIC 方案有固定成本而 FPGA 方案几乎没有,在使用量小的时候,采用 FPGA 方案无须一次性支付几百万美元的流片成本,同时也不用承担流片失败的风险,此时 FPGA 方案的成本低于 ASIC 的,随着使用量增加,FPGA 方案在成本上的优势逐渐减少,超过某一使用量后,由于大量流片产生了规模经济,因此 ASIC 方案在成本上更有优势

因此,FPGA 通常在数字信号处理、视频处理、图像处理、5G 通信领域、医疗领域、工业控制、云服务、加速计算、人工智能、数据中心、自动驾驶、芯片验证等领域发挥着不可替代的作用。只有掌握了通用的 FPGA 设计方法,才能在 FPGA 独领风骚的领域中大展宏图。

总结

FPGA偏硬件,用语言(verilog、vhdl)或者图形(ip block)描述硬件电路,适合做底层通信时快速的硬协议。个人感觉,今后国家的大趋势应该是恶补底层建筑,应用范围比较广,而且自学难度大,适合投入整个本科或研究生阶段去学。

FPGA在嵌入式领域的应用,只是FPGA广阔应用中很小的一部分。作为学生,FPGA更多的是作为载体,用来帮助你来学习和理解更多专业知识,并且提高自己的动手能力和技术水平。

免责声明:

本文内容部分摘抄自网络,仅供各位参考不做任何商业及其他用途。倘若文章内容侵犯任何人的权益请及时告知我本人进行删除,谢谢配合。

982

982

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?