VCS与Verdi联合仿真简易教程及例子示范

最近在公司实习,最近也恰好在学习Linux下的IC设计环境,涉及到了VCS与Verdi联合仿真等内容,也切身感觉到,和学校学习的内容是如此的不同,此篇便来讲下:

- VCS,Verdi是什么,为何要用VCS和Verdi?

- 用一个简短的例子展示如何在Linux下使用VCS,Verdi对Verilog文件进行功能仿真;

- 一些用VCS,Verdi的提高效率的方式;

1. VCS,Verdi介绍

相信大家都用过Vivado,Quartus等,这里以Vivado为例,他包含了RTL,编译,仿真,综合,看波形,烧板子等,集大成为一体。相比之下,VCS和Verdi就很专一了,VCS专注于编译及仿真,Verdi专注于看波形,仅此而已,安分守己。那Vivado这种功能这么全,工业界直接全用一个Vivado走天下不就行了,为何要大费周折用VCS和Verdi呢?

按我公司老板的话来讲,Vivado其实只能算个写Verilog的(而且还很慢),只不过集成了综合,仿真,看波形等功能,如果要真正做Asic设计,还是得在各个步骤用上用更加专业的软件,用那些在领域中做到顶峰的EDA,对,那就是Synopsys的VCS,Verdi这种(毕竟Vivado的优化大多也只针对于自家FPGA)。首先VCS编译仿真速度极快,效率极高,为大家节约时间,Verdi看波形也十分方便debug,它支持信号追溯,无缝增加信号波形等功能。虽然上手比Vivado难,但学习之后能感受到其美丽之处的。

(注意:仿真包含前仿和后仿,如果单纯的前仿,VCS就绰绰有余了,然后想后仿,那就得需要再用DC (Design Complier) 来“综合”,此篇专注于前仿)

2. VCS,Verdi使用教程

环境:Linux

编写Verilog:Vim or Gedit

编译仿真:VCS

波形查看:Verdi

这里默认VCS和Verdi环境都已配好,需要配环境的朋友可以自行百度~

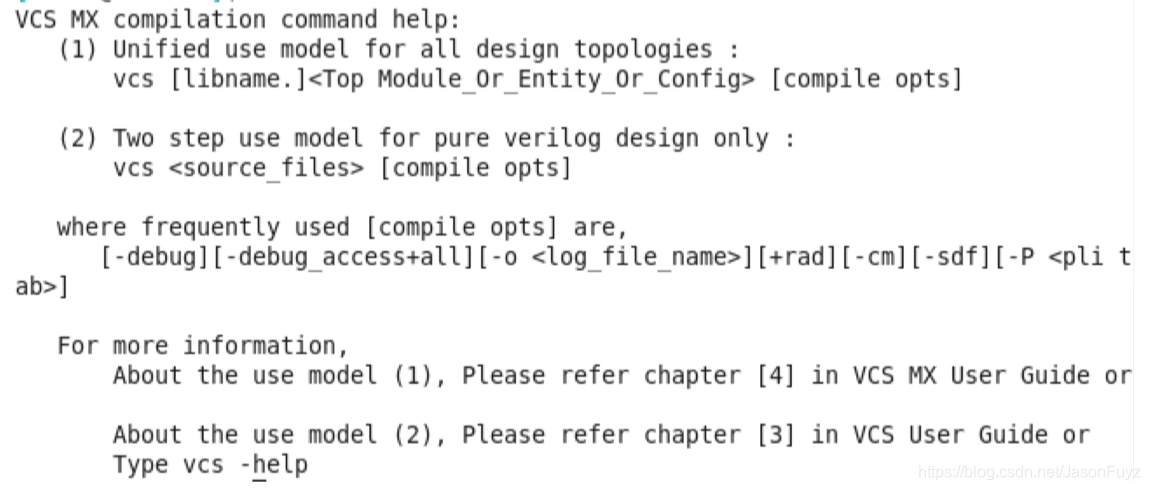

- 可以Terminal输入

vcs,verdi来验证下环境有没有配置成功(若安装成功一般会如下图所示,但出现下图也不能确保环境一定是正确的);

- Terminal输入vcs会显示如下:

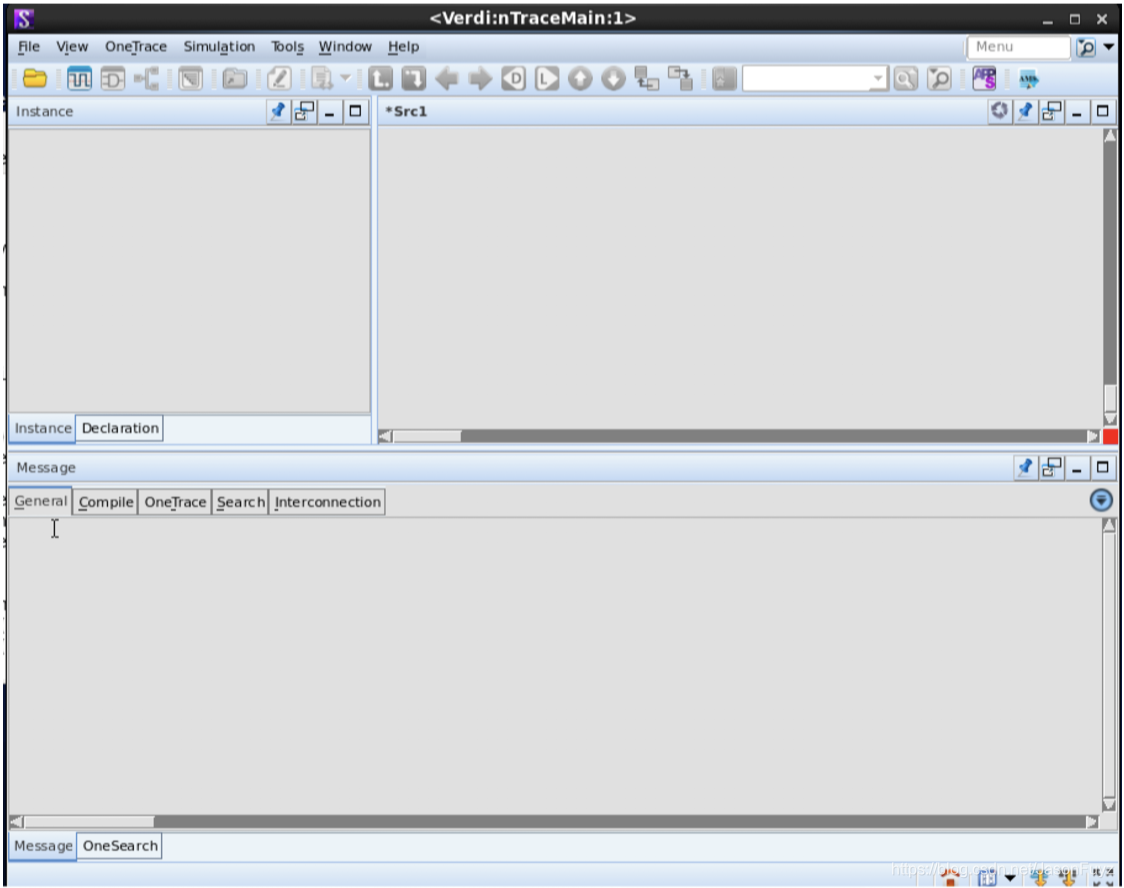

- Terminal输入verdi会直接调用出verdi的GUI

- 这样我们先新建一个计数器的verilog文件以及testbench文件(流程是:在桌面新建Counter文件夹,并在文件夹内新建counter.v,tb_counter.v和timescale.v文件。如果不熟悉可以鼠标操作);

cd Desktop

mkdir Counter

cd Counter

- 至此已完成Counter文件夹建立以及Terminal路径现在在\Desktop\Counter里,我们继续:在文件夹里新建counter.v,tb_counter.v和timescale.v文件,其内容如下:

vim counter.v

module counter(

input clk,

input rst,

output reg [5:0] count

);

always @(posedge clk or negedge rst)

begin

if(!rst)

count <= 0;

else

count <= count + 1;

end

endmodule

vim tb_counter.v

module tb_counter();

reg clk,rst;

wire [5:0] counter;

counter u1(clk,rst,counter);

always #(5) clk = ~clk;

initial begin

clk <= 0;

rst <= 0;

#20;

rst <= 1;

#50;

if(counter != 5)

$display("Failure 1: the counter should be 5 but it is %d",counter);

else

$display("You gotta the right result!");

$finish;

end

`ifdef FSDB

initial begin

$fsdbDumpfile("tb_counter.fsdb");

$fsdbDumpvars;

end

`endif

endmodule

vim timescale.v

`timescale 1ns/10ps

(注意,要VCS与Verdi联合仿真,需要在testbench里面必须加入``ifdef FSDB到endif`的代码,这样才能生成fsdb文件提供Verdi读取,不然不会输出波形)

- 我们已经有了RTL代码了,现在开始用vcs调用这两文件,对counter进行功能仿真;

- 在Terminal输入如下代码并运行

vcs -R -full64 +v2k -fsdb +define+FSDB -sverilog counter.v tb_counter.v timescale.v -l run.log

其中-R表示自动运行仿真,+v2k表示使用Verilog-2001标准,-fsdb表示支持对fsdb相应操作,+define+FSDB相当于在verilog头文件里加上`define FSDB,-sverilog表示支持system verilog,输入.v文件的顺序可以不同(顺序是随意的)-l run.log表示将终端显示的信息在run.log中储存;

-

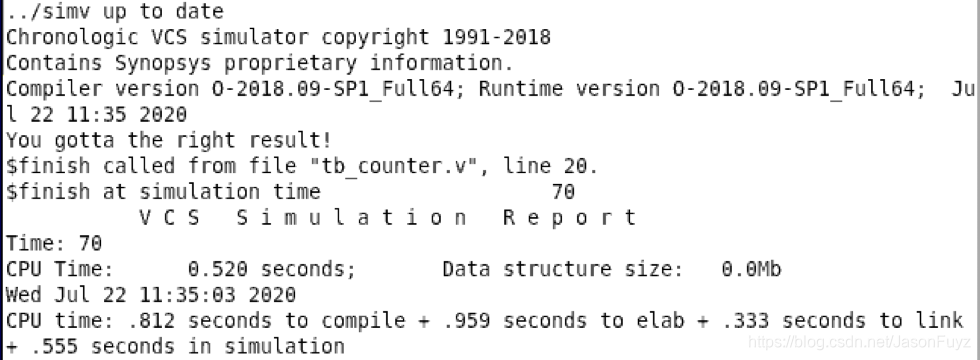

当Terminal显示下图,并在文件夹中出现fsdb文件时,代表vcs已经对counter编译仿真成功了:

-

现在我们可以打开verdi来看波形了,在Terminal输入:

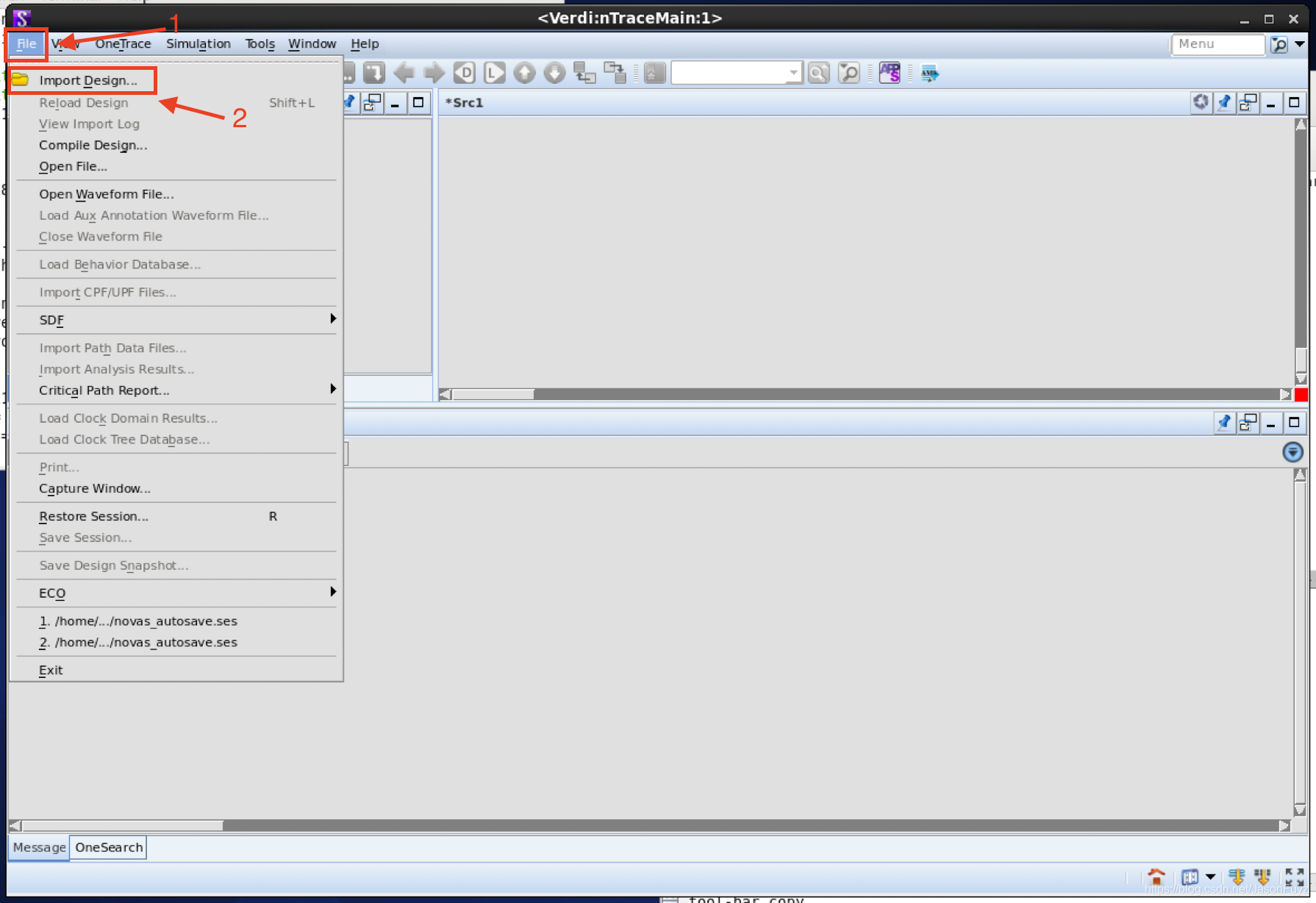

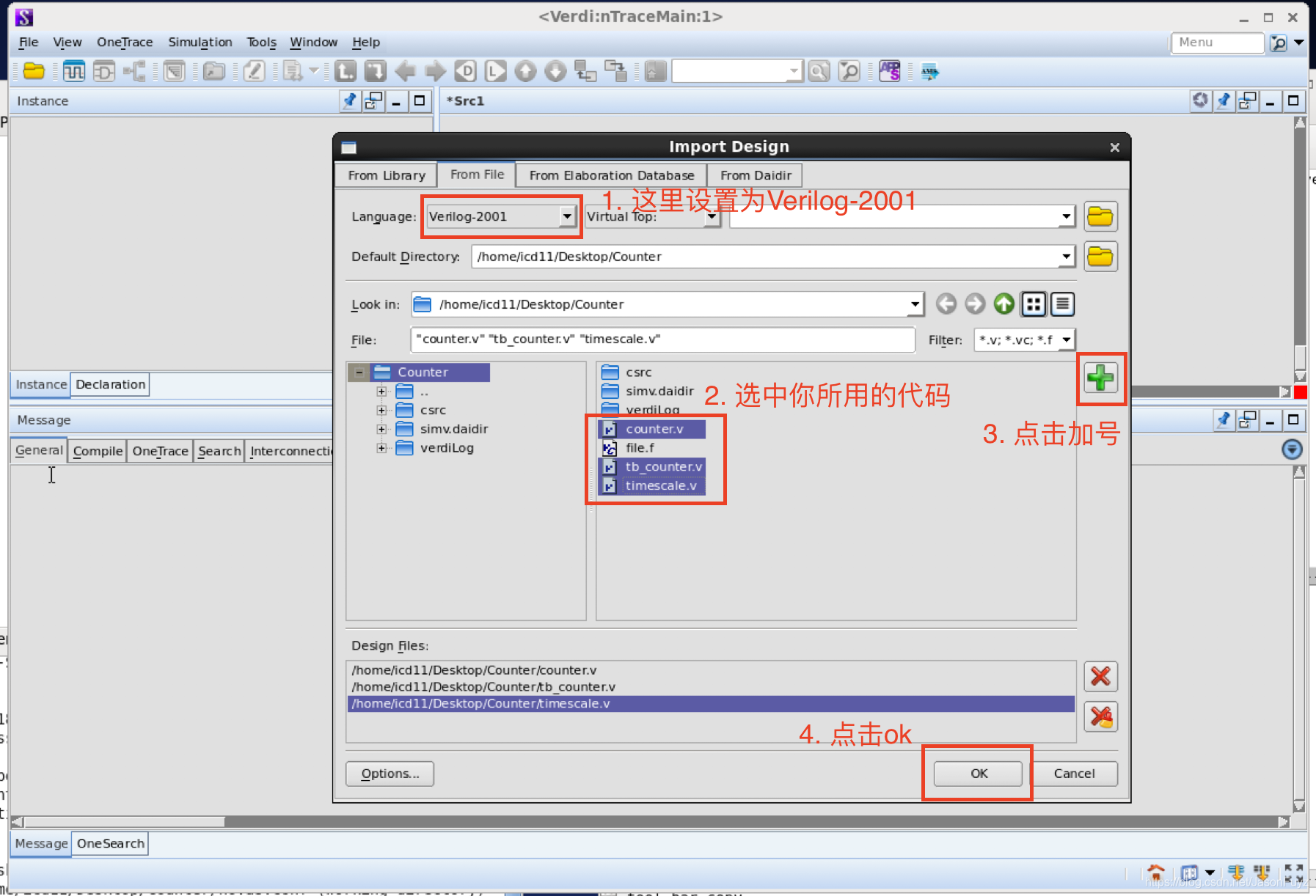

verdi再按下图点击相应选项,它们的意思也很直白,就不解释了;

-

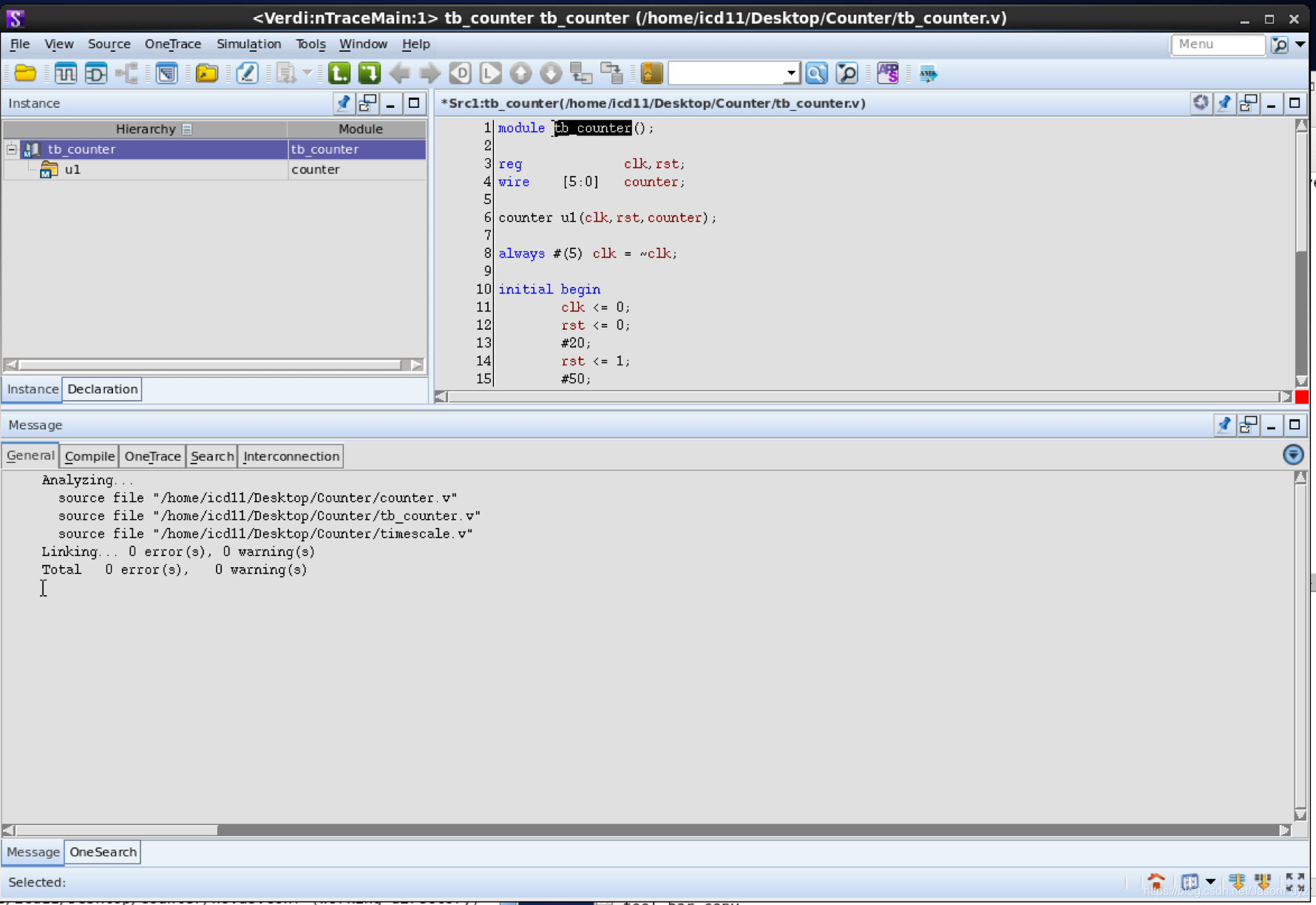

然后按图依次点击,导入代码,然后会变下图所示,恭喜,至此您已经完成了verdi看代码了,开心吧!

-

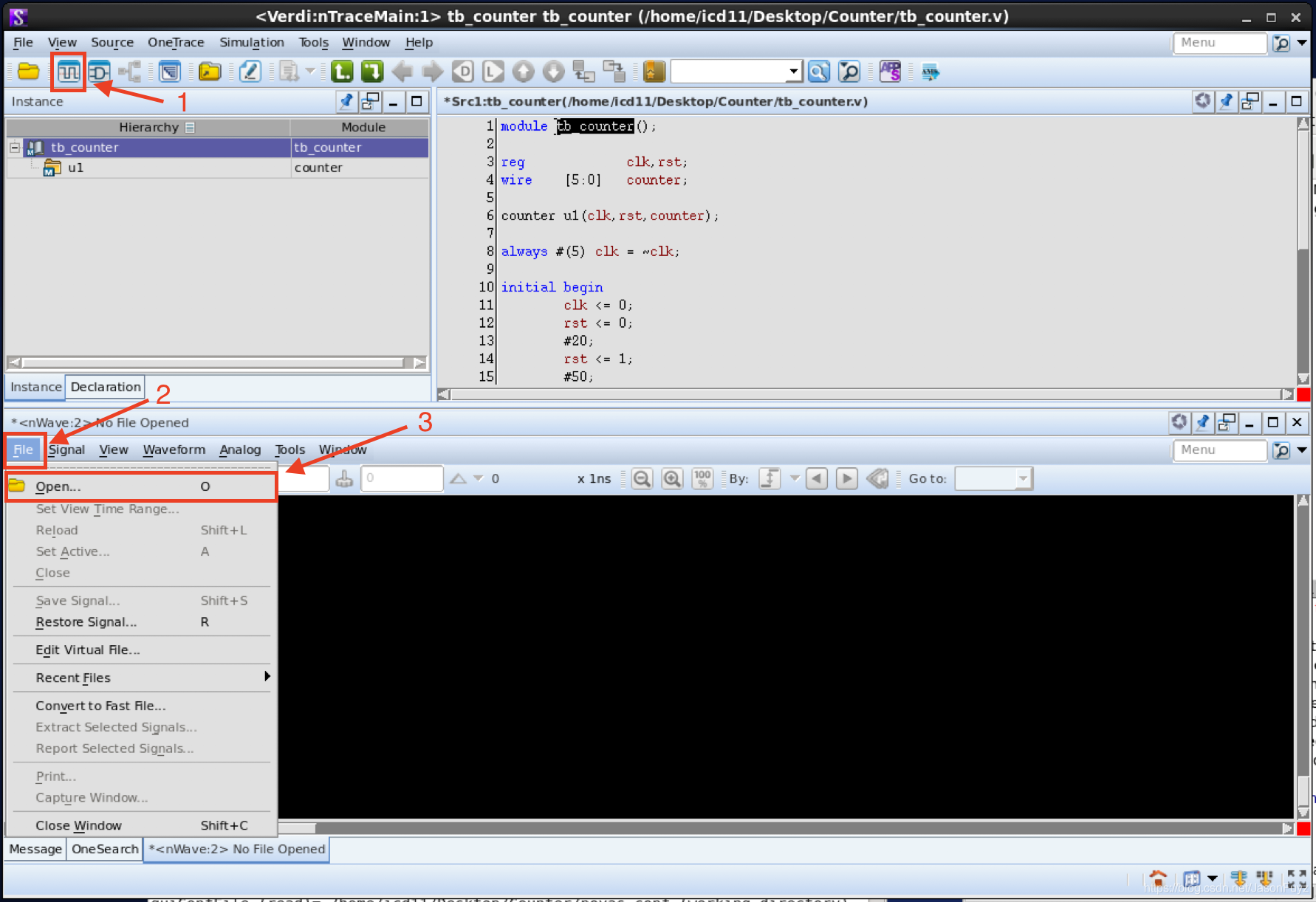

但还没出波形呢,别急,我们现在导入之前生成的fsdb文件。

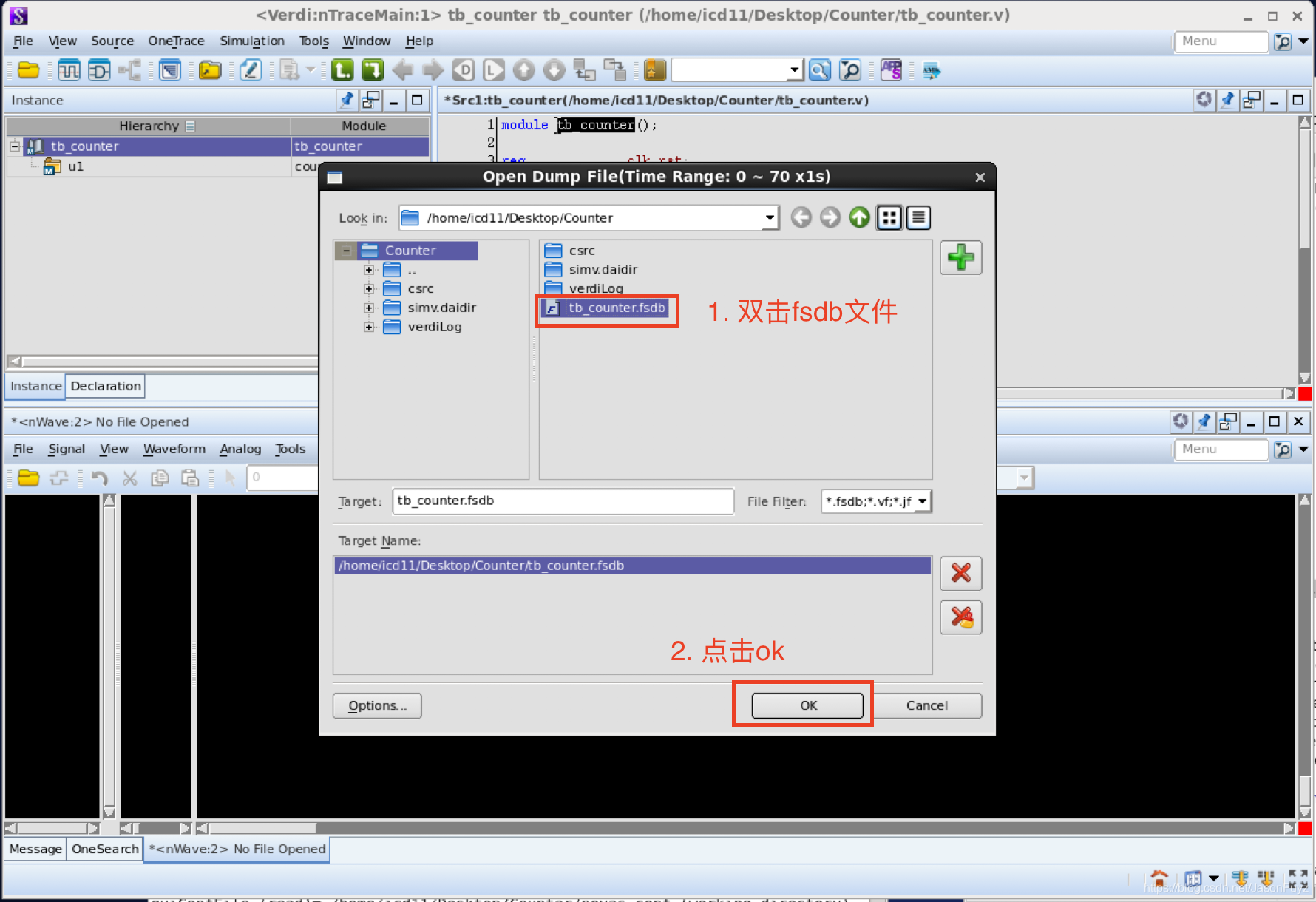

按图依次点击,导入fsdb文件,以显示波形:

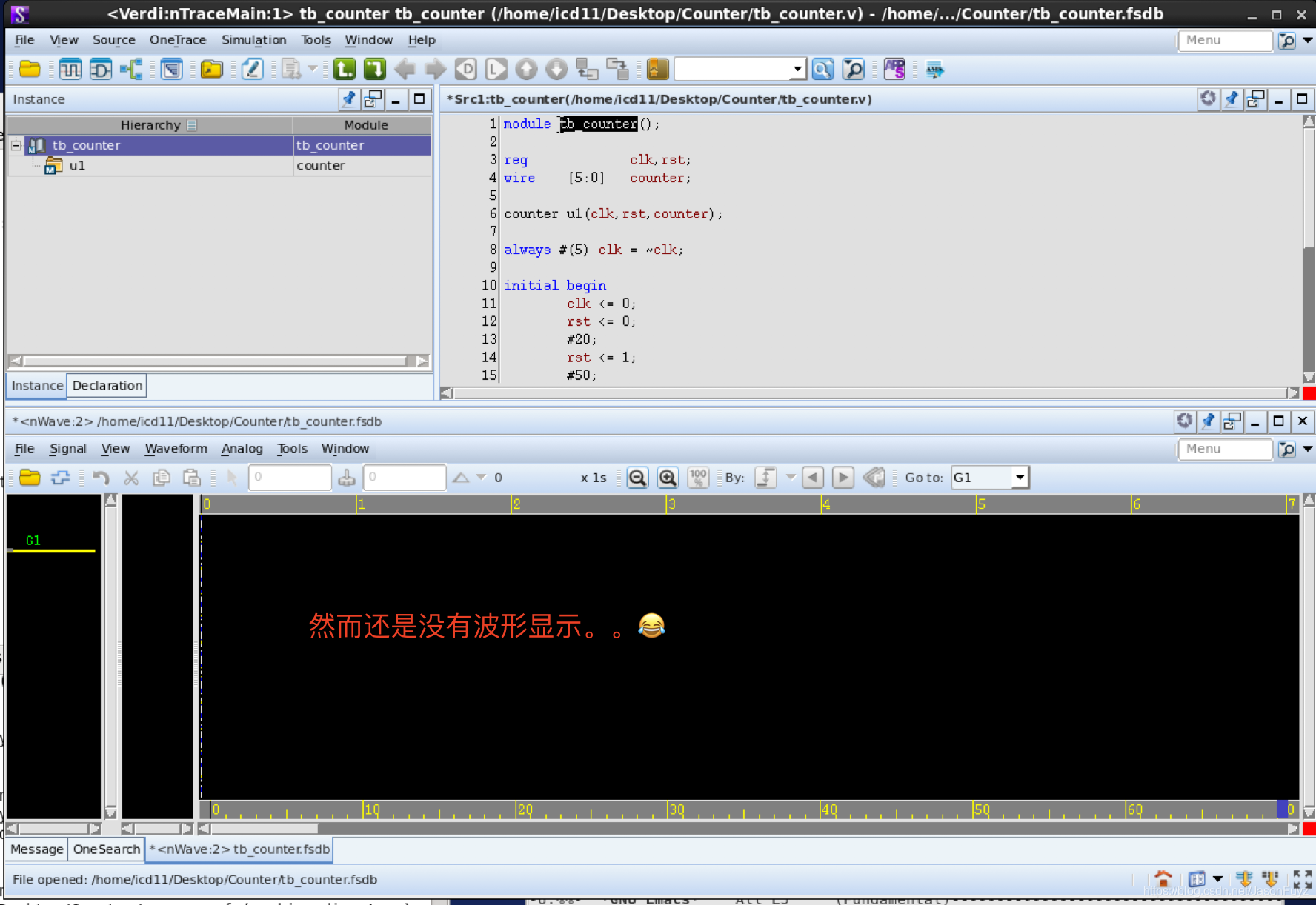

没错,还是没有波形输出,哈哈哈哈 别气馁

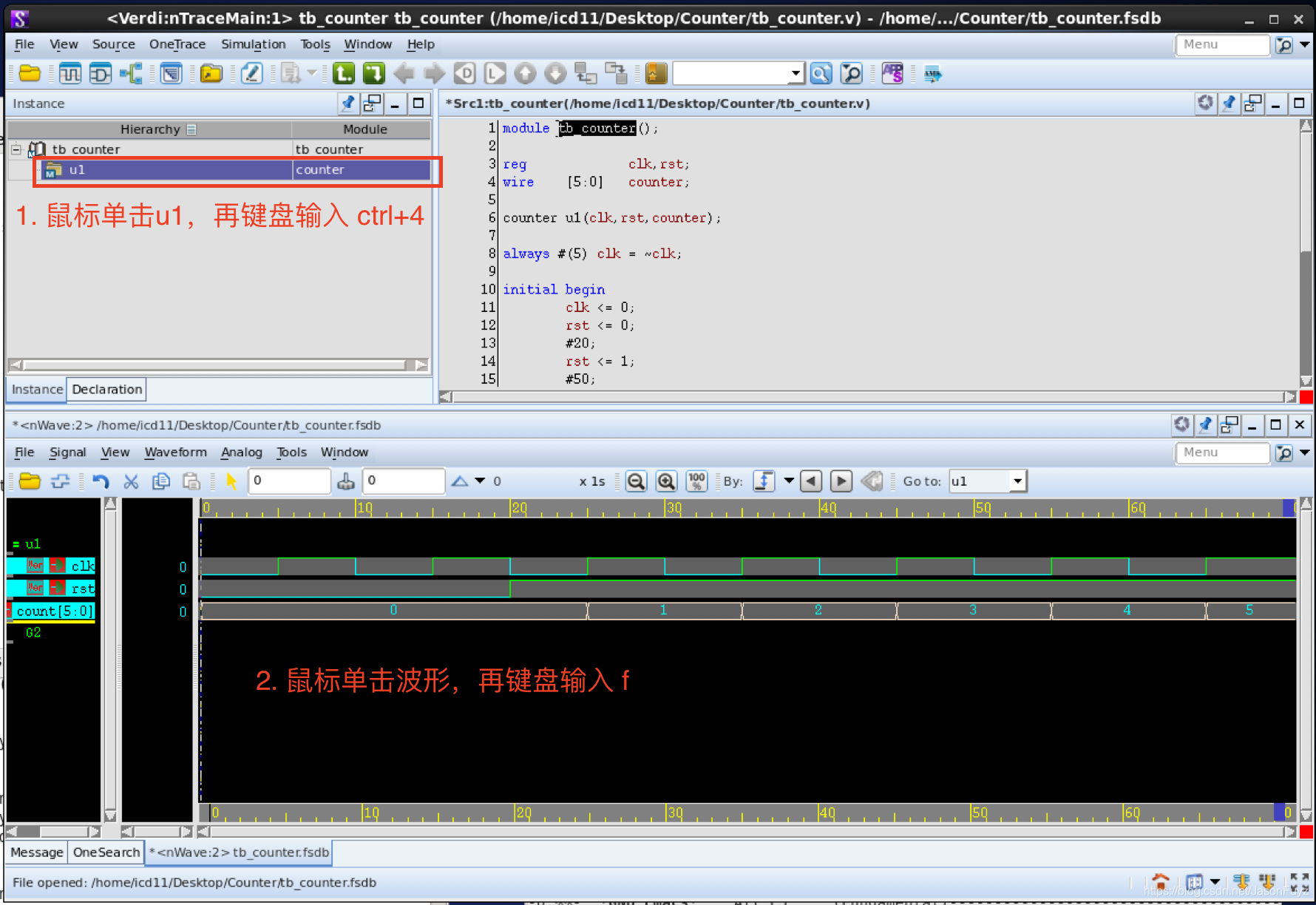

这不是bug,因为我们还没有告诉波形窗口应该看哪个信号的波形,那我们先直接调用这个counter.v里面所有信号的波形吧~ 再按如下操作verdi:

- 这样我们就看到波形啦,对于别的工程也可以依据此例子来做VCS与Verdi联合仿真啦~

至此,我们简单的VCS与Verdi联合仿真例子就大功告成咯,是不是很开心~

可能有些朋友在想,我没看到他们俩一起用有啥方便啊,又得手打命令,又得调来调去,麻烦的很,还没Vivado一半智能。那在下节,我来涉及些VCS和Verdi的一些基本提高效率操作吧~

3. VCS,Verdi提高效率

试想下,我们仅需在Terminal内敲入15个字母的命令,就能迅速自动完成vcs编译仿真甚至调用出verdi,是不是感觉很快,很速度!verdi可以实现代码窗口,波形窗口的联合debug,提高debug效率,是不是很高级,很舒适!

那具体怎么实现呢,请往下看~

-

调用vcs时不用每次都手打 .v文件,使用 .f文件就行,以及用脚本实现调用vcs,具体如下:

在工程文件夹(这里继续用上面Counter的例子)里面新建一个.f文件;

(这里用的vim,不熟悉的可以鼠标新建.f文件并输入内容)

cd Desktop/Counter vim file.ffile.f内容如下

tb_counter.v counter.v timescale.v依旧,这里.v的顺序不重要,只需要将包含的文件写进去便行;

这样,这个file.f文件便代表了工程中的三个.v文件,在调用vcs来前仿时便能这么写了:

vcs -R -full64 +v2k -fsdb +define+FSDB -sverilog -f file.f -l run.log此时,-f代表着你在使用.f文件了,之后如果想再添加.v文件,就在file.f中添加便可~

是不是感觉方便了一些,但感觉方便的还不够啊,以后每次开机岂不都都得重打这个长长的vcs命令,然后在输入verdi?

为了避免如此,我们可以用脚本来做下操作~

首先在Counter文件夹里,新建一个文件,我们叫他runrand(这个可以无后缀的,我这里使用的vim,也能鼠标新建文件)

vim runrand然后在runrand文件输入如下内容(实验室Linux系统的shell是bash,此以bash为例)

#!/bin/bash vcs -R -full64 +v2k -fsdb +define+FSDB -sverilog -f file.f -l run.log verdi然后在Terminal输入如下命令,将runrand转为执行文件:

chmod -x runrand这样,在每次重新启动Terminal时,我们仅需在Terminal输入以下命令便能进行vcs仿真,并调用出verdi了~

(实验室Linux系统的shell是bash,此以bash为例)

source runrand是不是方便了很多~

(如果不想直接调出verdi可以在runrand里将verdi这一行去掉)

-

Verdi的优点体现

不知道大家之前是不是也遇到过这种困扰,使用Vivado或者Modelsim看波形时,为了增加某几个信号的波形,又得重新仿真一遍(贼耗时间);为了追踪一个信号它在某几个时刻的变化原因,需要对着波形图琢磨几遍(贼耗时间)…

那么Verdi在这块都已经全部解决,在Verdi看增加信号波形无需再次仿真,追踪信号只需要在代码窗口里点击相应信号便能看到它是由哪些信号决定的。

那具体操作如下:

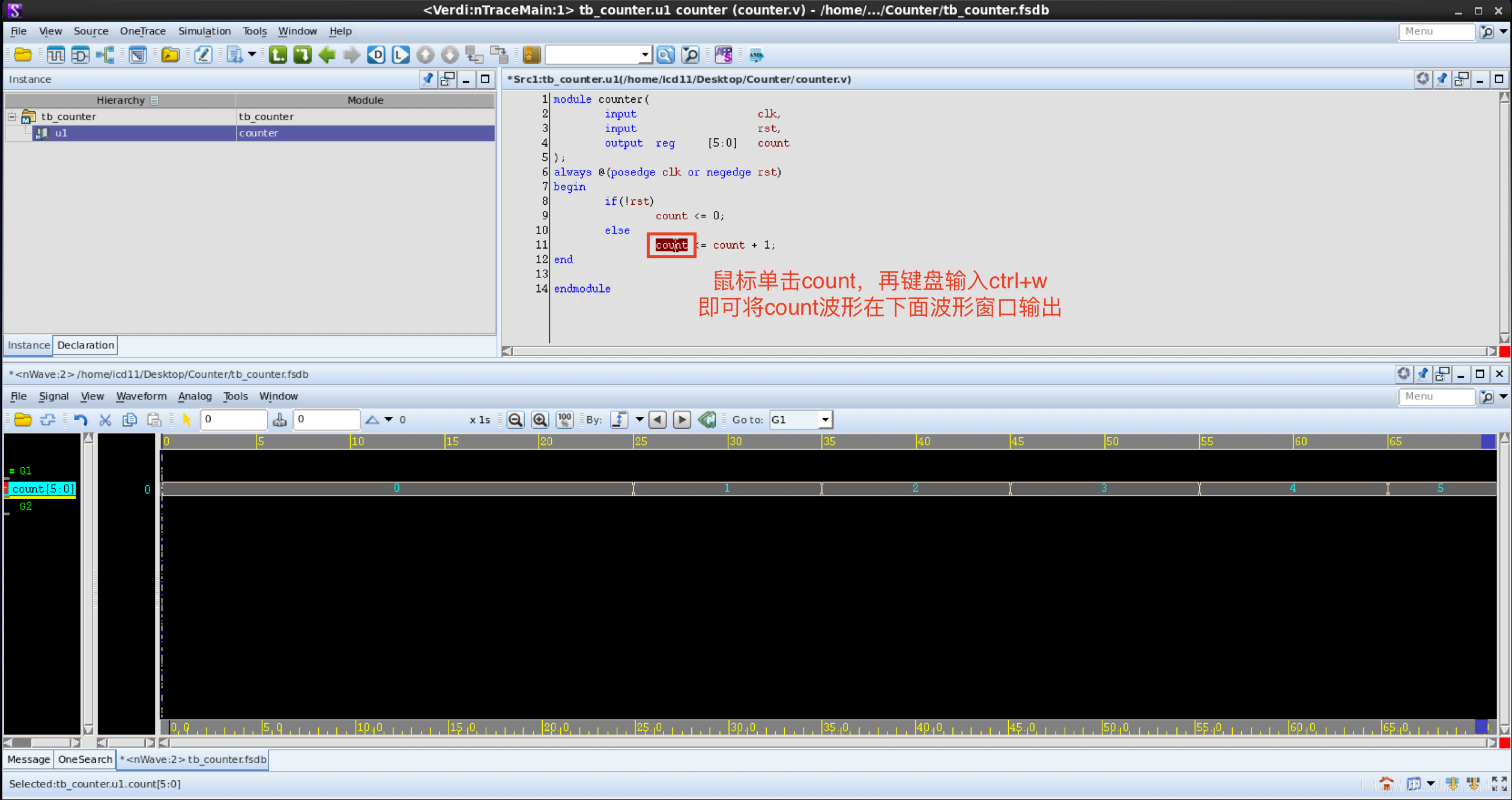

- 在导入.v文件以及.fsdb文件后,如果我们要增加某信号波形,可以鼠标单击代码窗口的对应信号,然后再键盘输入

ctrl+w,这样该信号的波形便直接导入波形窗口并显示了,不需要再次仿真,是不是超级方便!!!

- 在导入.v文件以及.fsdb文件后,如果我们要增加某信号波形,可以鼠标单击代码窗口的对应信号,然后再键盘输入

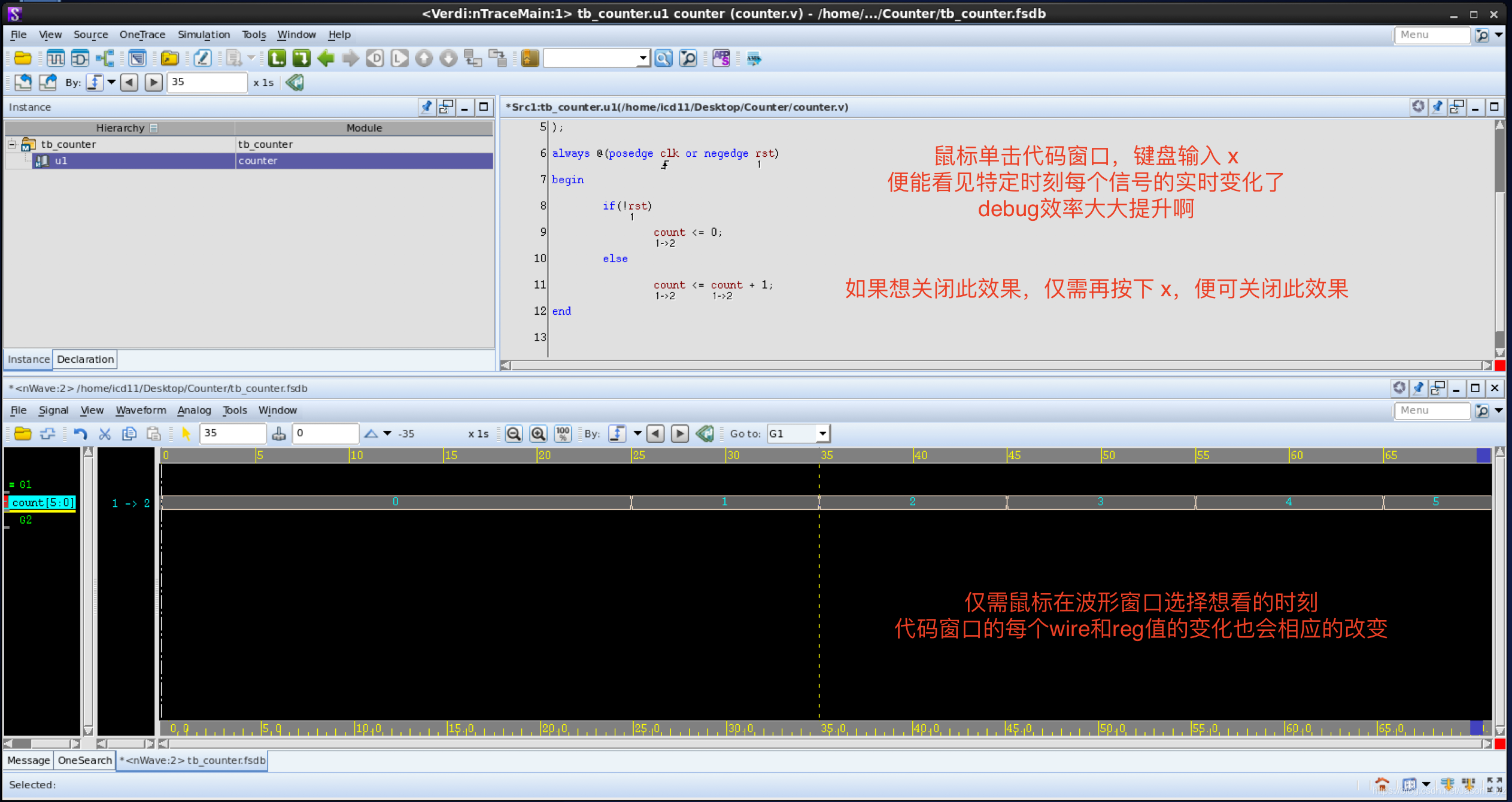

- 为了让debug更加快捷,我们可以在代码窗口单击键盘的x键,以显示出每个wire和reg在特定clk时的值的变化,再也不需要盯着波形来回看了!

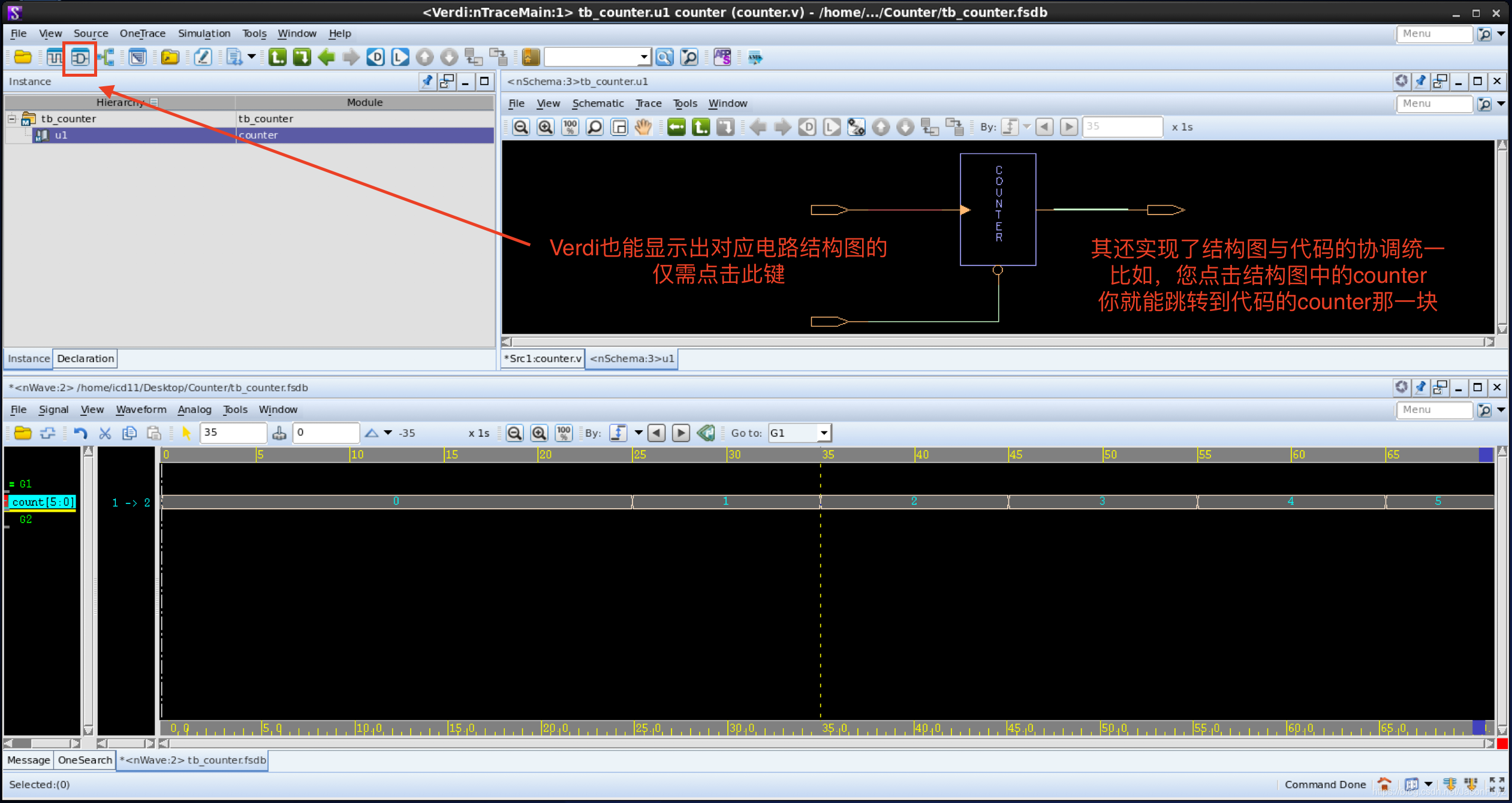

- verdi也能生成.v文件对应的电路结构图,具体如下图所示:

- verdi还有很多快捷键,比如

ctrl+4将.v文件中所有信号波形全部导入波形窗口,在波形窗口按f自动适配波形大小,按z缩小波形,按Z放大波形,等等,许多便捷操作,以及用命令行或者脚本直接verdi读取fsdb文件并显示等,这些大家可以自行上网查询~ - 这里再举个命令行直接调用verdi并直接导入.v文件,.fsdb文件的操作。同时我们也能像先前生成runrand脚本文件那样,创建一个新脚本文件调用下面的命令,从而提高效率~

verdi -ssf tb_counter.fsdb -2001 -sverilog tb_counter.v counter.v

- 欢迎大家找到更棒的快捷键或命令后与我分享,一起来完善此教程~

总结

十分感谢看到这里,教程就到此为止了,相信大家也已经能自主应用VCS和Verdi去对自己工程进行前仿以及看波形了。教程里面涉及的较少,如果想更加深入了解VCS和Verdi,建议去品读synopsys的官方指导文档,同时这也有一个良心UP主的VCS Lab教程视频,有兴趣的朋友也能看看,会让您对VCS有更深地理解。

https://www.bilibili.com/video/BV1Ab411r75o,这是VCS Lab1,还有Lab2,3,直接在UP主主页便能看见~

本文详细介绍了VCS与Verdi在Linux环境下进行IC设计的功能仿真过程,包括环境搭建、代码编写、编译仿真及波形查看。通过实际例子展示了如何高效使用VCS进行编译和Verdi进行波形分析,强调了其相较于Vivado的优势。

本文详细介绍了VCS与Verdi在Linux环境下进行IC设计的功能仿真过程,包括环境搭建、代码编写、编译仿真及波形查看。通过实际例子展示了如何高效使用VCS进行编译和Verdi进行波形分析,强调了其相较于Vivado的优势。

2278

2278

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?