1.问题主干:

用Verilog HDL门级描述方式描述如下图所示的电路。

2.问题分析:

由上述电路图可以分析得到,共有4个三输入与门(其中有一个只有两个输入,实际是而输入与门),一个四输入或门,以及两个反相器。

门级的电路描述风格是不需要知道关系表达式的,在已知电路的前提下,通过简单的调用基本门ip即可实现这个电路的描述,并且代码与电路描述是一一对应的。

在代码中实现这个门级电路比较简单,反相器:not(a_n,a);三输入与门:and(out,a,b,c);三输入或门:or(out,a,b,c,d)。

3. 程序内容:

.v文件:

`timescale 1ns / 1ps

//

// Company:

// Engineer: jefferym

//

// Create Date: 2022/03/18 10:40:31

// Design Name:

//

module gate_test(D0,D1,D2,D3,S1,S2,Z);

input [0:0] S1,S2,D0,D1,D2,D3;

output [0:0] Z;//默认这些数据类型为wire,在基本门的表述中,输入输出都应该是wire

wire [0:0] T0,T1,T2,T3;//中间变量

wire [0:0] S1_N,S2_N;

not not1(S1_N,S1),

not2(S2_N,S2);

and and1(T0,D0,S2_N,S1_N),

and2(T1,D1,S1_N,S1),

and3(T2,D2,S2_N,S1),

and4(T3,D3,S2);

or or1(Z,T0,T1,T2,T3);

endmodule

tb文件:

`timescale 1ns / 1ps

module tb(Z);

output [0:0] Z;

reg [0:0] S1,S2,D0,D1,D2,D3;//下面将对这些输入进行在过程语句中进行赋值,因此必须为reg

gate_test my_gate_test(D0,D1,D2,D3,S1,S2,Z);//这里可以写作.D0(D0),也可以按顺序赋值,这样必须严格按照顺序来写

reg [5:0] cnt=6'b1;//计数变量,用于产生六位的测试信号

initial begin

D0=0;D1=0;D2=0;D3=0;S1=0;S2=0;

for(cnt=1;cnt<64;cnt=cnt+1)

begin

#2 {S2,S1,D3,D2,D1,D0}=cnt; //这里把s2,s1放在高位,D0放在低位,这样方便观察测试波形;

end

end

endmodule

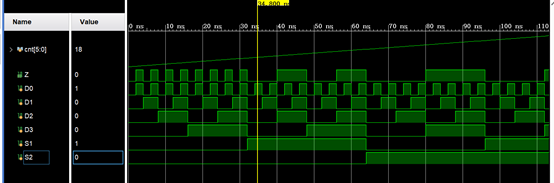

4. 实验结果:

和逻辑运算的结果一致。

357

357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?