-过程连续赋值:

过程赋值:将值赋给寄存器,之一直保存在寄存器中,直到另一个过程赋值将另外一个值存放在该寄存器中;

过程连续赋值:允许在有限时间段内将表达式的值连续地加到寄存器或线网。左边只能是寄存器或寄存器组。

-assign和deassign:

-force和release:可改写(覆盖)寄存器、线网上的赋值。

或者

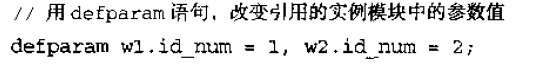

-defparam:在任意模块调用中改变参数值。

或者

-条件编译和执行:某部分代码只有设置了特定的表之后才能被编译。编译指令(`ifdef, `ifndef, `else, `endif)

-条件编译:

-条件执行:

-时间尺度:

![]()

-常用系统任务:

-文件输出:

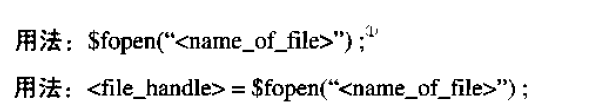

打开文件:

写文件:

关闭文件:

![]()

-显示层次:

-选通显示:

-随机数生成:

-用数据文件对存储器进行初始化:

-值变转储文件(VCD):

1495

1495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?