本文转载自《路科验证》,向分享知识的大佬致敬!瑞斯拜~~~

1. 另一盒糖的故事

想象你正在做晚餐,需要一些糖。你会怎么做?把手伸到冰箱旁边的柜子里,抓住盒子。糟糕,糖昨晚已经用完了,所以没有盒子。因此,你需要去杂货店再买一些。

SystemVerilog程序包就像杂货店一样,是一个存放了很多东西,每当你在家里找不到东西时就会去的地方(这句话很关键,细细品味)。

2. 什么是程序包

程序包中涵盖了你想在模块之间共享的定义。可以包括:参数,枚举类型,结构,类型定义(typedef),类,甚至是任务或函数。

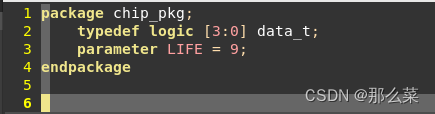

这里有一个程序包,其中定义了数据类型和参数。

3. 编译一个程序包

当你使用Questa进行编译时,代码将在工作库中转换为二进制形式。相较于原始代码,编译器可以更快地读取二进制版本,这就是为什么我们要导入程序包而不是包含它们的原因。 UVM程序包有70,000行,但是编译版本几乎是即时导入的(这里是一个关键点,使用中格外注意)。

4. 导入一个程序包

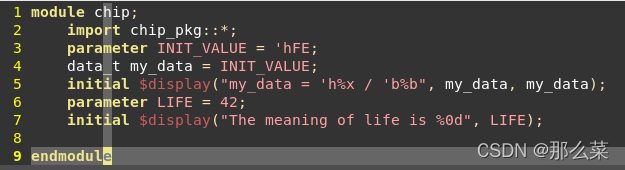

模块通过导入import 关键字,来访问已编译的程序包代码。这里给了一个声明一些参数和变量并显示参数的芯片模块module。

5. 运行原理解析

5.1 程序包商店规则

SystemVerilog编译器在本地module 内部域中查找名称。如果找不到它们,则转到程序包chip_pkg中寻找。

当编译此模块时,(1)通配符import语句会告诉编译器该包是查找定义的地方(2)编译器不会从包中引入所有名称,否则那就是像把整个杂货店带回家。

模块定义参数INIT_VALUE。对于“my_data”的声明,编译器需要弄清楚“data_t”和“INIT_VALUE”的含义。编译器始终从搜索本地范围(即芯片模块)开始,并成功在这里找到INIT_VALUE。但是,这里没有data_t。只有这样编译器才会查看程序包。编译器成功在芯片程序包中找到data_t的定义!

你可以证明在本地范围之后程序包也被搜索了。下一个代码块定义了一个参数LIFE并进行打印。在$display()语句中,编译器需要知道什么是“ LIFE”。由于你只是在本地声明了它,因此即使其中有一个具有相同名称的参数,编译器也不会在chip_pkg中查找。本地定义与包中的参数不冲突,因为从未导入chip_pkg :: LIFE。

5.2 最低限度原则

只有在本地作用域中找不到新定义时,SystemVerilog才会从包中引入新定义。这是为什么呢?如果包中的每个名称都被立即导入,则很有可能其中一个包中的名称也许与本地范围内的一个名称冲突,例如芯片模块。最好是只引入最少的名称,而不要太多。这样做,最保险。该模块定义了一个叫LIFE的参数。在你最喜欢的模拟器中运行此代码,找出LIFE的意义。因为本地重新定义了 parameter LIFE = 42, 故打印输出数字42。

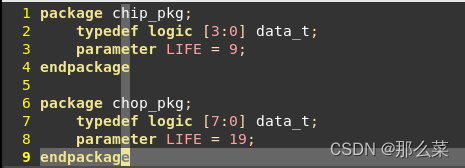

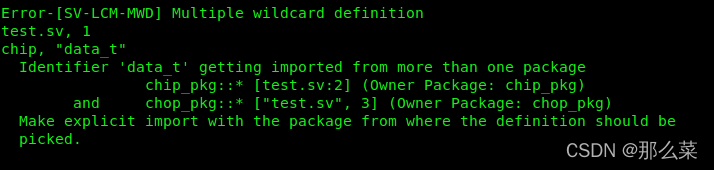

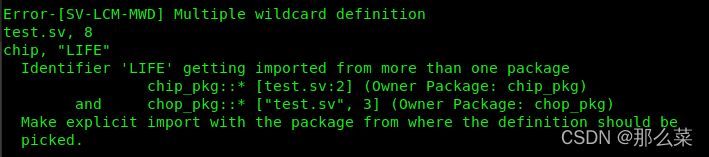

如果模块将data_t类型定义为8 chip_pkg显式获取LIFE的值?如果在chip_pkg和chop_pkg中都定义了一个新参数,并且都导入了该参数,该怎么办?会发生什么?如果我告诉您答案,您将永远不会记住它。请您自己尝试,花时间,发现真相。

最后,延伸一点。我们在搭建复杂的验证平台过程中,会遇到编译错误。该错误显示:有某个变量类型找不到定义。 可是,我们明明在某个 *_pkg.sv 中 定义了,而且查看 VCS 的编译日志文件,确实找到了该*_pkg.sv 已经被 parse 。大佬的文章也提醒我们:杂货店,不是全部搬回家的。用什么再去找什么,都拿在手边太重了。

本文详细介绍了SystemVerilog中的程序包概念,包括程序包的作用、如何编译和导入程序包,以及import关键字的工作原理。文章通过比喻解释了程序包类似于杂货店,用于存储共享的定义,如参数、类型等。强调了编译后的程序包能提高读取速度,并解释了import关键字按需引入避免冲突的原则。此外,还讨论了在不同作用域中查找变量和类型定义的规则。

本文详细介绍了SystemVerilog中的程序包概念,包括程序包的作用、如何编译和导入程序包,以及import关键字的工作原理。文章通过比喻解释了程序包类似于杂货店,用于存储共享的定义,如参数、类型等。强调了编译后的程序包能提高读取速度,并解释了import关键字按需引入避免冲突的原则。此外,还讨论了在不同作用域中查找变量和类型定义的规则。

1515

1515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?