----------------------------------------------------------------------------

最近由于考试、项目以及个人原因的一些事情停更了一段时间,后面可能等到6月中旬才能恢复每日一更。

------------------------------------------------------------------------------

集成电路版图物理验证(PV)

设计规则检查(Design Rule Check,DRC)

天线效应检查

版图原理图一致性检查(Layout Versus Schematic,LVS)

电气规则检查(Electrical Rule Check,ERC)

Signoff 工具:Calibre,ICV

版图的Merge

是在物理验证(PV)之前,布局布线(PR)之后的操作。

不用完整的GDS进行布局布线。而是会用抽象的层次进行布局布线,这样布局布线工具吐出的GDS不是完整的GDS,里面会缺失某些东西,这样的GDS不能交给Foundary进行生成,也不能把这样的GDS拿去做Signoff的DRC和LVS的检查。里面的层次是缺少的,所以也肯定过不了。所以我们使用Layout Merge去把里面抽象的层次替换成完整的层次,即完整的GDS。

PR的时候用的是FRAM view,而完整的GDS是CEL view。

FRAM view:抽象化的版图物理信息(只有单元大小,端口名称,端口位置等简单的PR所需的物理信息)

CEL view:版图物理数据

集成电路版图设计规则(Design Rule)

Foundary针对特定工艺专门制定的强制性版图设计检查的一些规则的集合(不同的工艺有不同的设计规则),综合考虑电学性能和可靠性限制,按照芯片加工过程所需的一系列限制来制定,目的是描述版图中几何图形之间的关系,使其符合具体工艺的要求

制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层mask套准偏差可能带来的问题,尽可能地提高IC制备的成品率。

常见的几种:

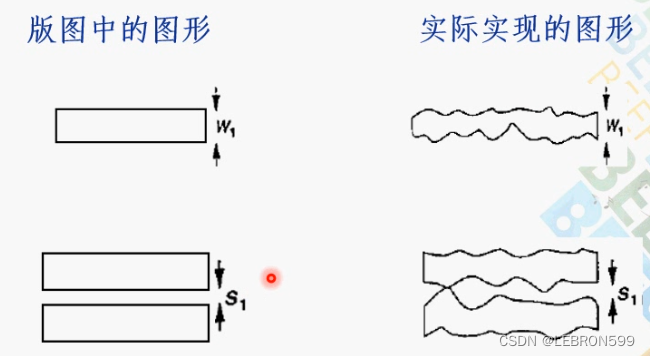

(1)最小宽度和间距

实际实现的图像是不规则的,弯弯扭扭的,为了防止短路和其他效应,要设置最小宽度和间距。

(2)最小交叠(minOverlap)

(3)最小密度

金属线的成形,是通过刻蚀工艺完成的,稀疏的金属线比紧密的金属线更容易被过刻蚀,所以对最小金属密度有要求,解决方案:Metal fill,也就是加dummy。

(4)最大密度

芯片制造过程的金属线成形过程中,在氧化层上淀积一层金属,刻掉不需要的部分,再在被刻掉的部分上氧化出与金属等高的氧化层,接下来需要做一次化学机械抛光(CMP)来平坦化芯片表面(每一层都要做平坦化)

氧化层和金属对CMP的反应程度是不一样的,金属更容易被CMP刻蚀掉,所以金属的密度不能太大,否则被CMP刻蚀掉形成的凹槽过大

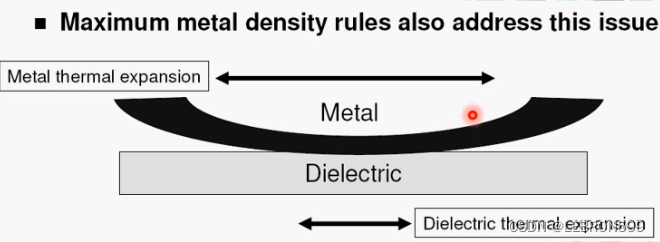

(5)最大宽度

由于金属和氧化层的热膨胀系数不同,氧化层上的金属可能会产生翘起现象,金属线越宽越容易发生这种现象,所以要控制金属宽度。

解决方案:挖槽,多段金属并联

设计规则检查(DRC)

版图完成后需要做物理验证(physical verification),首先是对版图进行设计规则检查(DRC),DRC的主要目的是检查版图中所有因违反设计规则而引起的潜在断路、短路或不良效应的物理验证过程。DRC检查的方法是将版图中所有几何图形与设计规则规定的尺寸,间距进行比较,并将所有违反规则的地方通过EDA工具以醒目的标识反标到版图中告诉设计者,设计者通过这些表示判断、修改错误。

设计规则检查的必要性:

Innovus在PR阶段也会考虑DRC,但Innovus不是Signoff级的工具。其设计规则来自于tech file文件,另外使用的是FRAM View。

Signoff级的PV工具是Calibre或者ICV,输入的是完整且更加严格的drc规则文件以及Layout Merge之后的完整GDS。

DRC-----ing

对版图做DRC之前,需要准备两个文件:

完整的版图GDS文件,一般通过版图的Merge得到,且做DRC之前要对版图进行编辑

DRC规则文件(由代工厂提供),做DRC之前要对此文件进行一定的修改

需要对DRC文件进行更改的地方:

set TOPMETAL 8 ;#valid value is:{10,9,8,7,6,5}

-M1-M6,TM1,TM2

#DEFINE UTM NO //valid value is:{YES,NO}

-//If top metal is layer TM2(layer122,top metal with regular thickness),then please use default value NO

-//If top metal is layer MTT2(layer231,top metal with ultra thickness),then please change it into YES

#DEFINE SRAM_GT_DIRECTION V //valid value is:{H,V}

-//SRAM GT direction selection

-//Default is V(vertical),But it can also be changed into H(horizontal)

可选设置

LAYOUT PRIMARY

LAYOUT PATH

LAYOUT SYSTEM

DRC RESULTS DATABASE

DRC SUMMARY REPORT

TEXT DEPTH

不用修改的内容

PRECISION //输入数据的精度

RESOLUTION //工艺可识别的最小步进单位

FLAG OFFGRID YES //在Summary Report里显示不在格点上的版图的坐标

- // Allow Calibre to locate offgrid area,base on the setting of PRECISION and RESOLUTION。Similarly,it also report a warning to summary file。

FLAG ACUTE YES //在Summary Report里显示锐角的版图的坐标

- // Allow Calibre to locate acute angle area,but it only report a warning to summary file,can not output error to DRC results database。

FLAG SKEW YES //在Summary Report里显示不是45度的斜线的版图的坐标

- // Allow Calibre to locate skew line(do not include 45 degree line)。Similarly,it also report a warning to summary file。

FLAG NONSIMPLE YES //在Summary Report里显示非简易多边形版图的坐标

- // Allow Calibre to locate non-simple polygon。Similarly,it also report a warning to summary file。

DRC规则文件的解读见:DRC规则解读-CSDN博客

640

640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?