FPGA编程入门

引言:

在数字电路的神奇世界里,我穿越逻辑门的迷宫,跟随电子的舞动,探索着信息的奇妙旅程。这不是科幻小说中的场景,而是我在Verilog编程的大门中踏入的数字王国。如果你曾在世界的另一端寻找着门电路的谜题,或者在组合电路的森林中迷失过,那么这篇文章将为你打开一扇通往数字探险的大门。

~

我将结合在线Verilog编程网站的实践练习,操刀Logisim软件的逻辑仙境,还要在Quartus软件的数字画布上留下我的足迹。从门电路的神秘起点,经过组合电路的蜿蜒征程,一路追逐时序电路的星辰,这篇文章将带领你踏上一场数码冒险之旅。

~

但这不仅仅是一场枯燥的技术探险,而是一次充满趣味和创造力的数字探索之旅。我将不仅仅是编程和设计,更是在电子的舞台上扮演着创意的导演。在这个数字化的舞台上,我将见证门电路的独角戏、组合电路的相互协奏,以及时序电路的精妙编织,所有这一切都交织成一幅令人惊叹的数字交响乐。

~

准备好了吗?让我插上电子的羽翼,携手Verilog编程的魔法精灵,一同展开这场引人入胜的数字冒险!

~

希望你在本次学习过后,能够有一定的收获!!!

~

弱小,并非服从恐惧的理由。——虞姬

~

冲啊!!!! ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶

一. 在线Verilog编程网站学习:

1. 门电路练习

《知识分析》

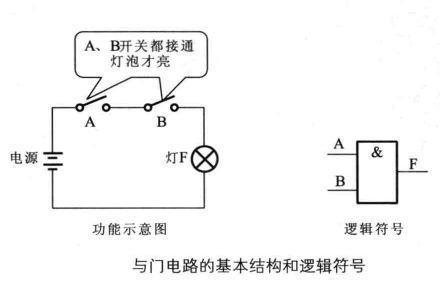

与门(AND Gate):

与门是一种基本的数字逻辑门,它具有两个或多个输入和一个输出。与门的输出只有在所有输入信号都为高电平时才为高电平,否则为低电平。与门的符号通常用一个大写字母“AND”表示,并在其左侧放置输入端口的数量。与门的真值表如下:

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

与门的逻辑代数表达式为Q = A * B,其中 * 表示逻辑与运算。

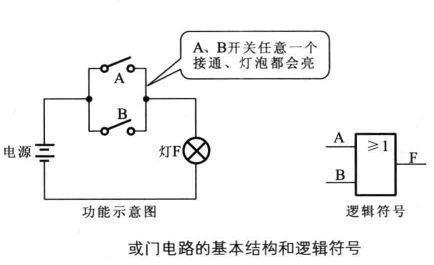

或门(OR Gate):

或门是另一种基本的数字逻辑门,它同样具有两个或多个输入和一个输出。或门的输出只有在至少一个输入信号为高电平时才为高电平,否则为低电平。或门的符号通常用一个大写字母“OR”表示,并在其左侧放置输入端口的数量。或门的真值表如下:

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

或门的逻辑代数表达式为Q = A + B,其中 + 表示逻辑或运算。

非门(NOT Gate):

非门是最简单的逻辑门,它只有一个输入和一个输出。非门的输出与输入相反,即当输入为高电平时,输出为低电平,反之亦然。非门的符号通常用一个圆圈表示,并在其左侧放置输入端口。非门的真值表如下:

| A | Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

非门的逻辑代数表达式为Q = ~A 或 Q = A’,其中 ~ 或 ’ 表示逻辑非运算。

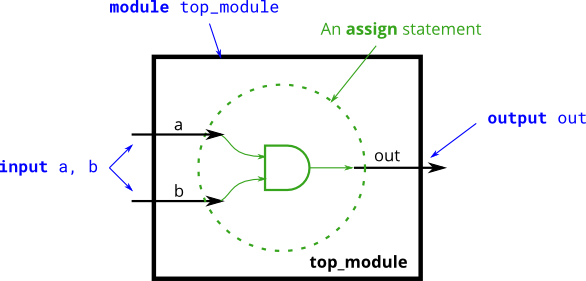

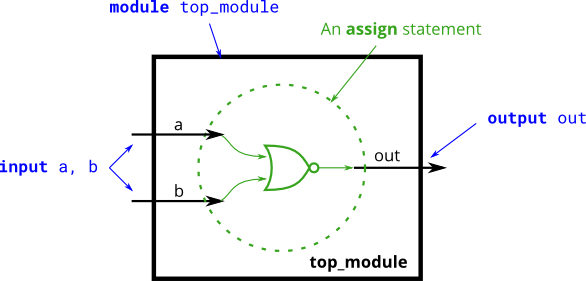

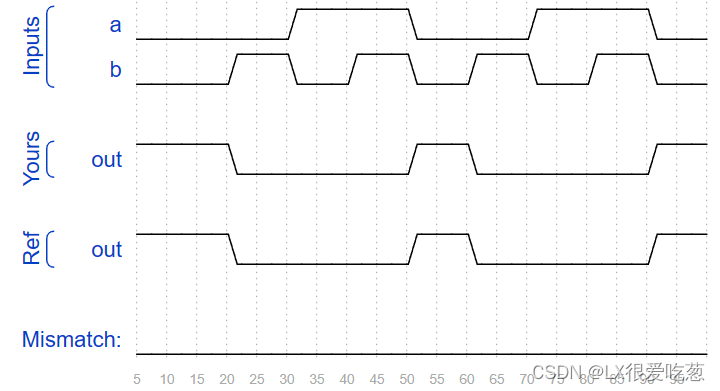

1.1 例题1: [Andgate]

题目描述

Create a module that implements an AND gate.

This circuit now has three wires (, , and ). Wires and already have values driven onto them by the input ports. But wire currently is not driven by anything. Write an statement that drives with the AND of signals and .

a``b``out``a``b``out``assign``out``a``bNote that this circuit is very similar to the NOT gate, just with one more input. If it sounds different, it’s because I’ve started describing signals as being driven (has a known value determined by something attached to it) or not driven by something. are driven by something outside the module. statements will drive a logic level onto a wire. As you might expect, a wire cannot have more than one driver (what is its logic level if there is?), and a wire that has no drivers will have an undefined value (often treated as 0 when synthesizing hardware).

Input wires``assign

题目分析

题目要求创建一个实现与门(AND gate)的 Verilog 模块。这个与门有两个输入信号,分别为

ina、inb,以及一个输出信号out。其中,in1和in2已经由输入端口赋值。题目要求使用 Verilog 语句来将out的值设为in1、in2两者的与操作结果。

解题代码

module top_module(

input a,

input b,

output out );

assign out = a & b; // 逻辑与门的实现

endmodule

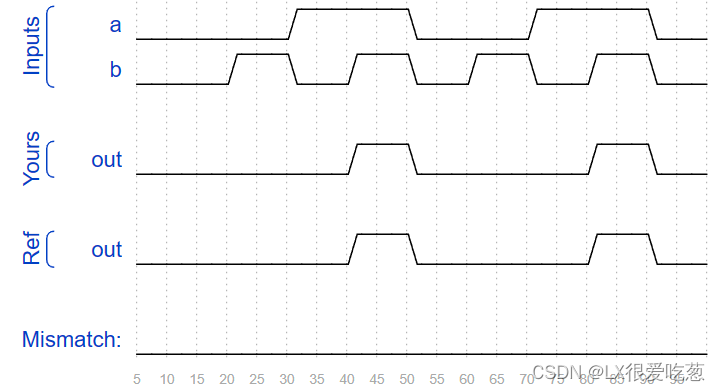

代码结果

1.2 例题2: [Norgate]

题目描述

Create a module that implements a NOR gate. A NOR gate is an OR gate with its output inverted. A NOR function needs two operators when written in Verilog.

An

assignstatement drives a wire (or “net”, as it’s more formally called) with a value. This value can be as complex a function as you want, as long as it’s a combinational (i.e., memory-less, with no hidden state) function. Anassignstatement is a continuous assignment because the output is “recomputed” whenever any of its inputs change, forever, much like a simple logic gate.

题目分析

题目要求创建一个实现或门与非门结合的 Verilog 模块。这个分别有两个输入信号,分别为

ina、inb,以及一个输出信号out。其中,ina和inb已经由输入端口赋值,输出信号为两个输入信号的或和非的结果。题目要求使用 Verilog 语句来将out的值设为ina、inb两者的或非操作结果。

解题代码

module top_module(

input a,

input b,

output out );

assign out = ~(a|b);

endmodule

代码结果

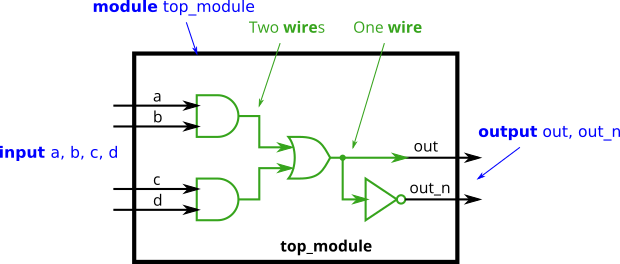

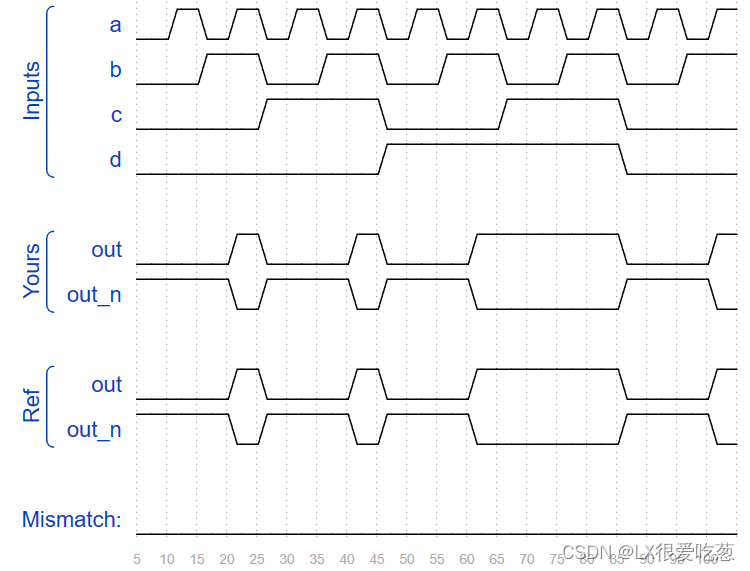

1.3 例题3: [Wire decl]

题目描述

Implement the following circuit. Create two intermediate wires (named anything you want) to connect the AND and OR gates together. Note that the wire that feeds the NOT gate is really wire

out, so you do not necessarily need to declare a third wire here. Notice how wires are driven by exactly one source (output of a gate), but can feed multiple inputs.If you’re following the circuit structure in the diagram, you should end up with four assign statements, as there are four signals that need a value assigned.

(Yes, it is possible to create a circuit with the same functionality without the intermediate wires.)

题目分析

这个任务描述了一个数字逻辑电路的实现。如下简单的信息分析:

-

组件:

- 与门 (AND gate)

- 或门 (OR gate)

- 非门 (NOT gate)

-

连接:

- 两个中间导线连接 AND 门和 OR 门。

-

输出:

- 输出导线命名为

out,out_n。

- 输出导线命名为

-

赋值语句:

- 将有四个赋值语句来为信号赋值。

-

逻辑结构:

- 与门有两个输入和一个输出。

- 中间导线 (Wire1) 连接 AND 门的输出到 OR 门的一个输入。

- OR 门的另一个输入连接到一个直接输入。

- OR 门的输出即为最终的输出导线 (

out)。 - 非门的输入为 AND 门的输出。

-

电路图:

输入1 ----\ 与门 ---- Wire1 ---- 或门 ---- out 输入2 ----/ -

赋值语句(使用 Verilog 语法):

wire wire1 = a & b; // 将 AND 门的输出赋值给 Wire1 wire wire2 = c & d; wire wire3 = wire1 | wire2; // 将 OR 门的输出赋值给 wire3 assign out = wire3; // 一个输出 assign out_n = ~wire3; // 一个输出

解题代码

// Make sure to remove the "default_nettype none" directive if you have it.

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n

);

wire wire1 = a & b;

wire wire2 = c & d;

wire wire3 = wire1 | wire2;

assign out = wire3;

assign out_n = ~wire3;

endmodule

代码结果

2. 组合电路练习

《知识分析》

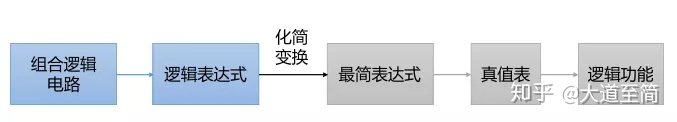

组合逻辑电路介绍

组合逻辑电路是一种数字逻辑电路,其输出仅取决于当前的输入状态,而不受过去输入状态的影响。组合逻辑电路的设计基于布尔代数原理,它执行布尔运算并产生相应的输出。这种类型的电路通常用于执行特定的功能或任务,如加法器、减法器、多路选择器等。

组合逻辑电路分析

在组合逻辑电路中,信号通过逻辑门连接,这些逻辑门执行基本的逻辑操作,例如与、或、非等。输入信号经过逻辑门的布尔运算后,产生输出信号。组合逻辑电路没有存储元件,因此其输出完全由输入决定,没有状态或记忆效应。

在设计组合逻辑电路时,关键是理解特定功能的布尔代数表达式,并将其转化为逻辑门的连接。这包括确定所需的逻辑门类型、数量以及它之间的布局。

组合逻辑电路设计

设计一个组合逻辑电路的一般步骤如下:

- 问题定义: 确定电路需要执行的特定功能或逻辑操作。

- 布尔表达式: 将问题转化为布尔代数表达式。这可以通过真值表、逻辑方程或卡诺图等方法完成。

- 逻辑门选择: 根据布尔表达式,选择适当类型的逻辑门(与门、或门、非门等)来实现每个逻辑操作。

- 逻辑门连接: 将所选的逻辑门按照布尔表达式的逻辑连接在一起。这可能需要使用中间信号线来传递部分计算结果。

- 验证和优化: 使用模拟工具或硬件仿真验证电路的功能。优化电路结构,以提高性能或减少延迟。

- 实施: 将设计转化为硬件或程序代码,具体取决于应用的实现方式。

- 测试和验证: 在实际硬件或模拟器中测试电路,确保其按照设计要求正常工作。

组合逻辑电路设计的关键在于理解布尔代数原理和逻辑门的特性,以及将抽象的逻辑功能转化为具体的电路结构。随着技术的进步,数字设计工具和硬件描述语言(HDL)的使用变得越来越普遍,简化了组合逻辑电路的设计过程。

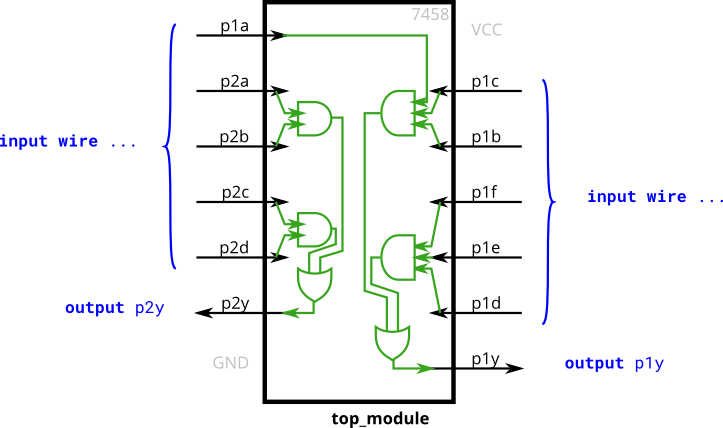

2.1 例题1: [7458]

题目描述

The 7458 is a chip with four AND gates and two OR gates. This problem is slightly more complex than 7420.

Create a module with the same functionality as the 7458 chip. It has 10 inputs and 2 outputs. You may choose to use an

assignstatement to drive each of the output wires, or you may choose to declare (four) wires for use as intermediate signals, where each internal wire is driven by the output of one of the AND gates. For extra practice, try it both ways.

题目分析

- 目标: 创建一个模块,模拟7458芯片的功能,该芯片包含四个AND门和两个OR门。模块应该有10个输入和2个输出。

- 输入:

- 模块有10个输入(input [9:0] inputs),分别表示7458芯片的10个输入引脚。

- 输出:

- 模块有2个输出(output reg out1, output reg out2),分别表示7458芯片的两个输出引脚。

- AND门:

- 7458芯片包含四个AND门。在模块中,我可以通过多个AND运算实现。

- OR门:

- 7458芯片包含两个OR门。在模块中,我可以通过多个AND门的输出连接到OR门实现。

- 实现方式:

- 题目提供了两种实现方式:

- 使用

assign语句直接计算输出值。 - 使用中间信号线(

wire)连接AND和OR门的输出。

- 使用

- 题目提供了两种实现方式:

- 分析:

- 输入信号经过四个AND门进行逻辑与运算。

- AND门的输出通过两个OR门进行逻辑或运算。

- 输出信号的生成可以通过直接使用

assign语句或通过中间信号线实现。

解题代码

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

wire p2ab = p2a&p2b;

wire p2cd = p2c&p2d;

assign p2y = p2ab|p2cd;

wire p1acd = p1a&p1c&p1b;

wire p1fed = p1f&p1d&p1e;

assign p1y = p1acd|p1fed;

endmodule

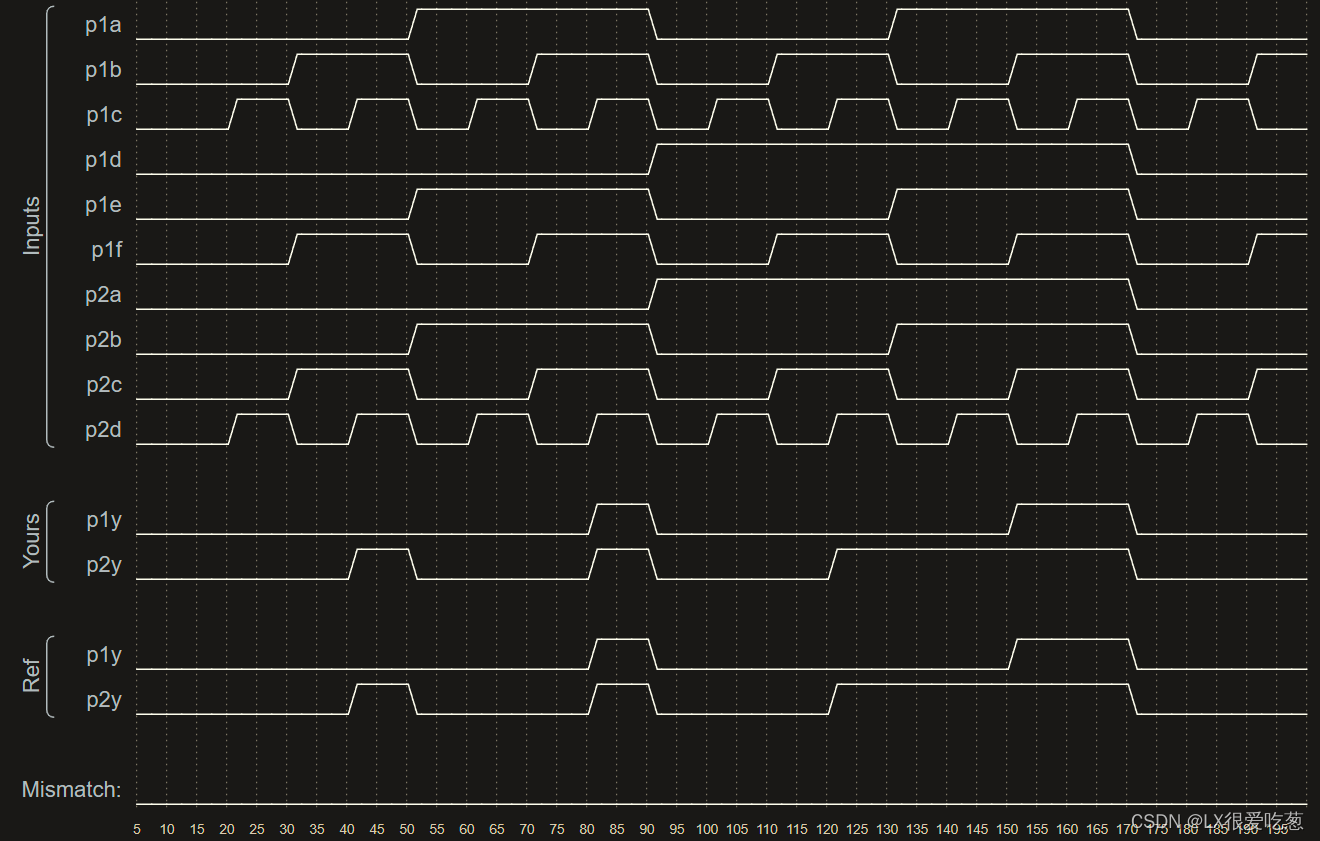

代码结果

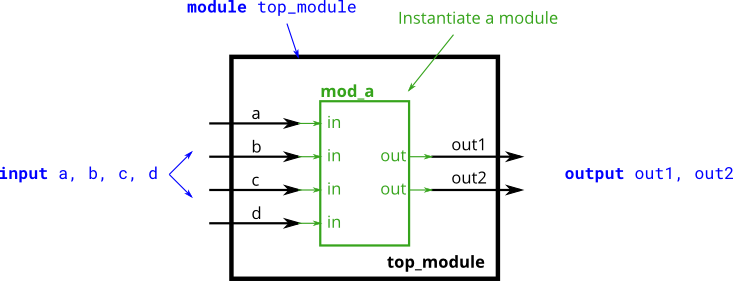

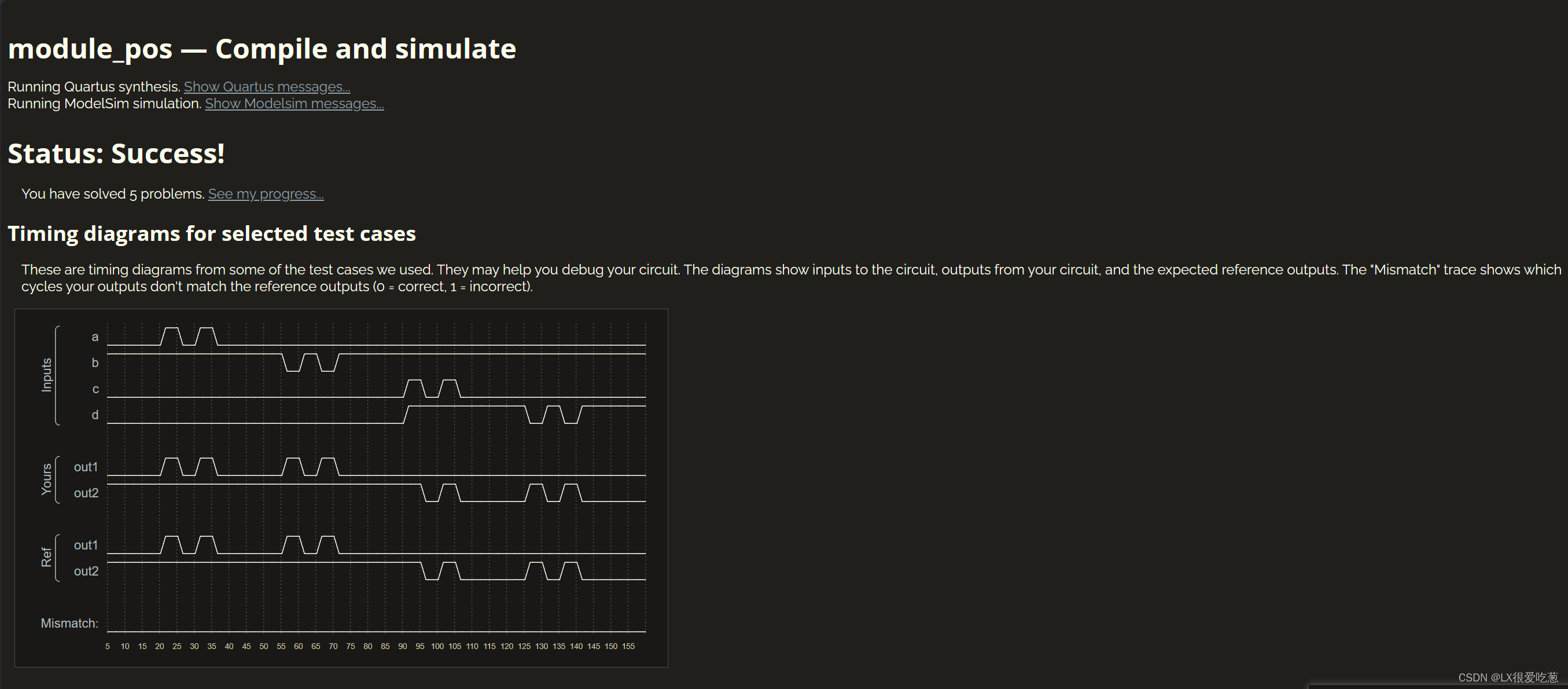

2.2 例题2: [Module pos]

题目描述

This problem is similar to the previous one (module). You are given a module named that has 2 outputs and 4 inputs, in that order. You must connect the 6 ports by position to your top-level module’s ports , , , , , and , in that order.

mod_a``out1``out2``a``b``c``dYou are given the following module:

module mod_a ( output, output, input, input, input, input );

题目分析

- 目标: 在这个问题中,要求实例化一个名为

mod_a的模块。mod_a模块有两个输出和四个输入,端口的顺序是先输出后输入。 - 模块声明:

mod_a模块的声明为:module mod_a (output, output, input, input, input, input);- 具体来说,模块有两个输出(output)、分别命名为

out1和out2,以及四个输入(input),分别命名为a、b、c和d。

- 连接顺序:

- 要求实例化

mod_a模块,并按照顺序将其两个输出和四个输入连接到另一个顶层模块top_module的端口。 - 顶层模块

top_module的端口顺序是out1、out2、a、b、c、d。

- 要求实例化

- 实例化:

- 在实例化过程中,确保按照顺序将

mod_a模块的输出和输入连接到top_module的对应端口。

- 在实例化过程中,确保按照顺序将

解题代码

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a uut ((out1), (out2), (a), (b), (c), (d));

endmodule

代码结果

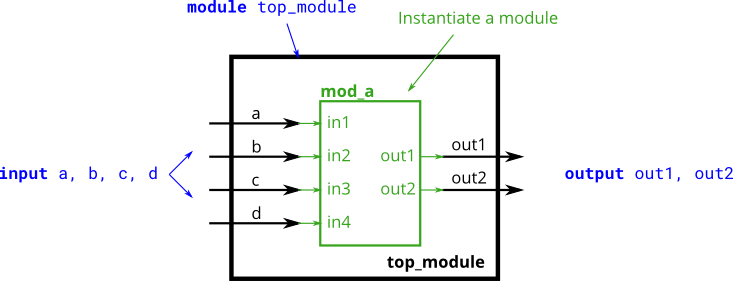

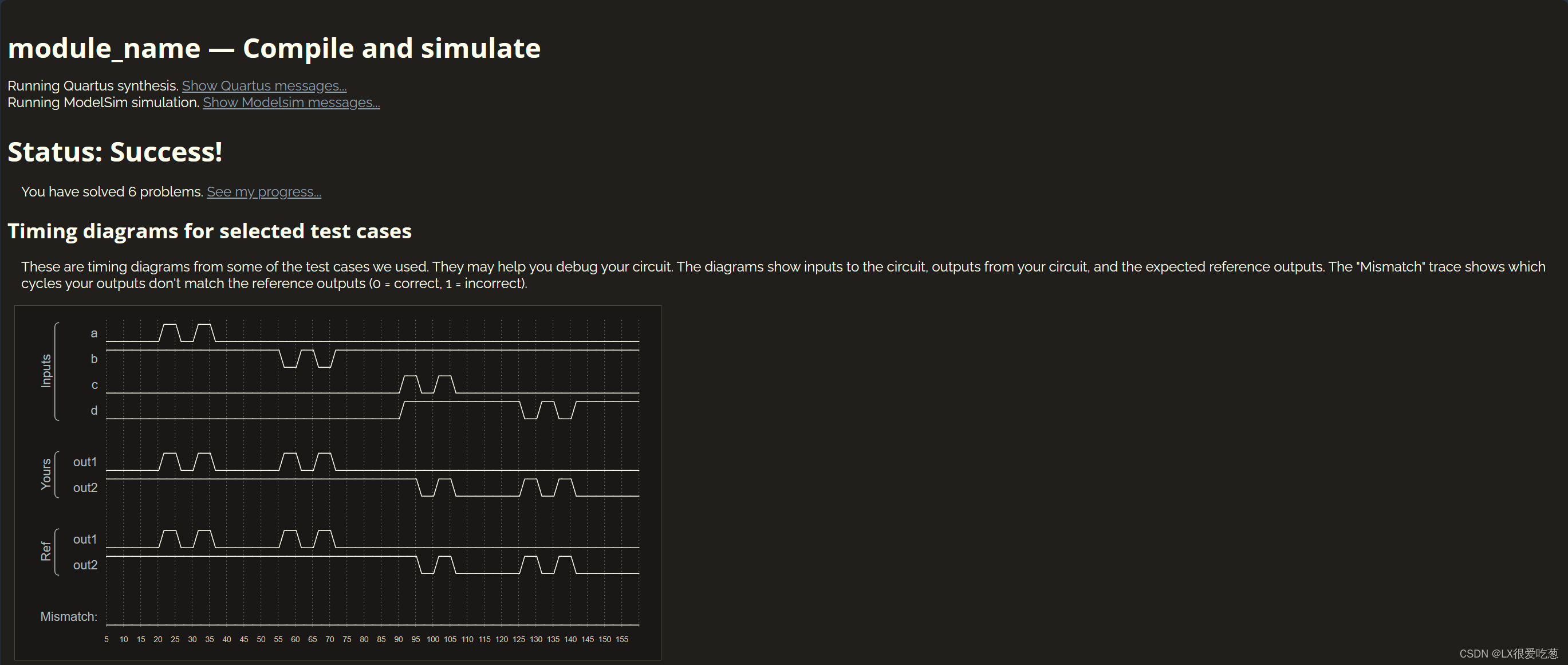

2.3 例题3: [Module name]

题目描述

This problem is similar to module. You are given a module named

mod_athat has 2 outputs and 4 inputs, in some order. You must connect the 6 ports by name to your top-level module’s ports:

Port in **mod_a**Port in **top_module**output out1out1output out2out2input in1ainput in2binput in3cinput in4dYou are given the following module:

module mod_a ( output out1, output out2, input in1, input in2, input in3, input in4);

题目分析

- 目标: 在这个问题中,要求实例化一个名为

mod_a的模块。mod_a模块有两个输出和四个输入,端口的顺序可能是任意的。 - 模块声明:

mod_a模块的声明为:module mod_a (output out1, output out2, input in1, input in2, input in3, input in4);- 具体来说,模块有两个输出(output)、分别命名为

out1和out2,以及四个输入(input),分别命名为in1、in2、in3和in4。

- 连接顺序:

- 要求实例化

mod_a模块,并按照端口名称将其两个输出和四个输入连接到另一个顶层模块top_module的端口。 - 顶层模块

top_module的端口名称与mod_a模块的端口名称一一对应。

- 要求实例化

- 实例化:

- 在实例化过程中,确保按照端口名称将

mod_a模块的输出和输入连接到top_module的对应端口。

- 在实例化过程中,确保按照端口名称将

解题代码

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a moda(.out1(out1),.out2(out2),.in1(a),.in2(b),.in3(c),.in4(d));

endmodule

代码结果

3. 时序电路练习

《知识分析》

时序逻辑电路介绍

时序逻辑电路是一种电子数字逻辑电路,与组合逻辑电路相比,它具有一些额外的特性,主要涉及信号的时序和状态的存储。时序逻辑电路使用存储元件(如触发器或锁存器)来存储信息,并具有时钟信号来同步操作。

时序逻辑电路的一些关键概念和特性:

- 时钟信号: 时序逻辑电路通常由一个时钟信号驱动,用于同步各个存储元件的状态变化。时钟信号以固定的频率振荡,例如,在每个上升沿或下降沿发生变化。

- 存储元件: 时序逻辑电路包含存储元件,如触发器(Flip-Flop)或锁存器(Latch)。这些元件用于存储电路的状态信息,并在时钟信号的作用下更新。

- 时序逻辑电路的状态: 时序逻辑电路具有状态,其状态是由存储元件中的信息确定的。状态在时钟信号的辅助下发生变化。

- 时序逻辑电路的时序性: 与组合逻辑电路不同,时序逻辑电路的输出不仅取决于当前输入,还取决于过去的输入和状态。因此,时序逻辑电路是一种具有时序性的电路。

- 时序逻辑电路的时延: 由于涉及存储元件,时序逻辑电路具有时延。信号的变化需要一定的时间才能传播到整个电路,并影响到输出。

- 时序逻辑电路的同步和异步设计: 时序逻辑电路可以采用同步设计或异步设计。同步时序逻辑电路使用时钟信号来同步所有存储元件的状态更新,而异步设计则不使用时钟信号,而是根据条件来触发状态变化。

- 状态机: 时序逻辑电路常用于实现状态机,其中电路在不同的状态之间转换,并且状态转换受到输入和当前状态的影响。

时序逻辑电路广泛应用于数字系统中,例如处理器、通信设备、存储器和各种控制系统。设计时序逻辑电路需要考虑时钟频率、时钟域交叉以及时序问题,以确保电路的正确性和可靠性。

时序逻辑电路分析

- 时序逻辑分析的步骤:

- 确定时序逻辑电路的输入和输出: 确定哪些信号是输入,哪些是输出。

- 建立状态图或状态表: 对于有限状态机,绘制状态图或编制状态表,以识别系统中可能的状态和状态之间的转移。

- 时序分析: 分析时序逻辑电路的时钟信号、时延和同步要求。这包括时钟周期、时钟脉冲宽度、信号传播时延等。

- 获得状态方程和输出方程: 对于有限状态机,根据状态图或状态表,得到状态方程和输出方程,这些方程描述了状态转移和输出与输入之间的关系。

- 时序逻辑分析工具:

- 仿真工具: 使用数字电路仿真工具(如ModelSim、VCS等)来验证时序逻辑电路的行为。仿真可以帮助理解电路在不同输入和时钟条件下的响应。

- 时序分析工具: 一些专业工具可以用于时序分析,帮助设计者评估电路的时序性能,包括时序偏差、时钟域交叉等。

时序逻辑电路设计

- 时序逻辑设计的步骤:

- 需求分析: 确定时序逻辑电路的功能和性能要求。了解输入、输出和状态转移的关系。

- 状态图设计: 对于有限状态机,绘制状态图以表示系统的各种状态及其之间的转换。

- 状态方程和输出方程的确定: 根据状态图,确定状态方程和输出方程,这些方程描述了状态转移和输出的逻辑关系。

- 选择存储元件: 选择适当类型的存储元件(触发器或锁存器),以存储系统的状态信息。

- 电路设计和布线: 使用硬件描述语言(如Verilog或VHDL)编写电路描述,并进行逻辑综合和布线,将设计映射到具体的硬件结构。

- 时序约束: 为电路设置时序约束,确保时钟和信号时序满足设计要求。

- 仿真和验证: 使用仿真工具验证电路的正确性和性能,包括时序分析、时钟域交叉分析等。

- 物理设计和布局: 对于ASIC设计,进行物理设计和布局,生成物理上的版图。

- 时序逻辑设计工具:

- HDL(硬件描述语言): 使用硬件描述语言(Verilog或VHDL)进行电路设计。

- 综合工具: 使用综合工具将HDL代码映射到硬件资源,生成逻辑电路。

- 布线工具: 使用布线工具将逻辑电路布线到芯片上。

- 时序分析工具: 使用时序分析工具评估电路的时序性能,确保满足时序约束。

3.1 例题1: [Dff]

题目描述

A D flip-flop is a circuit that stores a bit and is updated periodically, at the (usually) positive edge of a clock signal.

D flip-flops are created by the logic synthesizer when a clocked always block is used (See alwaysblock2). A D flip-flop is the simplest form of “blob of combinational logic followed by a flip-flop” where the combinational logic portion is just a wire.

Create a single D flip-flop.

题目分析

- 目标: 在这个问题中,要求创建一个单个的 D 触发器(D flip-flop)。

- ·D 触发器的定义:

- D 触发器是一种电路,用于存储一个比特,并在时钟信号的(通常为)正沿更新。它由一个组合逻辑部分和一个触发器组成,其中组合逻辑部分通常是一个简单的线路。

- 图示:

- 提供了一个 D 触发器的图示(Dff.png),其中显示了时钟信号对触发器的影响。

- 时钟边沿:

- 规定 D 触发器是由时钟信号的上升沿(通常为正沿)触发的。

- 组合逻辑部分:

- D 触发器的组合逻辑部分非常简单,通常只是一条线。这意味着 D 输入直接连接到触发器,没有经过任何逻辑运算。

题目要求:

创建一个单个的 D 触发器,使用 Verilog 或 VHDL 描述,确保它在时钟的上升沿处更新。可以参考 always 块的用法,描述 D 触发器的行为,并确保组合逻辑部分非常简单,只是将 D 输入直接连接到触发器。

解题代码

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always@(posedge clk) begin

q <= d;

end

endmodule

代码结果

3.2 例题2: [Dff8p]

题目描述

Create 8 D flip-flops with active high synchronous reset. The flip-flops must be reset to 0x34 rather than zero. All DFFs should be triggered by the negative edge of

clk.

题目分析

**要求:**创建8个带有主动高电平同步复位的D触发器。这些触发器在时钟的负跳变沿触发,并且在复位时被重置为0x34。

模块接口:

- 输入信号:

clk:时钟信号,用于触发D触发器。reset:复位信号,当复位信号为高电平时,触发器被重置为0x34。d:数据输入信号,用于更新触发器的状态。

- 输出信号:

q:输出信号,表示触发器的状态。

设计思路:

- 使用Verilog语言来实现该功能。

- 使用

always块来描述时钟的负跳变沿触发的行为。 - 当复位信号为高电平时,将输出信号

q设置为预定的值0x34。 - 当复位信号为低电平时,将输出信号

q与输入信号d保持一致。

解题代码

module top_module (

input clk,

input reset,

input [7:0] d,

output reg [7:0] q

);

always @(negedge clk) begin

if (reset) begin

q <= 8'b00110100; // 重置为0x34

end else begin

q <= d;

end

end

endmodule

代码结果

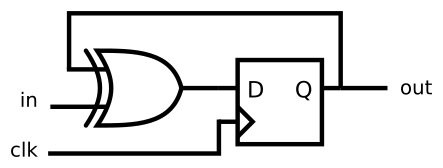

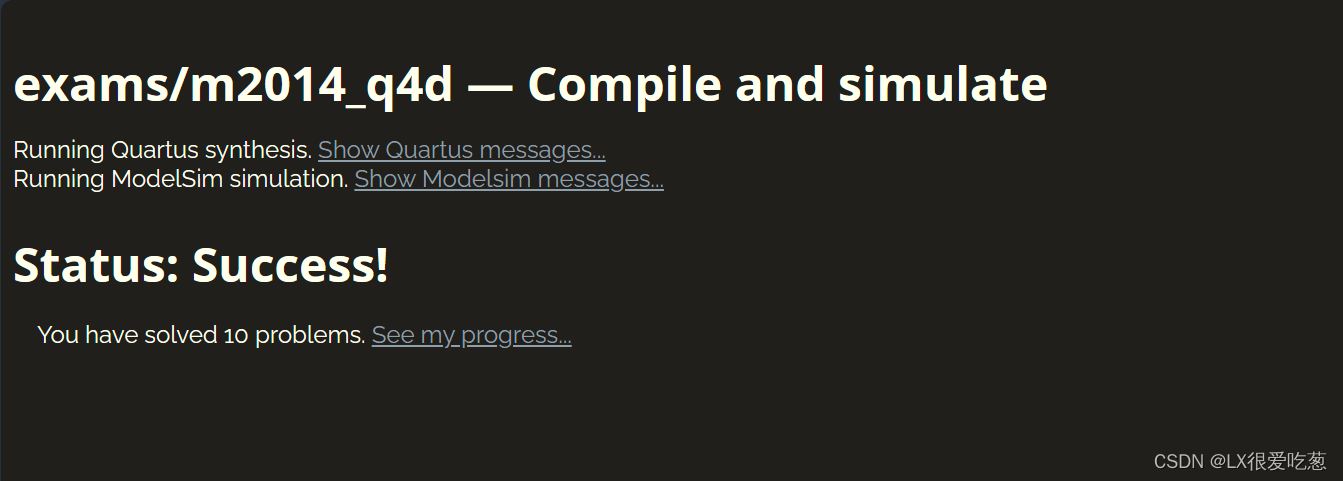

3.3 例题3: [Exams/m2014 q4d]

题目描述

Implement the following circuit:

题目分析

**要求:**设计一个模块,其包含一个输入信号(in)、一个时钟信号(clk)和一个输出寄存器(out)。在每个时钟的上升沿,输出寄存器的值更新为输入信号与当前输出寄存器值的异或结果。

模块接口:

- 输入信号:

clk:时钟信号,用于触发触发器的更新。in:输入信号,用于计算输出值。

- 输出信号:

out:输出信号,表示输出寄存器的当前值。

设计思路:

- 使用Verilog语言来实现该功能。

- 使用

always块来描述时钟的上升沿触发的行为。 - 在每个时钟的上升沿,将输出寄存器的值(

out)更新为输入信号(in)与当前输出寄存器值(out)的异或结果。

解题代码

module top_module (

input clk,

input in,

output reg out);

always @(posedge clk) begin

out <= in ^ out;

end

endmodule

代码结果

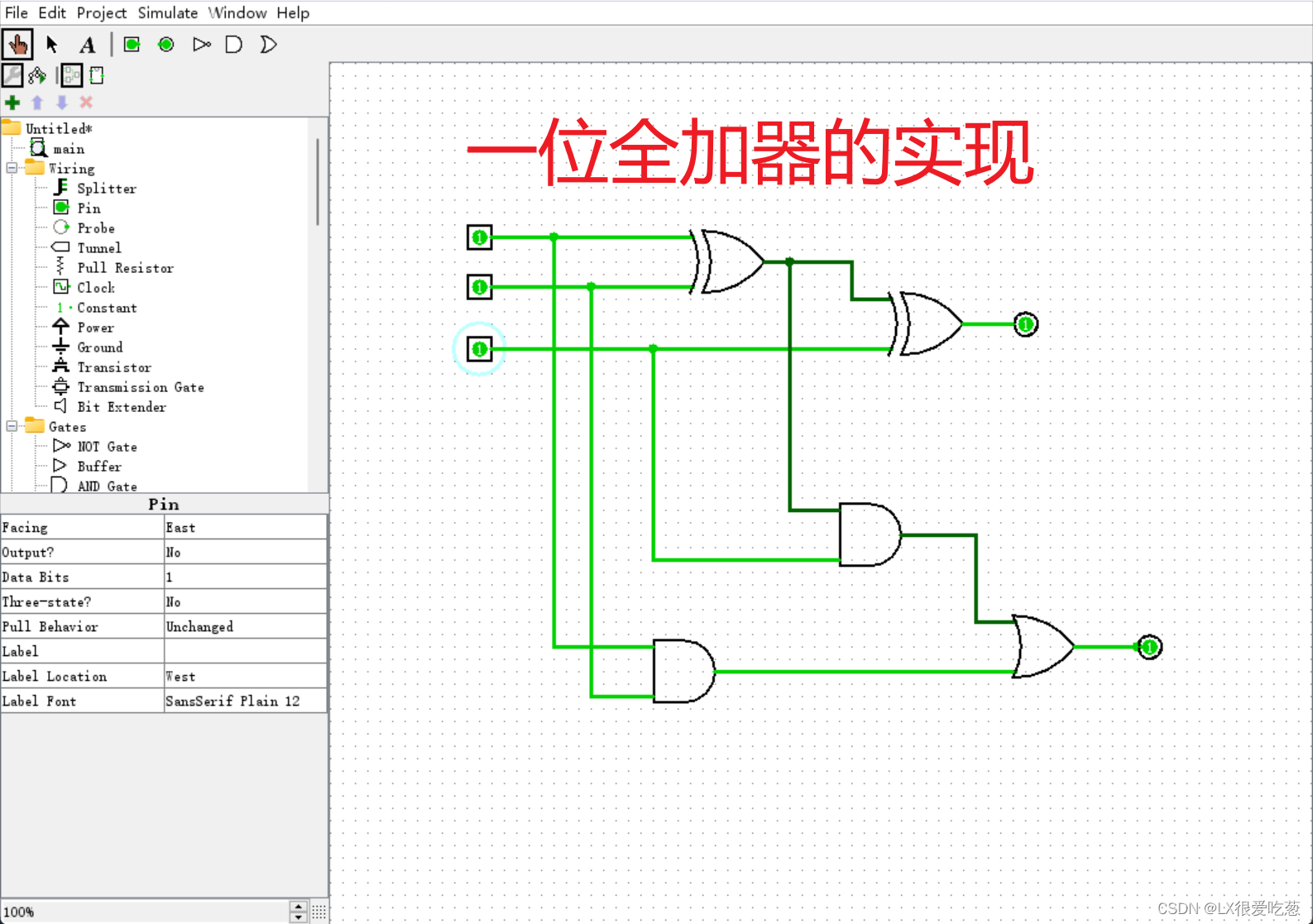

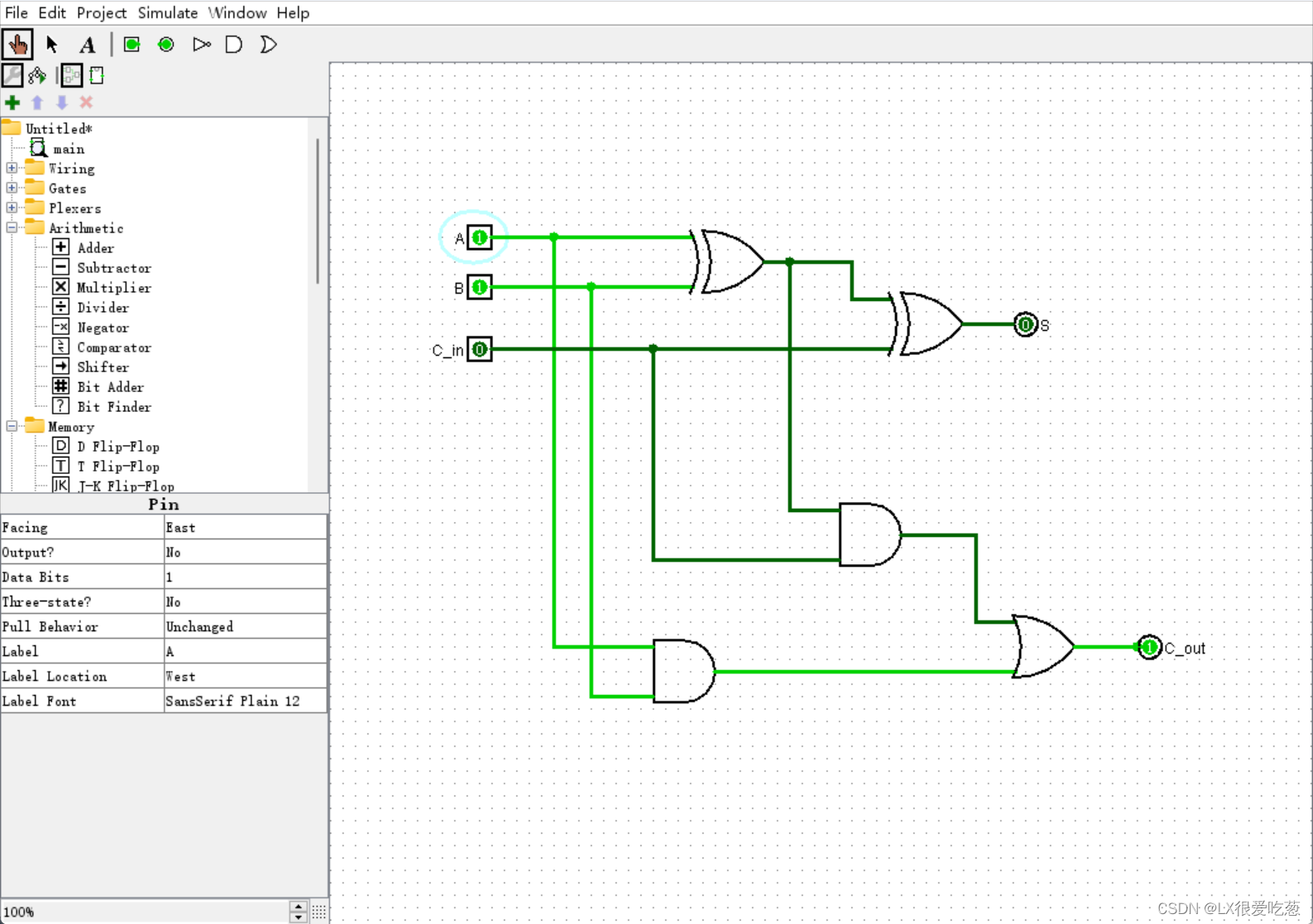

二. Logisim软件实践:

1位全加器

1. 1位全加器介绍

全加器是数字电路中的一种基本逻辑电路,用于将两个二进制位和前一位的进位相加,产生一个二进制的和以及一个可能的进位。全加器有三个输入和两个输出,分别是两个二进制输入(A和B)以及前一位的进位(Cin),两个输出分别是和(Sum)和进位输出(Cout)。

全加器的真值表如下:

A | B | Cin | Sum | Cout

---------------------------

0 | 0 | 0 | 0 | 0

0 | 0 | 1 | 1 | 0

0 | 1 | 0 | 1 | 0

0 | 1 | 1 | 0 | 1

1 | 0 | 0 | 1 | 0

1 | 0 | 1 | 0 | 1

1 | 1 | 0 | 0 | 1

1 | 1 | 1 | 1 | 1

根据上述真值表,全加器的功能可以总结如下:

- 当输入位A、B和Cin都为0时,和位Sum为0,输出进位位Cout为0。

- 当输入位A和B都为0,而Cin为1时,和位Sum为1,输出进位位Cout为0。

- 当输入位A为0,B为1,而Cin为0时,和位Sum为1,输出进位位Cout为0。

- 当输入位A为0,B为1,而Cin为1时,和位Sum为0,输出进位位Cout为1。

- 当输入位A为1,B为0,而Cin为0时,和位Sum为1,输出进位位Cout为0。

- 当输入位A为1,B为0,而Cin为1时,和位Sum为0,输出进位位Cout为1。

- 当输入位A、B和Cin都为1时,和位Sum为1,输出进位位Cout为1。

从上述真值表可以看出,全加器的和位Sum的结果是通过异或门(XOR)实现的,输出进位位Cout则是通过与门(AND)和或门(OR)实现的。

全加器在数字电路和计算机中广泛应用,是构建更复杂算术和逻辑电路的基础。多位加法器和处理器中的加法单元都是基于全加器的设计。

2. 设计与测试步骤

- 定义输入和输出:

- 确定输入信号:一般来说,全加器有两个二进制输入(A和B)以及一个进位输入(Cin)。

- 定义输出信号:全加器的输出包括和(Sum)和进位输出(Cout)。

- 编写真值表:

- 列出全加器的真值表,包括所有可能的输入组合和对应的输出。

- 逻辑表达式:

- 使用布尔代数或卡诺图等方法,推导出和(Sum)和进位输出(Cout)的逻辑表达式。

- 绘制电路图:

- 使用逻辑门(AND、OR、XOR等)和其他逻辑元件,根据逻辑表达式绘制出全加器的电路图。

- 选择逻辑门类型:

- 选择适当的逻辑门型号和类型来实现逻辑表达式。通常,AND门、OR门和XOR门是常见的选择。

设计的电路模块图如下:

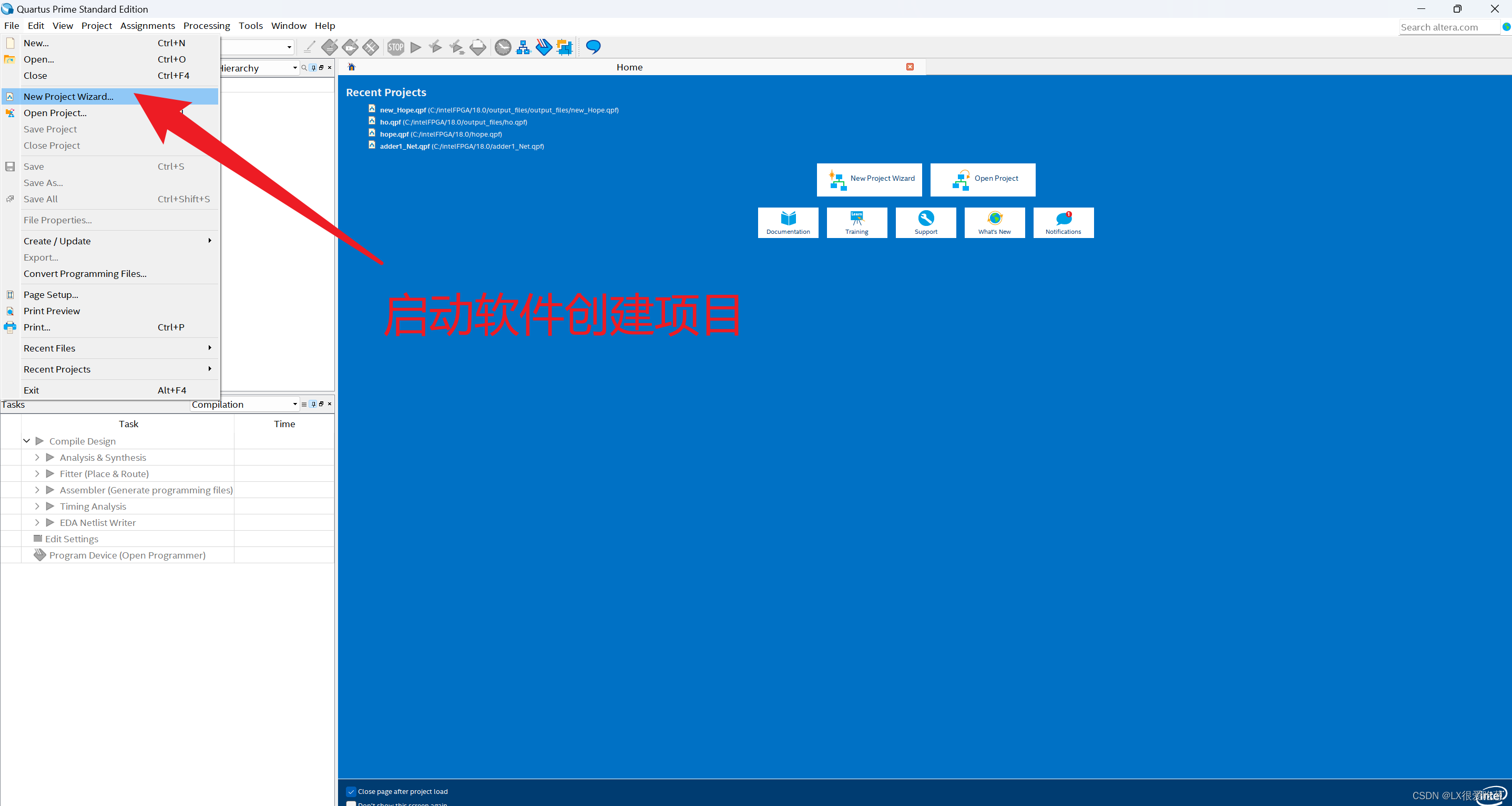

三. Quartus软件实践:

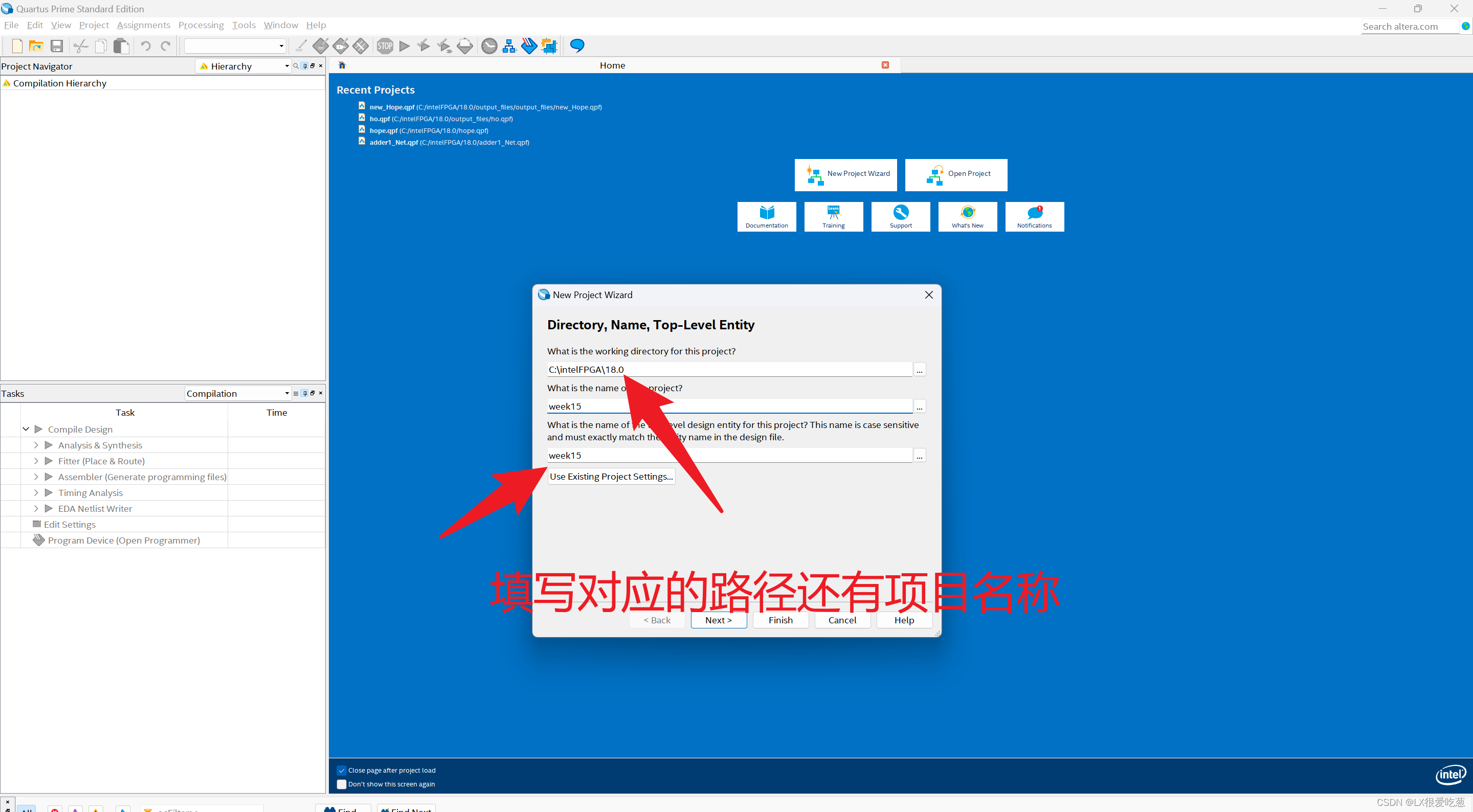

项目创建的具体过程

- 创建项目

-

填写相关信息

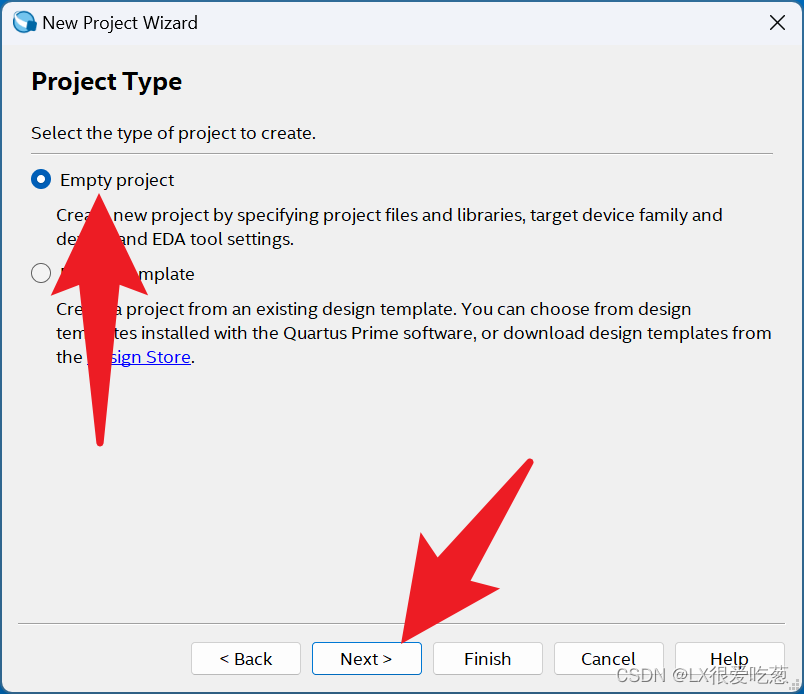

-

选择对应内容

然后记得下一个还是Next

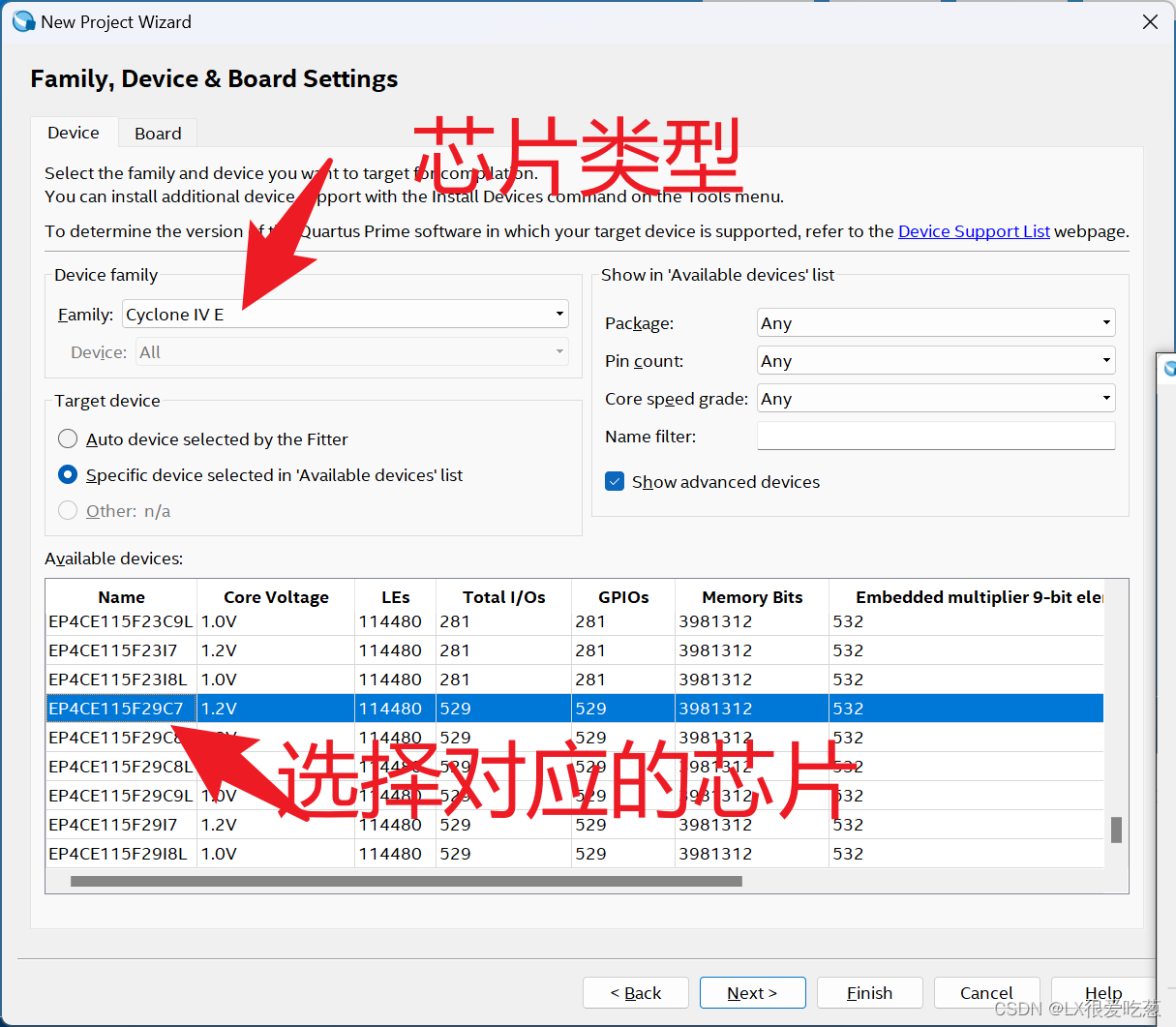

-

选择芯片数据

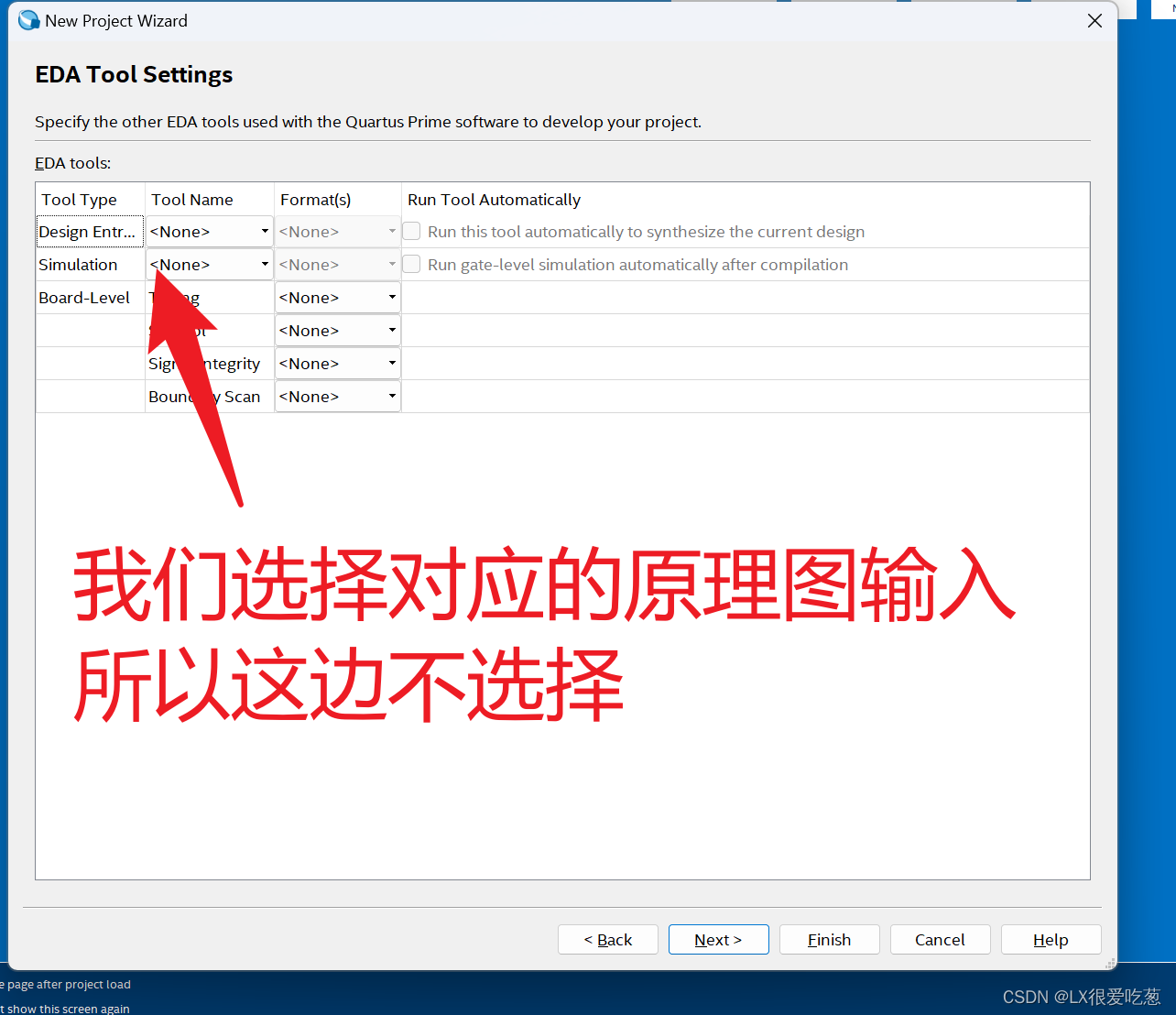

-

-

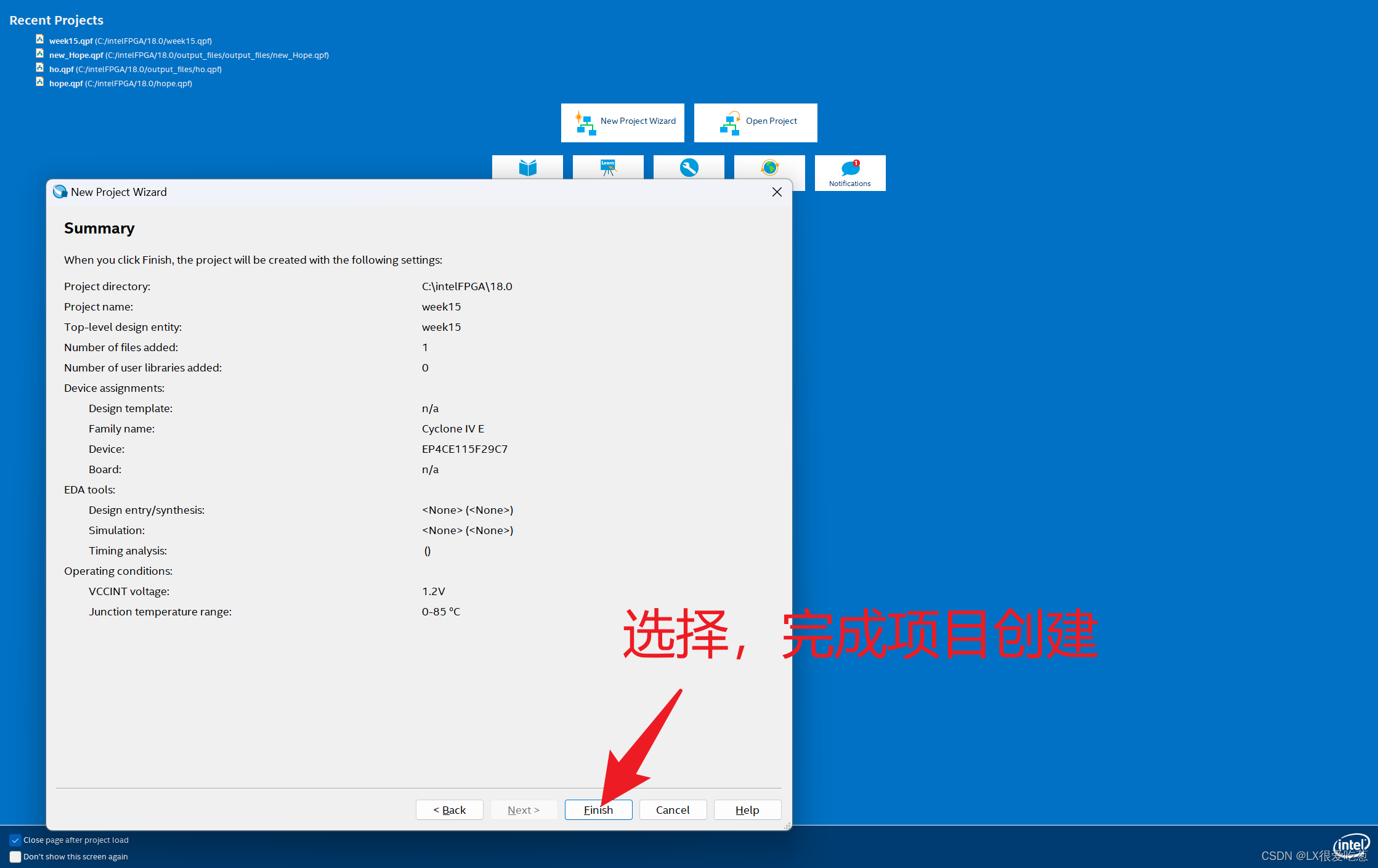

完成项目创建

半加器原理图实现过程

- 创建对应的原理图文件

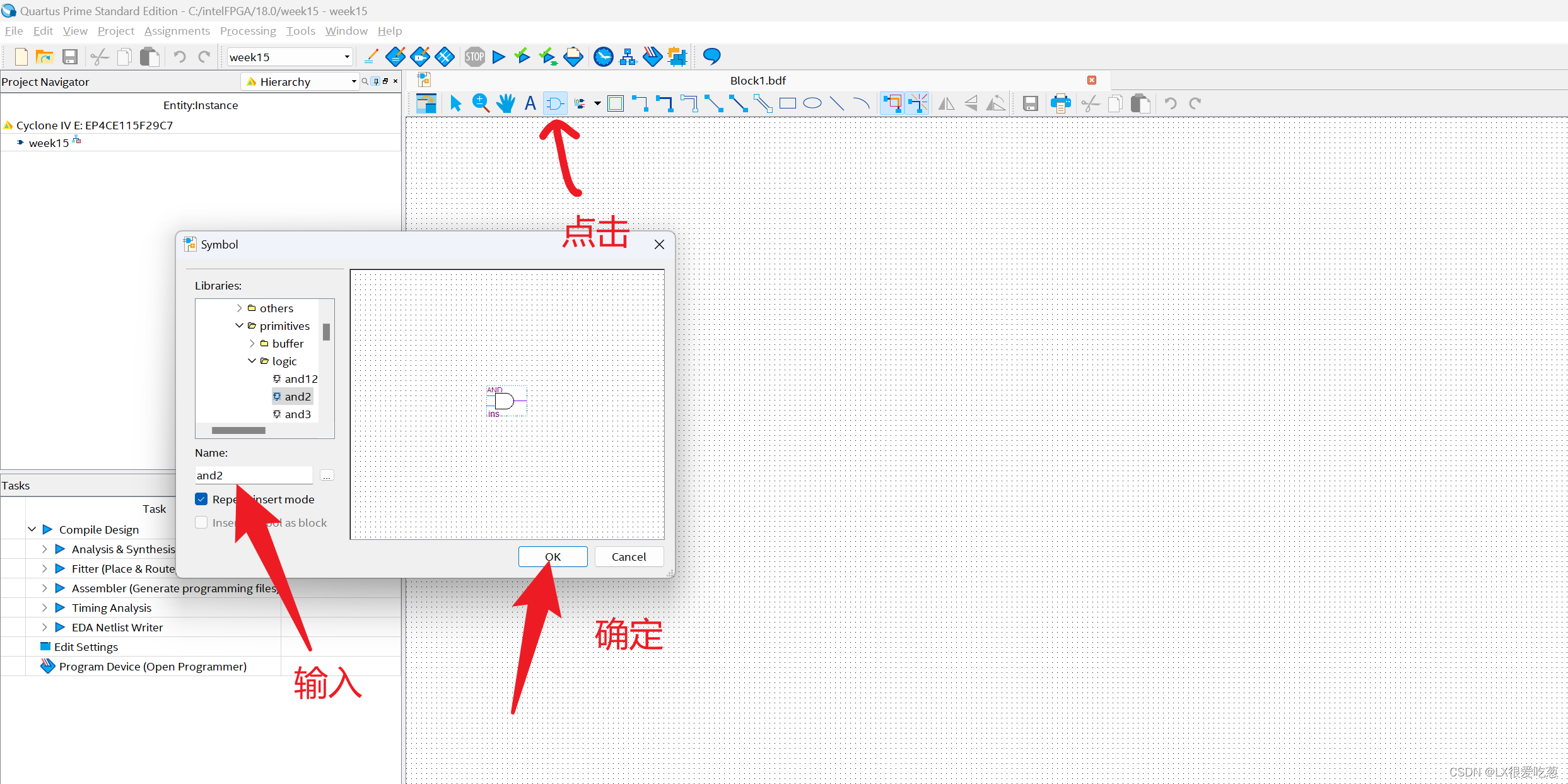

- 添加and2

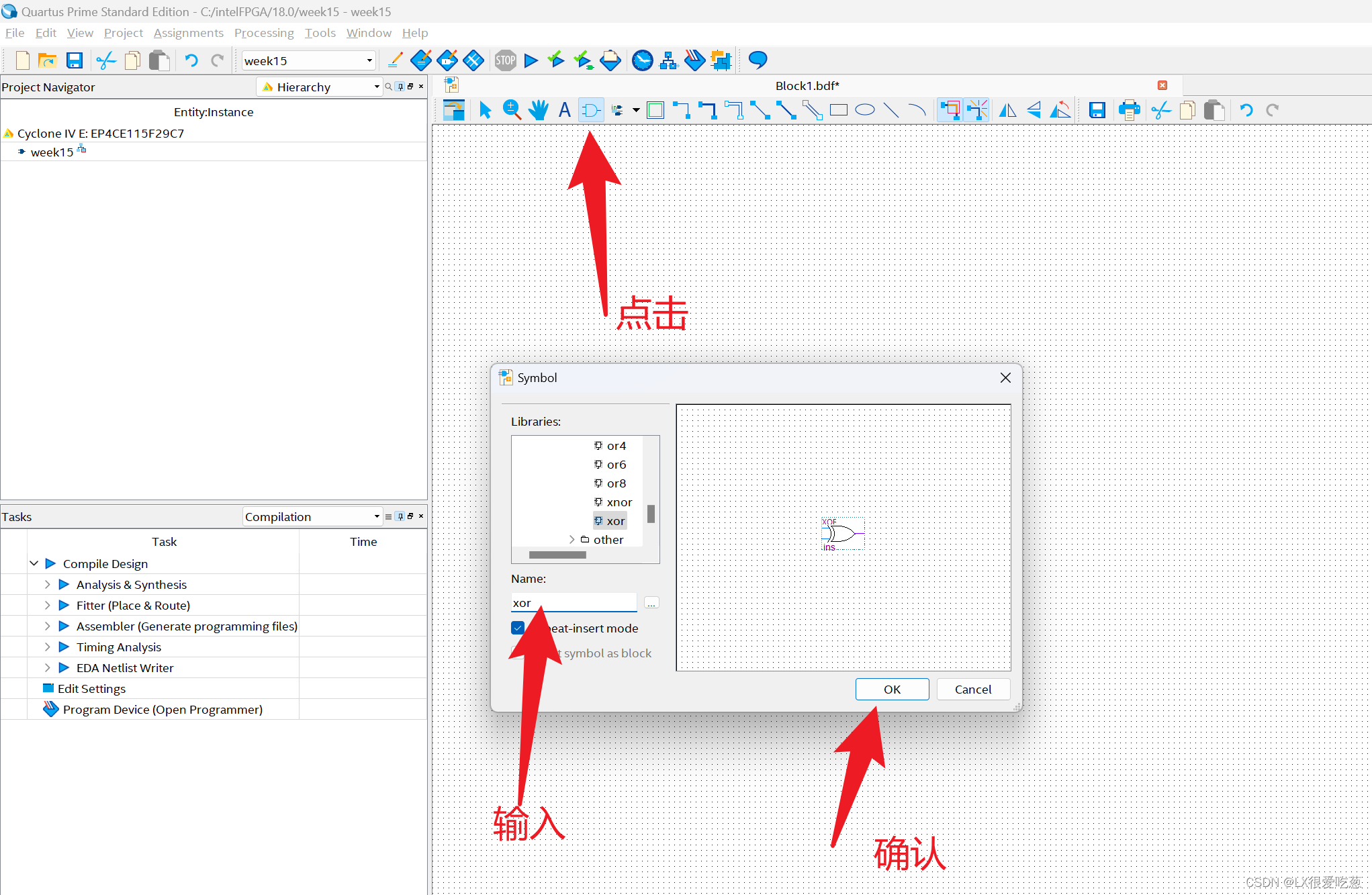

- 添加xor

-

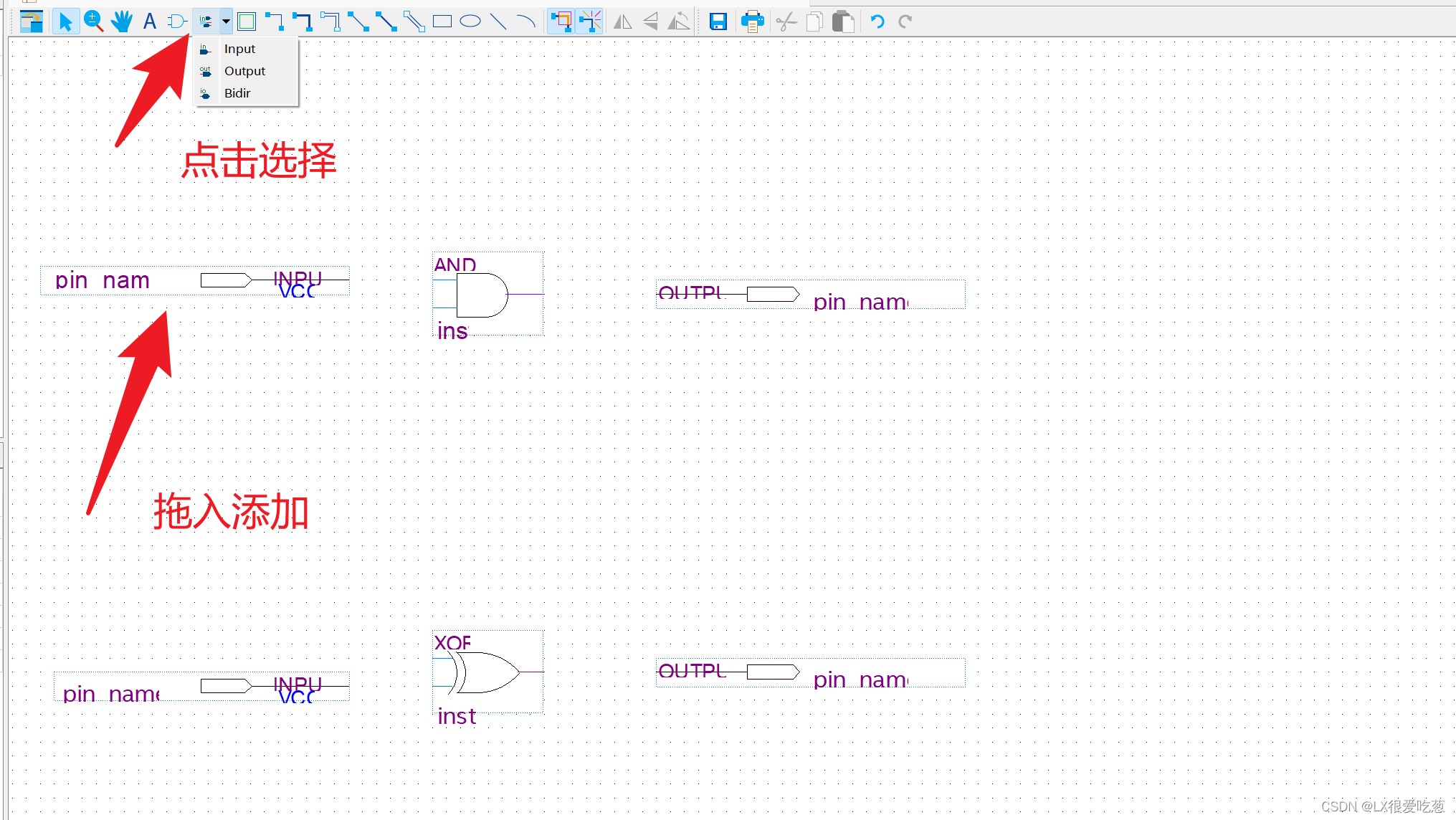

添加输入输出

-

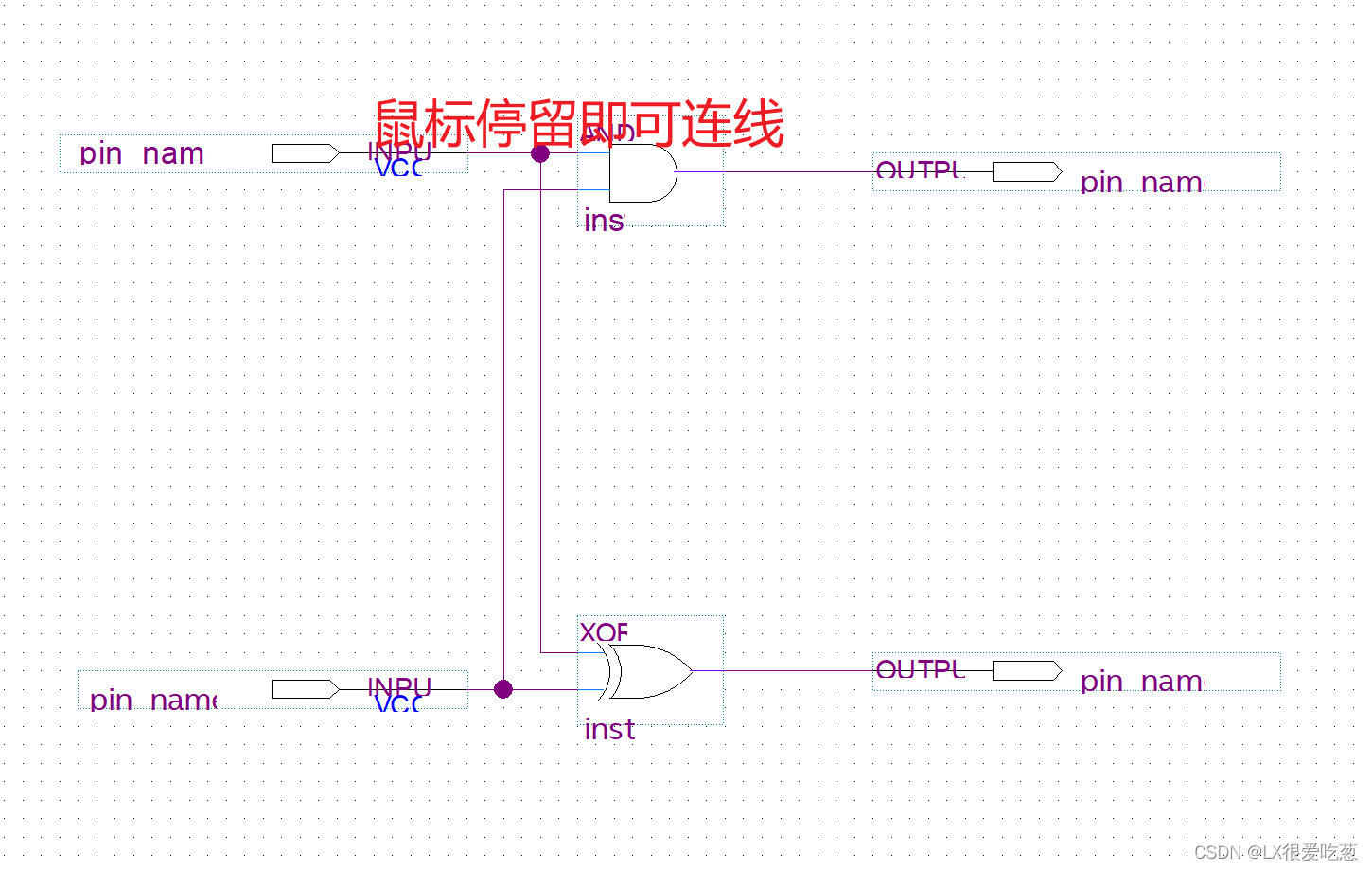

连线

-

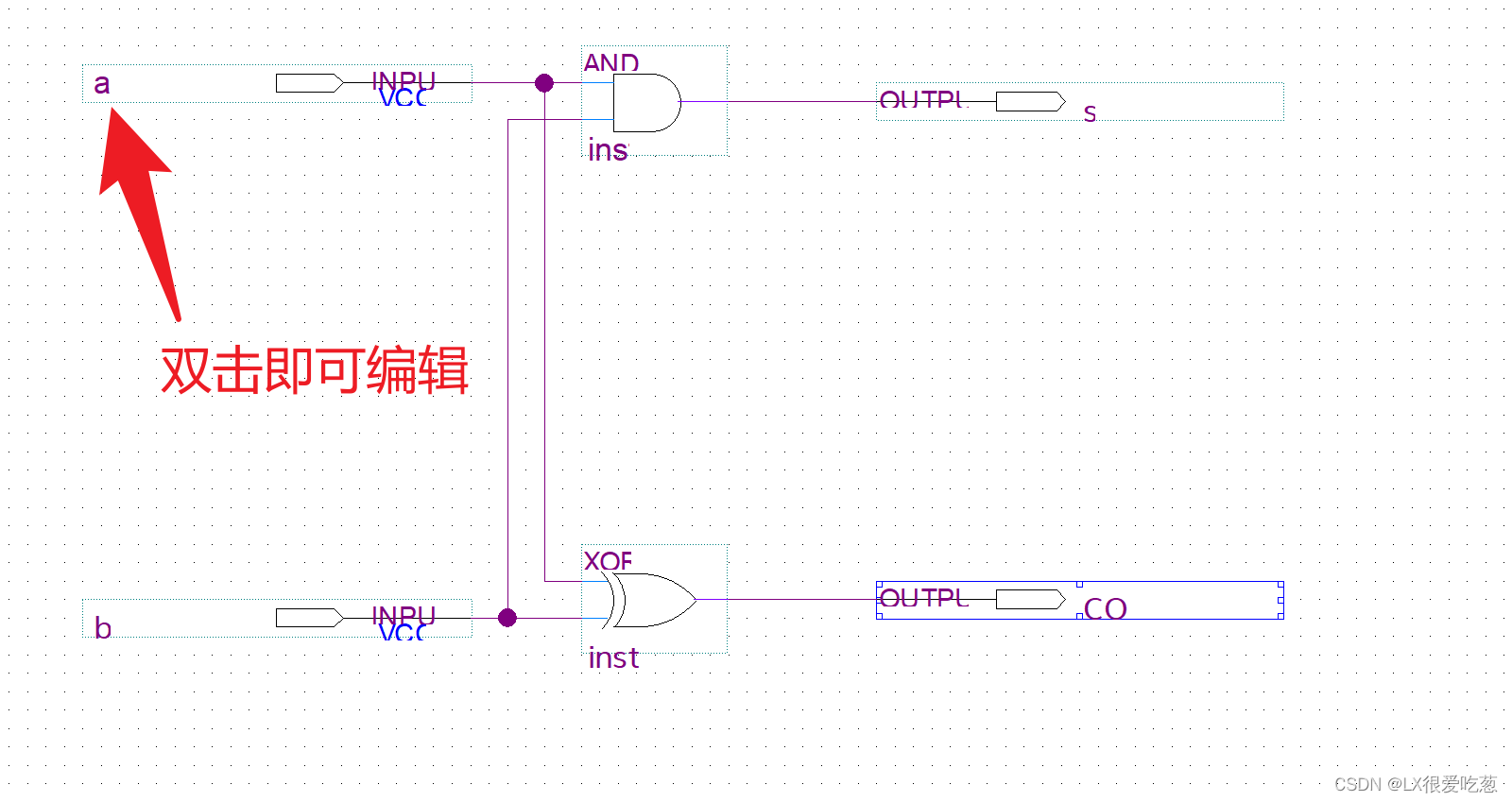

设置对应的标签,便于观察

-

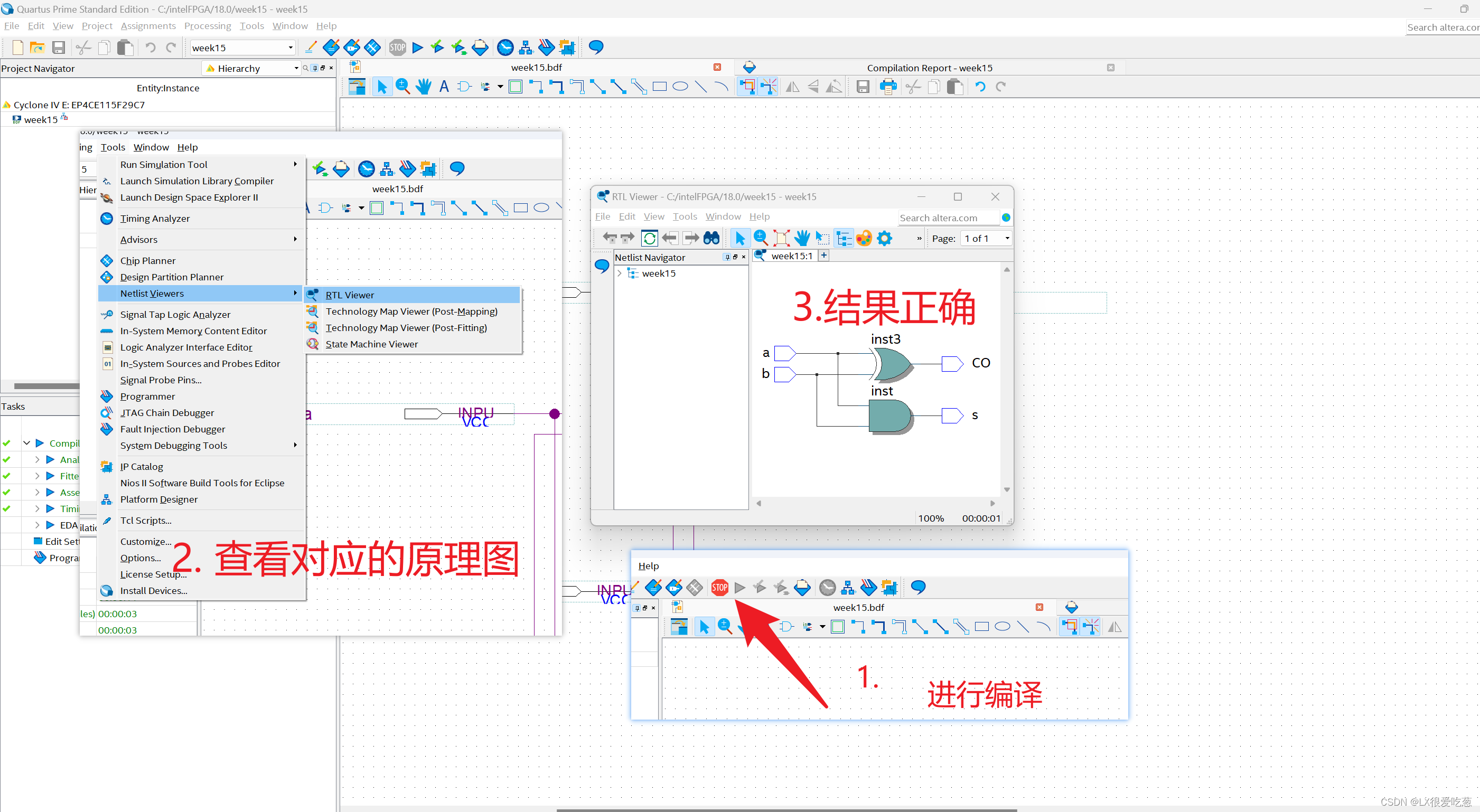

编译查看结果

半加器的仿真实现

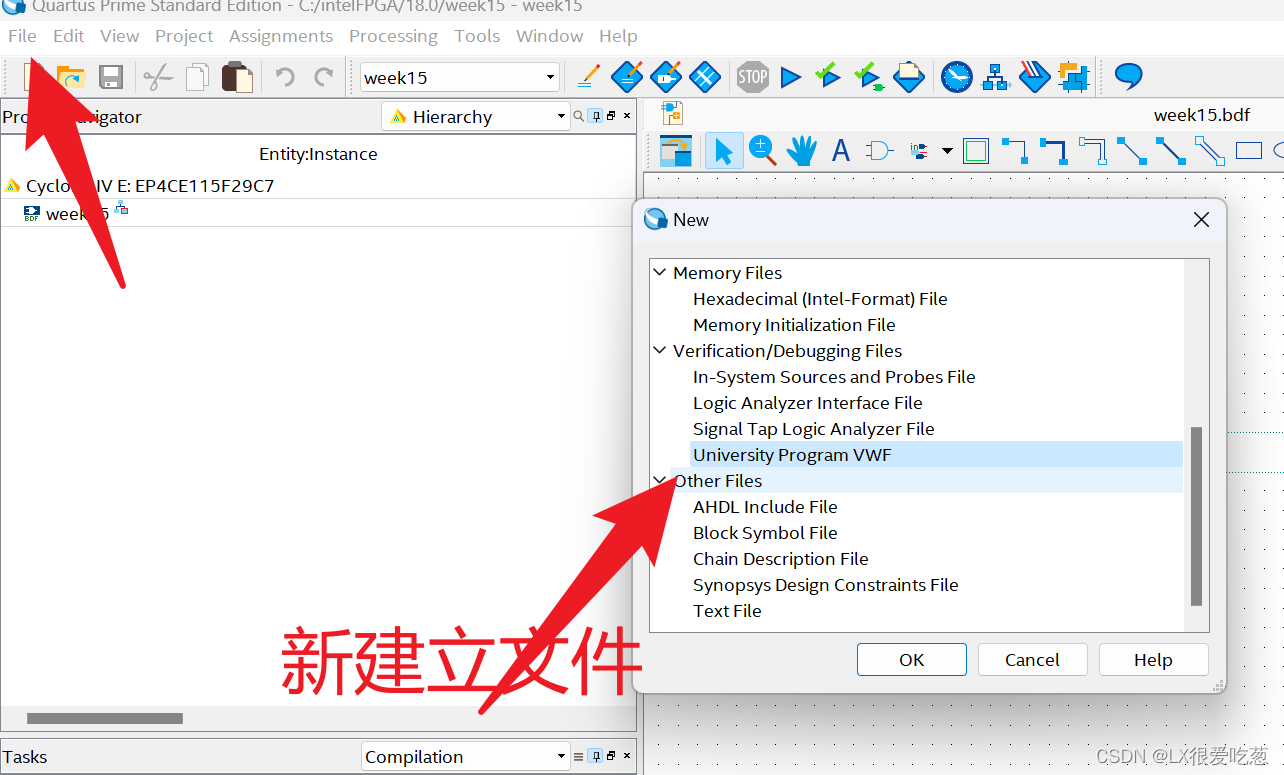

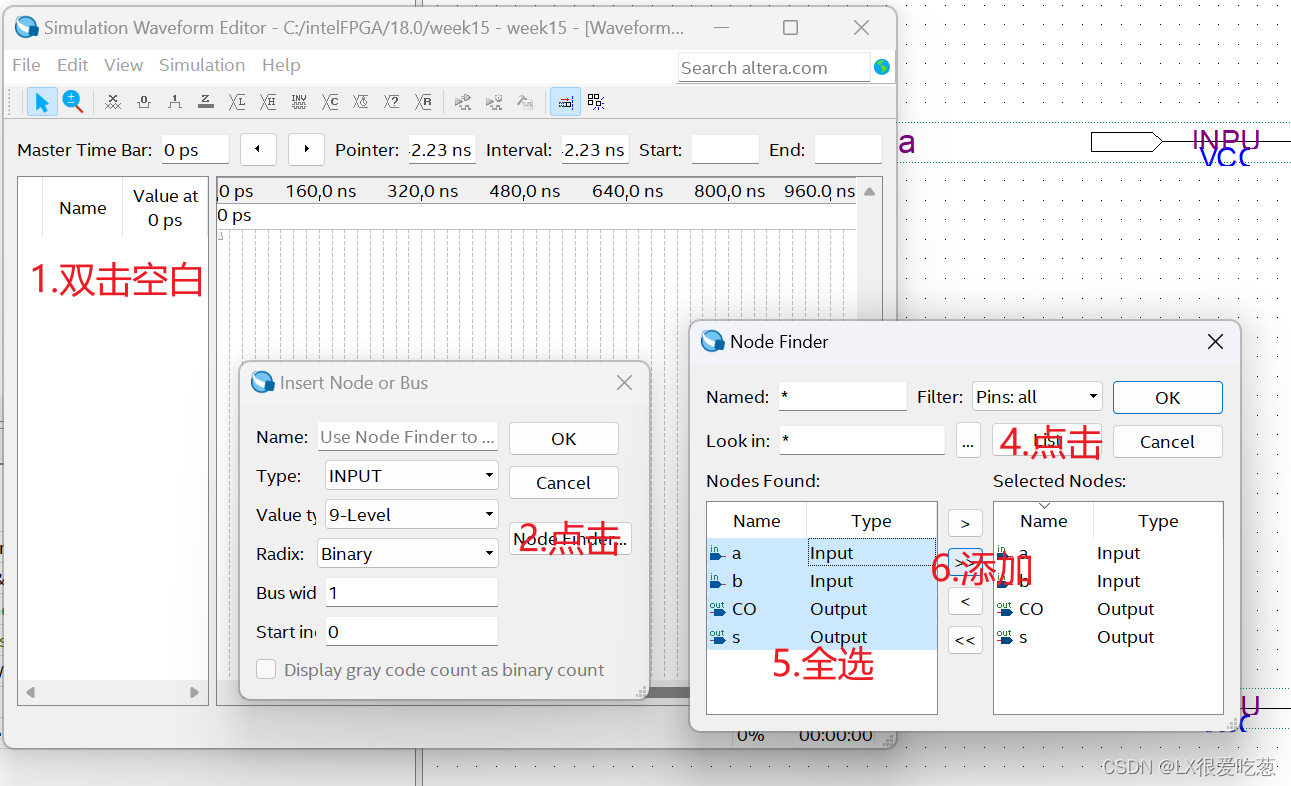

-

建立仿真文件

-

添加对应的信号

之后就全部OK就行了

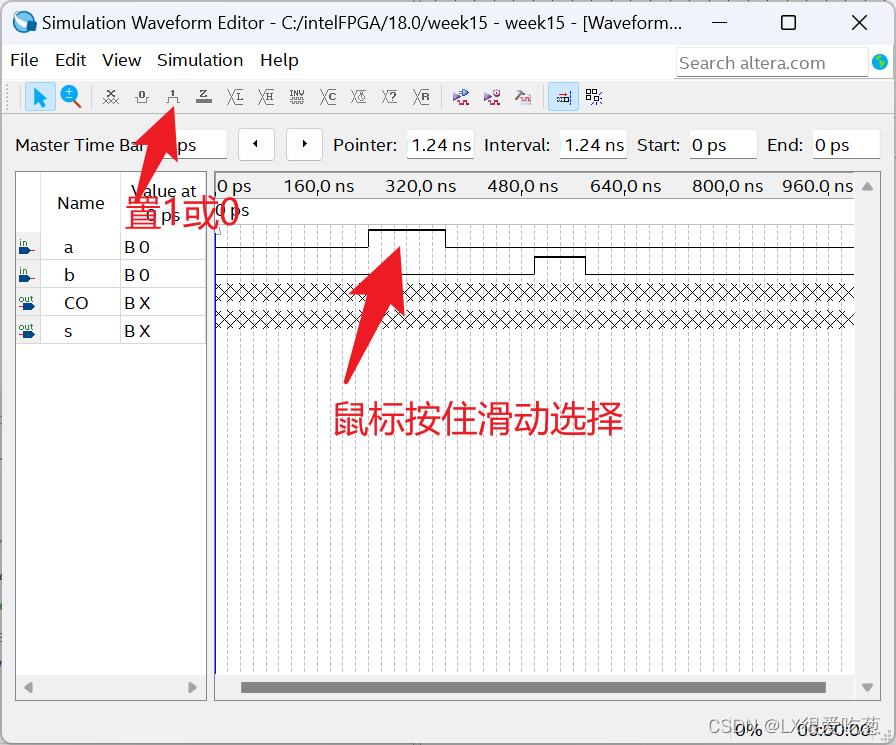

-

设置对应的1和0

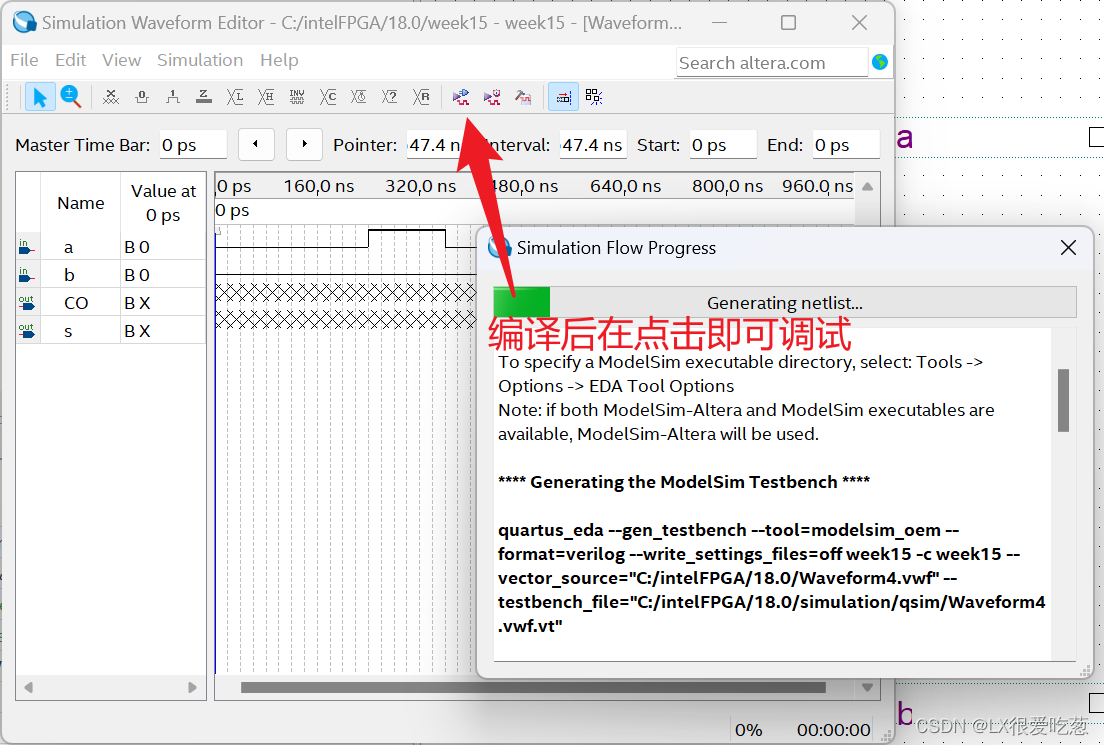

4.开始测试

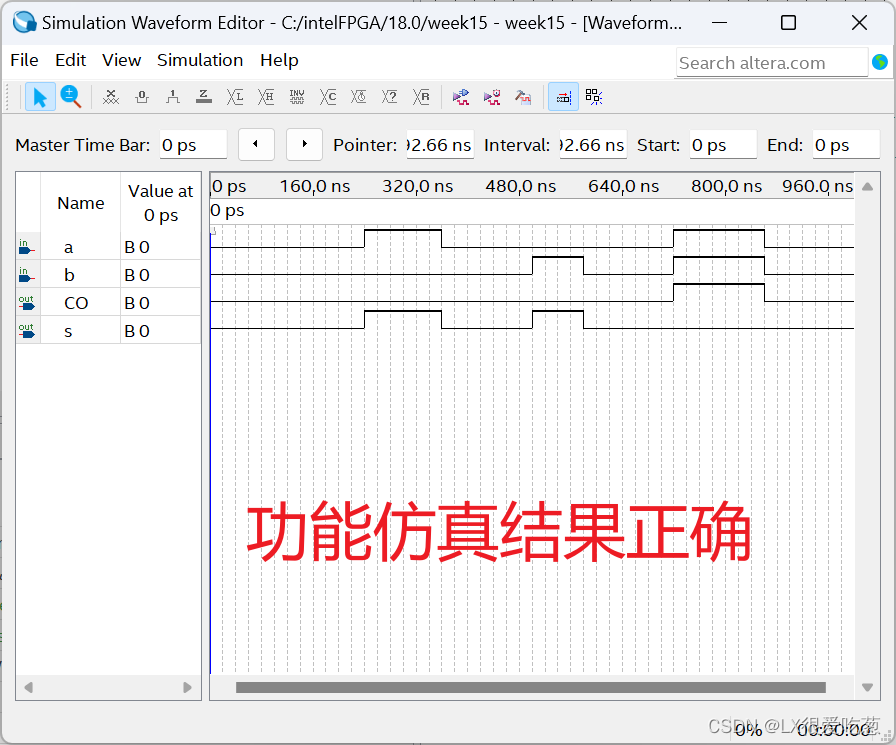

-

仿真结果观察

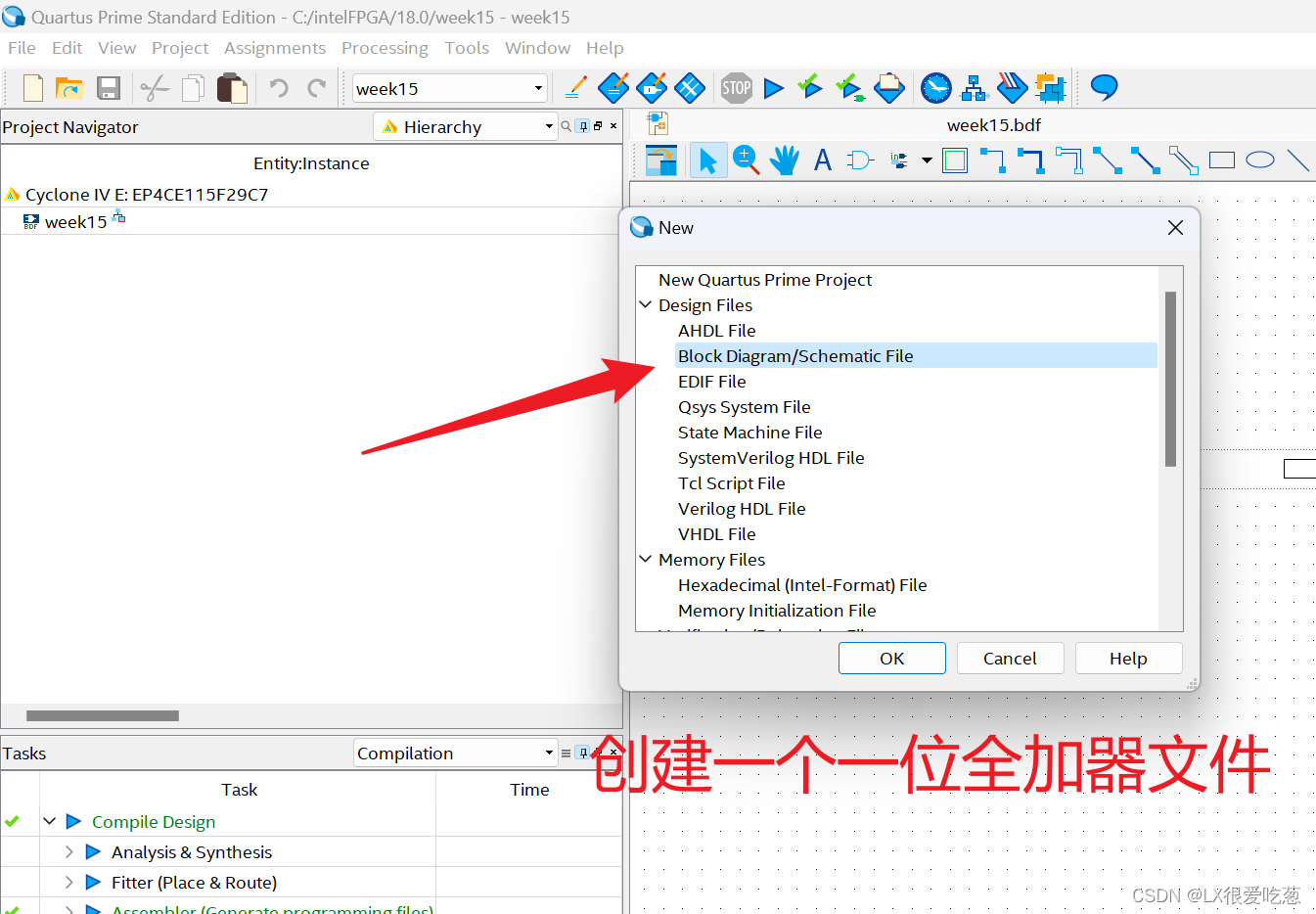

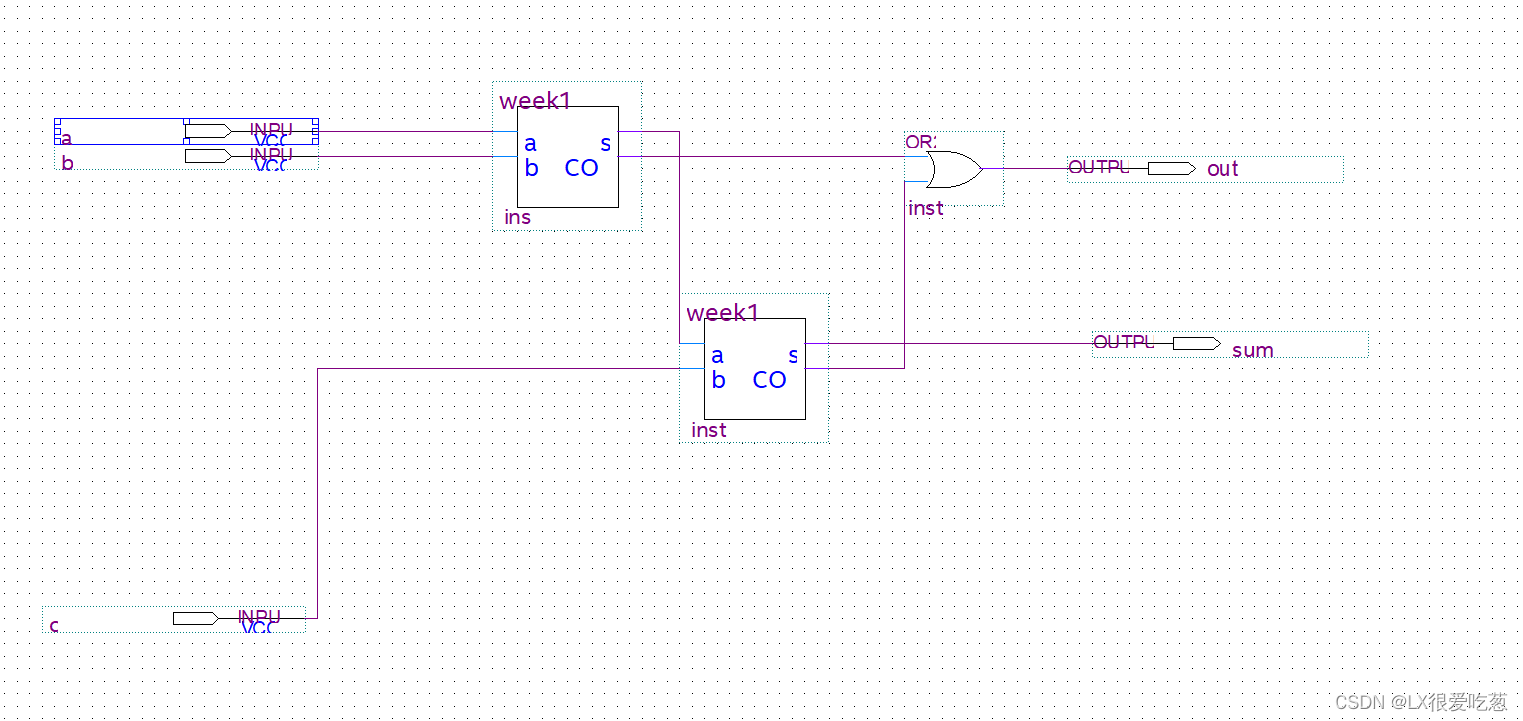

1位全加器的实现

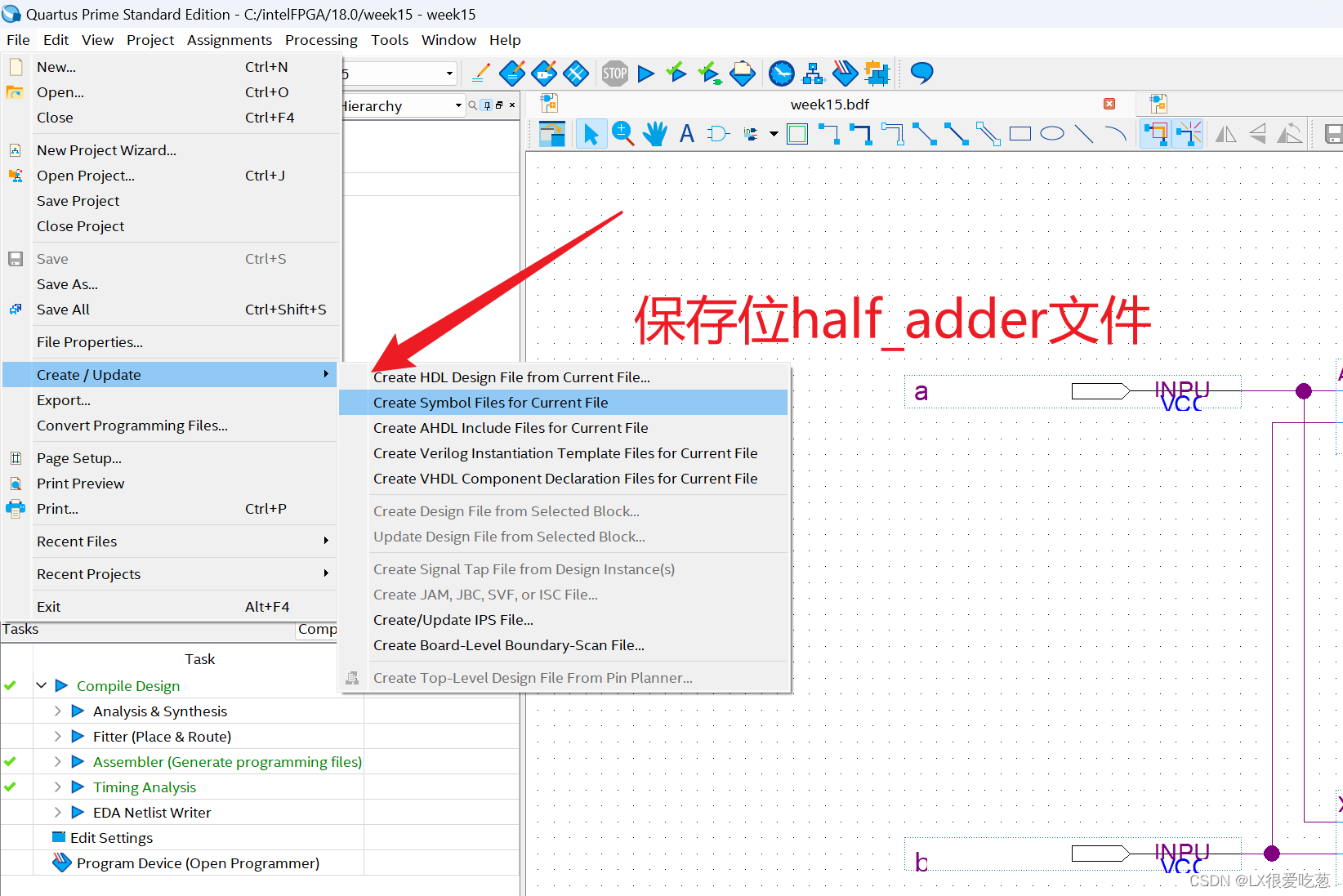

通过之前的知识学习我可以清楚的知道,一位全加器的实现,可以通过半加器的模块加以利用而实现

- 将半加器作为一个模块,供给其他任务调用实现

-

创建文件

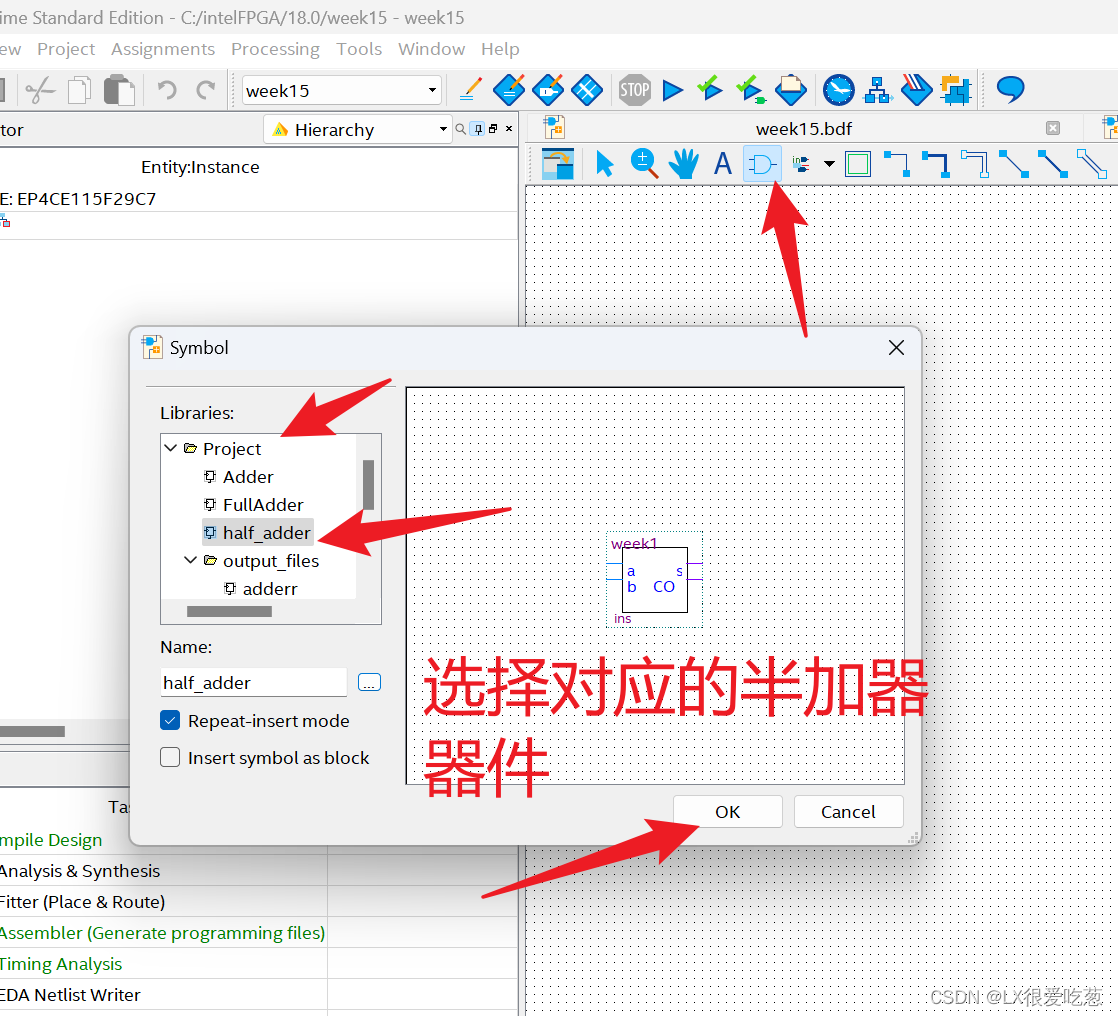

-

选择半加器

-

绘制如下的器件图

-

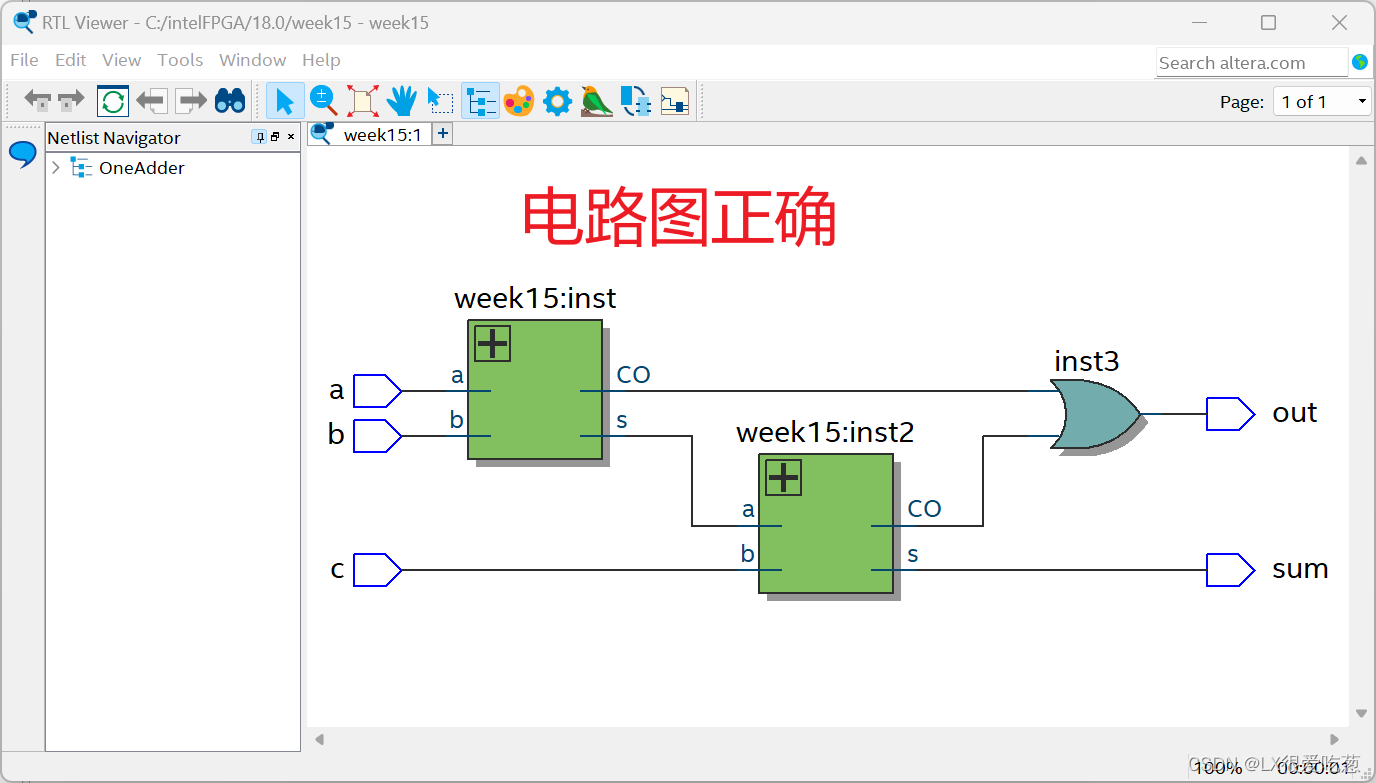

编译查看电路图

-

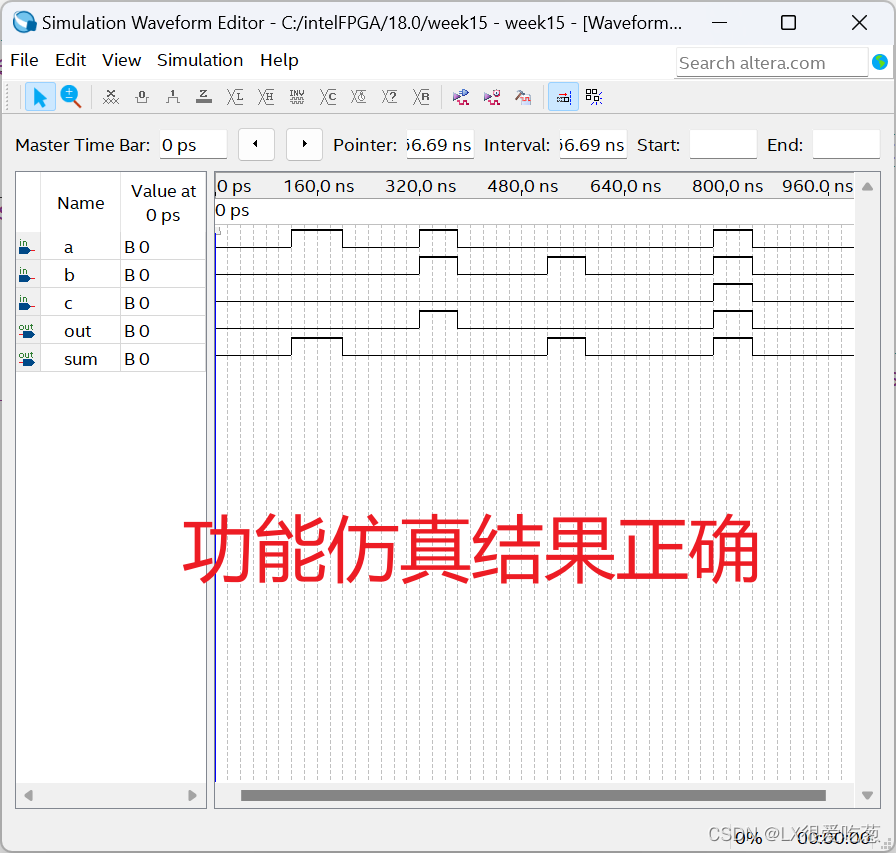

仿真结果图

-

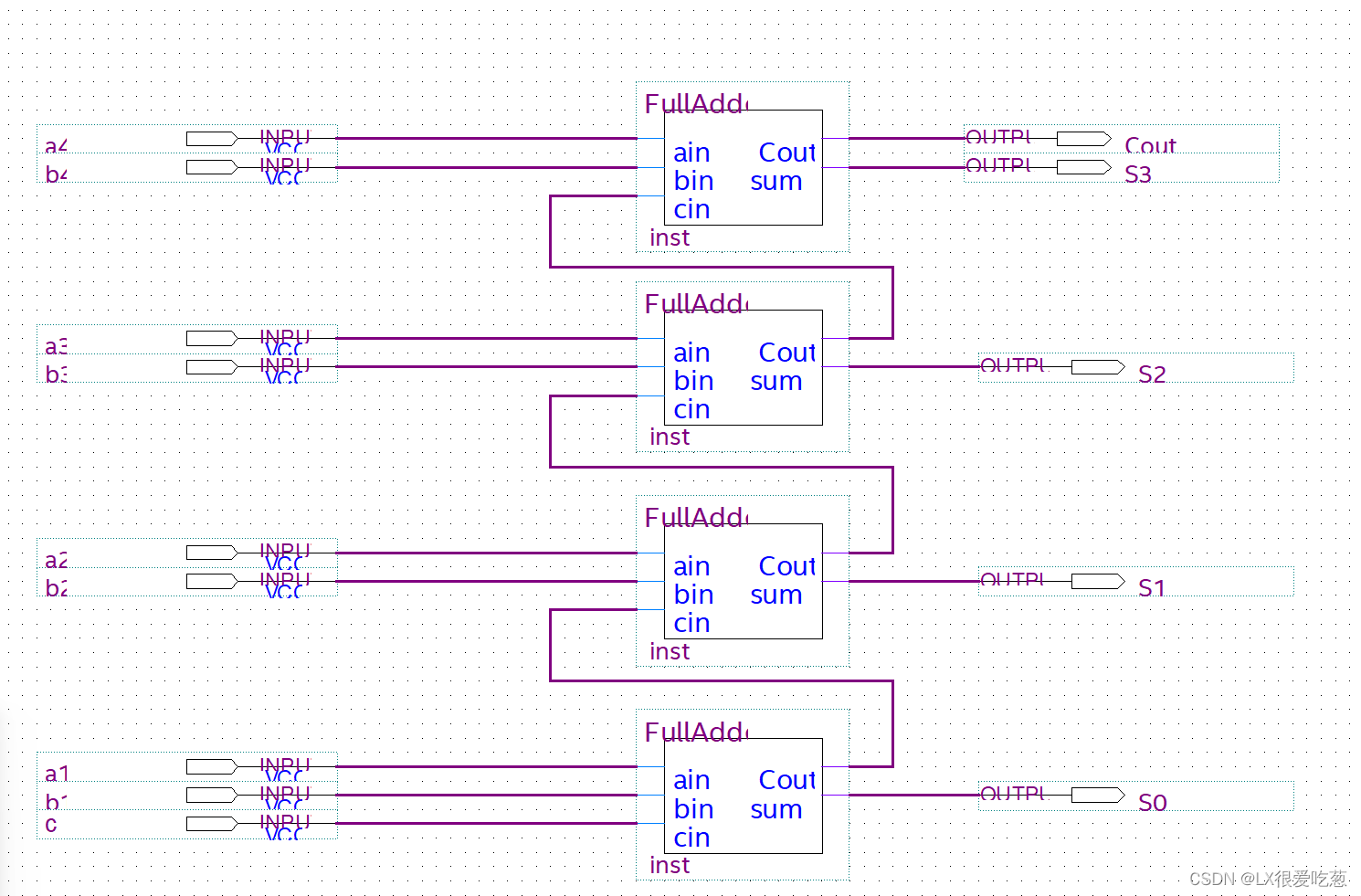

4位全加器的原理图

4位全加器可以由1位全加器组合而成,前面的基本步骤与上述的一致,这边直接给出对应的器件图

半加器的Verilog代码

module half_adder(

input a,

input b,

output sum,

output carry

);

xor(sum, a, b);

and(carry, a, b);

endmodule

1位全加器的Verilog代码

module full_adder_1bit(

input a,

input b,

input cin,

output sum,

output cout

);

wire carry1, carry2;

half_adder ha1(

.a(a),

.b(b),

.sum(sum),

.carry(carry1)

);

half_adder ha2(

.a(sum),

.b(cin),

.sum(sum),

.carry(carry2)

);

or(cout, carry1, carry2);

endmodule

4位全加器的Verilog代码

module full_adder_4bit(

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

wire [3:0] carry;

full_adder_1bit fa0(

.a(a[0]),

.b(b[0]),

.cin(cin),

.sum(sum[0]),

.cout(carry[0])

);

full_adder_1bit fa1(

.a(a[1]),

.b(b[1]),

.cin(carry[0]),

.sum(sum[1]),

.cout(carry[1])

);

full_adder_1bit fa2(

.a(a[2]),

.b(b[2]),

.cin(carry[1]),

.sum(sum[2]),

.cout(carry[2])

);

full_adder_1bit fa3(

.a(a[3]),

.b(b[3]),

.cin(carry[2]),

.sum(sum[3]),

.cout(carry[3])

);

assign cout = carry[3];

endmodule

四.实验过程

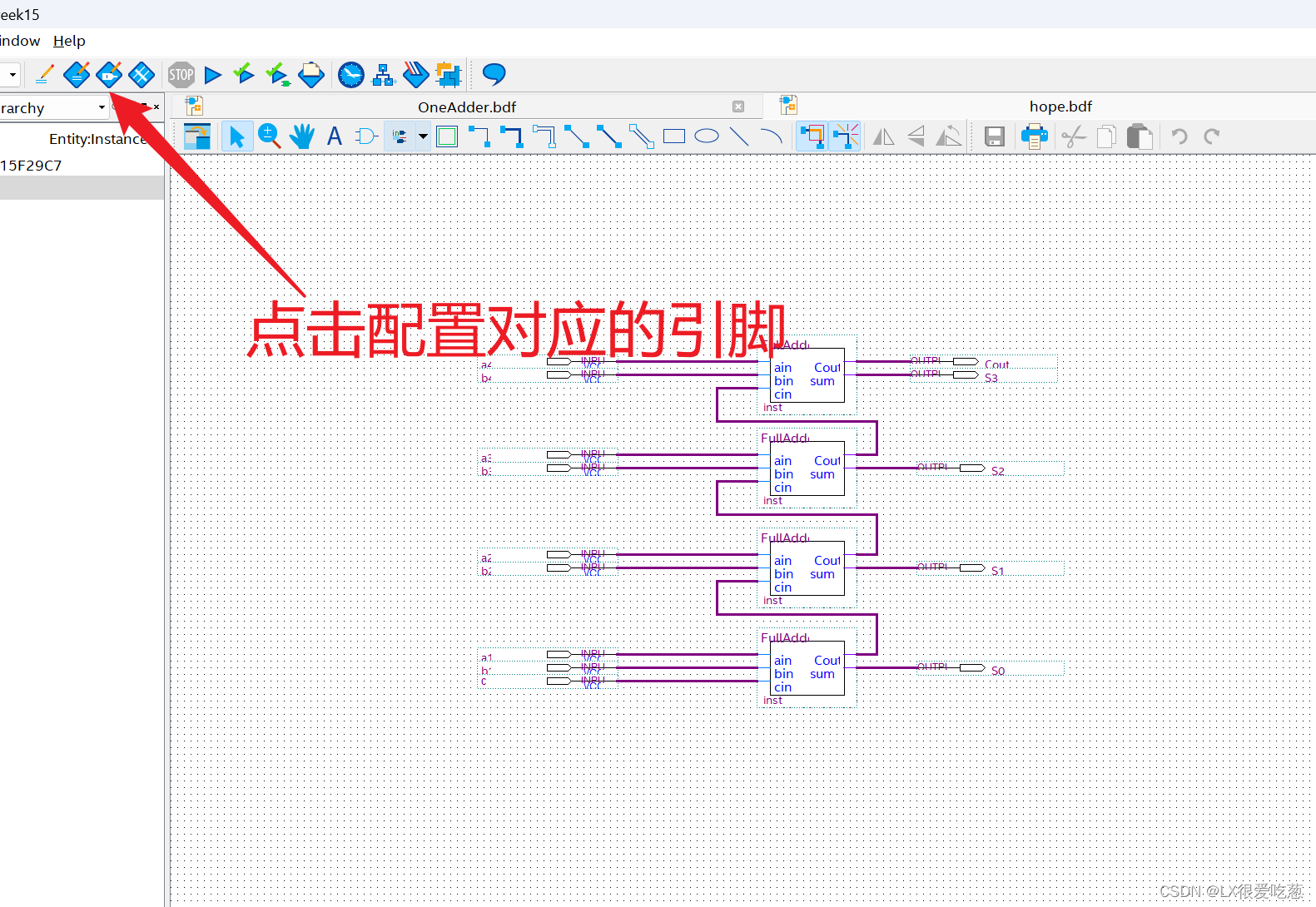

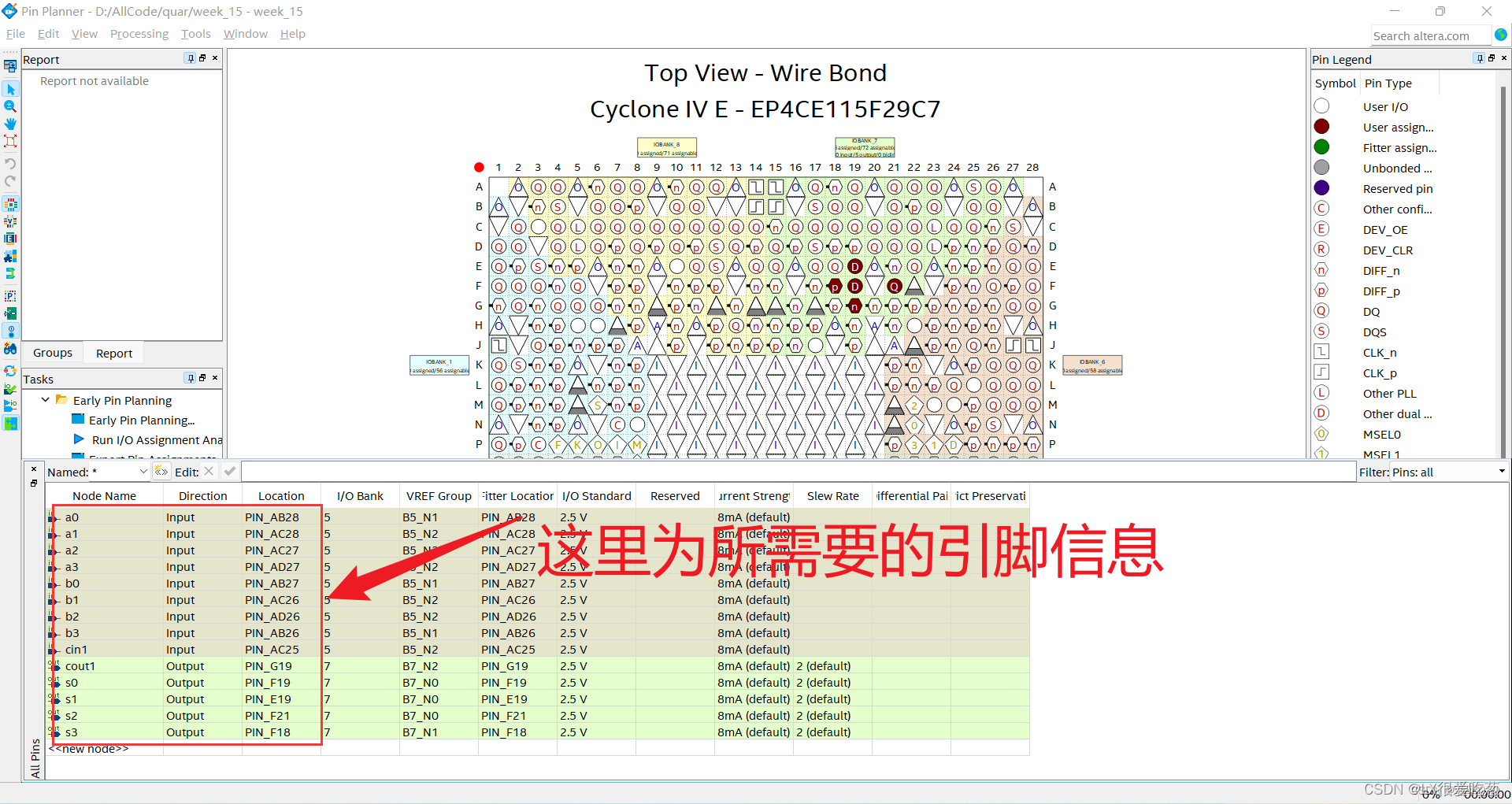

配置芯片引脚

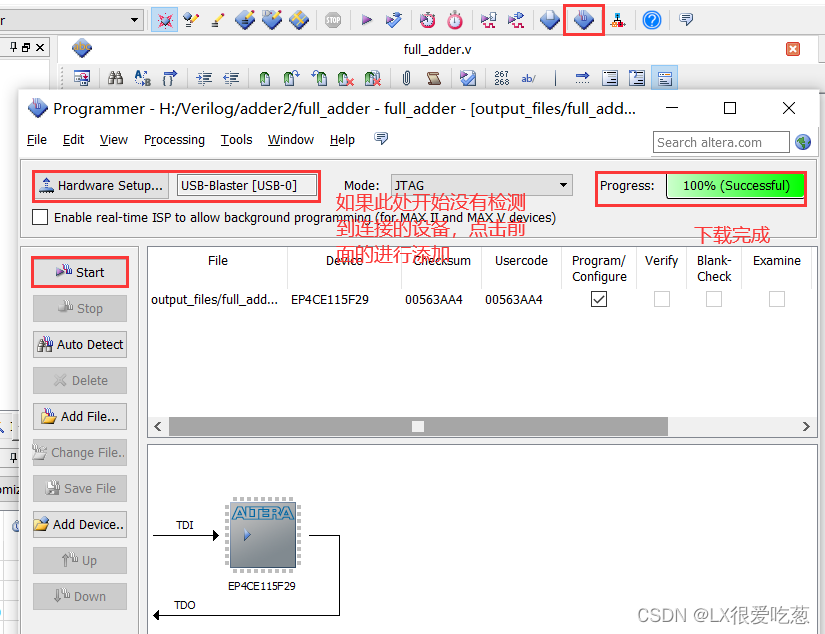

代码下载到板子上

实验结果图

由于实验完成后,没有留下记录,这边截一张图进行说明

- 根据上面的电路图,下面的开关对应这对应的输入信号有无

- 而最上面的Led灯,对应着相应的输出信号

- 下方通过拨动对应的A0,A1,A2,A3,B0,B1,B2,B3,对应着进行着相应的4位全加器的运算

- 可以通过观察上方LED灯的亮灭来判断对应的功能是否实现正确

总结

实验总结:探索数字电路设计与Verilog编程

在本次实验中,我通过Quartus软件进行了1位全加器的设计,采用了两种设计方法:原理图输入和Verilog编程。随后,我通过串行级联四个1位全加器,完成了一个4位全加器的原理图设计。最后,我改用Verilog编程,实现了4位全加器的设计。

1. 1位全加器的设计:

首先,我使用Quartus软件,通过原理图输入和Verilog编程两种方式设计了一个1位全加器。在原理图输入中,我连接了适当的逻辑门和输入/输出引脚,实现了1位全加器的功能。在Verilog编程中,我通过编写Verilog代码,定义了1位全加器的逻辑运算,使其能够正确地进行加法运算。

在初学的过程中,我遇到了一些常见的错误,例如在Verilog中忘记使用分号或在原理图输入中未正确连接输入/输出引脚。通过检查错误消息和调试,我逐渐熟悉了Quartus软件的使用,加深了对数字电路设计的理解。

2. 4位全加器的设计:

接着,我将四个1位全加器进行串行级联,完成了一个4位全加器的原理图设计。然后,我尝试使用Verilog编程,实现了相同的功能。通过这一步骤,我学到了不同的Verilog描述方式,了解了它之间的差异。

3. 实际验证与硬件测试

最后,我使用Modelsim对Verilog代码进行仿真测试,观察了仿真波形图,确保逻辑功能的正确性。随后,我将设计好的4位全加器连接到DE2-115开发板上,进行了引脚绑定、烧录操作。通过拨动按钮开关,我验证了加法器的正确性,并观察了硬件上的实际运行情况。

总结与收获

于实验完成后,没有留下记录,这边截一张图进行说明

[外链图片转存中…(img-9KVXFLyS-1702992624936)]

- 根据上面的电路图,下面的开关对应这对应的输入信号有无

- 而最上面的Led灯,对应着相应的输出信号

- 下方通过拨动对应的A0,A1,A2,A3,B0,B1,B2,B3,对应着进行着相应的4位全加器的运算

- 可以通过观察上方LED灯的亮灭来判断对应的功能是否实现正确

715

715

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?