转载请注明出处:https://blog.csdn.net/Leytton/article/details/90761305

一、导言

在这篇文章里,我将给大家介绍一些门电路基础知识,并利用门电路,搭建一个能保存一位数据的锁存器和D触发器

这是一个系列文章,也是作者的一个分阶段计划。

已完成已完成进行中将上述结构设计组成一个简易版的8位CPU;未开始如果顺利的话,作者将选用一些实际的门电路电子元器件,绘制PCB电路板并造出简易版CPU实物;进行中开发配套的编译软件把汇编语言转换成这个CPU能够运行的二进制数据(对应大学课程《汇编语言》)未开始我们的CPU应该具备USB烧写程序功能,把二进制数据烧写到里面运行;- 开发CPU对应的高级语言暂无打算(对应大学课程《编译原理》);

进行中把这个过程写下来分享给大家。

二、名词约定

1、缩写约定

复位输入:R (Reset)

数据输入:D (Data)

时钟输入:C CLK(Clock)

数据输出:Q (至于为什么不用"O",Out,下面给出了一段有意思的解释)

为什么要用Q呢?这是因为输出的英语是用OUT表示的,简单表示是用O表示的,如果用O表示很容易看错为0。为了不容易看错,德国人就想出了用Q来表示输出的含义了

2、术语约定

(1)高电平和低电平

CPU或MCU芯片有不同的正常工作电压,有5V、3.3V等。一般而言接近工作电压的称为高电平,接近0V(接地)的是低电平;

当然实际情况并不是完全等于工作电压或者完全是0V,会划分一个范围的电压是高电平、另一个范围的是低电平

我的另一篇篇文章有Arduino和STM32芯片的电压划分图:

《Arduino与STM32等单片机读取高电压信号输入》https://leytton.blog.csdn.net/article/details/78398143

在这里演示,我们用1表示高电平,用0表示低电平。

三、基础门电路

与、或、非是三种最基础的门电路,不是很懂的同学可以阅读这篇文章,有形象的介绍:

《继电器是如何成为CPU的(1)》https://blog.csdn.net/Leytton/article/details/90522635

在这里再简单地描述下:

1、与门

全部输入都是高电平,输出才是高电平。

真值表如下:

| 输入D1 | 输入D2 | 输出Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2、或门

只要其中一个输入是高电平,输出就是高电平。

真值表如下:

| 输入D1 | 输入D2 | 输出Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

2、非门

输入高电平,输出低电平;输入低电平,输出高电平。

真值表如下:

| 输入D | 输出Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

四、D锁存器

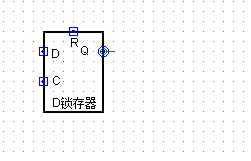

锁存器是靠时钟信号电平触发。下图是D锁存器

- 复位

R=1时,数据输出Q=0;复位R=0时,数据输出Q由数据输入D和时钟输入C决定 R=0时,若C=0,则Q=0;若C=1,则Q=D

总而言之就是不是复位的情况下,时钟输入为高电平,则数据输入才能有效输出

真值表如下:

| 复位R | 时钟输入C | 数据输入D | 数据输出Q |

|---|---|---|---|

| 1 | X | X | 0 |

| 0 | 0 | X | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

我们把锁存器封装一下,只留输入输出,方便后面复用

五、D触发器

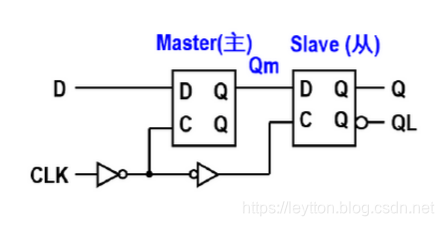

触发器是靠时钟信号的边沿触发。下图为上升沿触发有效的D触发器:

当时钟信号由低电平变成高电平的瞬间,把数据输入保存起来。

下图有个网上找的静态图(出处):

CLK=0时,主锁存器工作,接收输入信号Qm = D;从锁存器不工作,输出 Q 保持不变。

CLK=1时,主锁存器不工作,Qm保持不变;从锁存器工作,将Qm传送到输出端。

在设计时我用的是下降沿触发的D寄存器:

当时钟信号由高电平变成低电平的瞬间,把数据输入保存起来。

六、相关软件

感谢下列作者提供优秀的软件帮助我们方便研究以及更好地展示作品 ?

1、电路仿真:Logisim

逻辑电路仿真软件,能帮助你对数字逻辑电路和计算机组成原理有更深刻的理解。万丈高楼平地起,你可以使用它出神入化地设计出简易的CPU来。

下载地址:https://download.csdn.net/download/leytton/11225068

2、GIF动图录制:LICEcap

1M不到的GIF动画录制软件,亲测不掉色不失真,生成动图体积小,现在博客文章里可以配上动图啦

下载地址:https://download.csdn.net/download/leytton/11225078

1442

1442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?