Verilog 函数

关键词:函数,大小端转换,数码管译码

在 Verilog 中,可以利用任务(关键字为 task)或函数(关键字为 function),将重复性的行为级设计进行提取,并在多个地方调用,来避免重复代码的多次编写,使代码更加的简洁、易懂。

函数

函数只能在模块中定义,位置任意,并在模块的任何地方引用,作用范围也局限于此模块。函数主要有以下几个特点:

1)不含有任何延迟、时序或时序控制逻辑

2)至少有一个输入变量

3)只有一个返回值,且没有输出

4)不含有非阻塞赋值语句

5)函数可以调用其他函数,但是不能调用任务

Verilog 函数声明格式如下:

function [range-1:0] function_id ;

input_declaration ;

other_declaration ;

procedural_statement ;

endfunction

函数在声明时,会隐式的声明一个宽度为 range、 名字为 function_id 的寄存器变量,函数的返回值通过这个变量进行传递。当该寄存器变量没有指定位宽时,默认位宽为 1。

函数通过指明函数名与输入变量进行调用。函数结束时,返回值被传递到调用处。

函数调用格式如下:

function_id(input1, input2, …);

下面用函数实现一个数据大小端转换的功能。

当输入为 4’b0011 时,输出可为 4’b1100。例如:

module endian_rvs

#(parameter N = 4)

(

input en, //enable control

input [N-1:0] a ,

output [N-1:0] b

);

reg [N-1:0] b_temp ;

always @(*) begin

if (en) begin

b_temp = data_rvs(a);

end

else begin

b_temp = 0 ;

end

end

assign b = b_temp ;

//function entity

function [N-1:0] data_rvs ;

input [N-1:0] data_in ;

parameter MASK = 32'h3 ;

integer k ;

begin

for(k=0; k<N; k=k+1) begin

data_rvs[N-k-1] = data_in[k] ;

end

end

endfunction

endmodule

automatic 函数

在 Verilog 中,一般函数的局部变量是静态的,即函数的每次调用,函数的局部变量都会使用同一个存储空间。若某个函数在两个不同的地方同时并发的调用,那么两个函数调用行为同时对同一块地址进行操作,会导致不确定的函数结果。

Verilog 用关键字 automatic 来对函数进行说明,此类函数在调用时是可以自动分配新的内存空间的,也可以理解为是可递归的。因此,automatic 函数中声明的局部变量不能通过层次命名进行访问,但是 automatic 函数本身可以通过层次名进行调用。

下面用 automatic 函数,实现阶乘计算:

wire [31:0] results3 = factorial(4);

function automatic integer factorial ;

input integer data ;

integer i ;

begin

factorial = (data>=2)? data * factorial(data-1) : 1 ;

end

endfunction // factorial

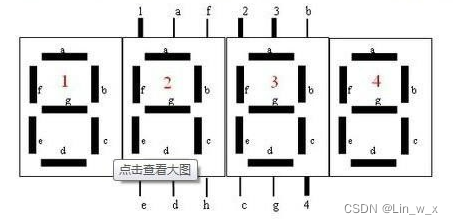

数码管译码

module digital_tube

(

input clk ,

input rstn ,

input en ,

input [3:0] single_digit ,

input [3:0] ten_digit ,

input [3:0] hundred_digit ,

input [3:0] kilo_digit ,

output reg [3:0] csn , //chip select, low-available

output reg [6:0] abcdefg //light control

);

reg [1:0] scan_r ; //scan_ctrl

always @ (posedge clk or negedge rstn) begin

if(!rstn)begin

csn <= 4'b1111;

abcdefg <= 'd0;

scan_r <= 3'd0;

end

else if (en) begin

case(scan_r)

2'd0:begin

scan_r <= 3'd1;

csn <= 4'b0111; //select single digit

abcdefg <= dt_translate(single_digit);

end

2'd1:begin

scan_r <= 3'd2;

csn <= 4'b1011; //select ten digit

abcdefg <= dt_translate(ten_digit);

end

2'd2:begin

scan_r <= 3'd3;

csn <= 4'b1101; //select hundred digit

abcdefg <= dt_translate(hundred_digit);

end

2'd3:begin

scan_r <= 3'd0;

csn <= 4'b1110; //select kilo digit

abcdefg <= dt_translate(kilo_digit);

end

endcase

end

end

/*------------ translate function -------*/

function [6:0] dt_translate;

input [3:0] data;

begin

case(data)

4'd0: dt_translate = 7'b1111110; //number 0 -> 0x7e

4'd1: dt_translate = 7'b0110000; //number 1 -> 0x30

4'd2: dt_translate = 7'b1101101; //number 2 -> 0x6d

4'd3: dt_translate = 7'b1111001; //number 3 -> 0x79

4'd4: dt_translate = 7'b0110011; //number 4 -> 0x33

4'd5: dt_translate = 7'b1011011; //number 5 -> 0x5b

4'd6: dt_translate = 7'b1011111; //number 6 -> 0x5f

4'd7: dt_translate = 7'b1110000; //number 7 -> 0x70

4'd8: dt_translate = 7'b1111111; //number 8 -> 0x7f

4'd9: dt_translate = 7'b1111011; //number 9 -> 0x7b

endcase

end

endfunction

endmodule

Verilog 任务

关键词:任务

任务与函数的区别

和函数一样,任务(task)可以用来描述共同的代码段,并在模块内任意位置被调用,让代码更加的直观易读。函数一般用于组合逻辑的各种转换和计算,而任务更像一个过程,不仅能完成函数的功能,还可以包含时序控制逻辑。下面对任务与函数的区别进行概括:

| 比较点 | 函数 | 任务 |

|---|---|---|

| 输入 | 函数至少有一个输入,端口声明不能包含 inout 型 | 任务可以没有或者有多个输入,且端口声明可以为 inout 型 |

| 输出 | 函数没有输出 | 任务可以没有或者有多个输出 |

| 返回值 | 函数至少有一个返回值 | 任务**没有返回值 ** |

| 仿真时刻 | 函数总在零时刻就开始执行 | 任务可以在非零时刻执行 |

| 时序逻辑 | 函数不能包含任何时序控制逻辑 | 任务不能出现 always 语句,但可以包含其他时序控制,如延时语句 |

| 调用 | 函数只能调用函数,不能调用任务 | 任务可以调用函数和任务 |

| 书写规范 | 函数不能单独作为一条语句出现,只能放在赋值语言的右端 | 任务可以作为一条单独的语句出现语句块中 |

任务

任务声明

任务在模块中任意位置定义,并在模块内任意位置引用,作用范围也局限于此模块。

模块内子程序出现下面任意一个条件时,则必须使用任务而不能使用函数。

1)子程序中包含时序控制逻辑,例如延迟,事件控制等

2)没有输入变量

3)没有输出或输出端的数量大于 1

Verilog 任务声明格式如下:

task task_id ;

port_declaration ;

procedural_statement ;

endtask

例如,一个带延时的异或功能 task 描述如下:

task xor_oper_iner;

input [N-1:0] numa;

input [N-1:0] numb;

output [N-1:0] numco ;

//output reg [N-1:0] numco ; //无需再注明 reg 类型,虽然注明也可能没错

#3 numco = numa ^ numb ;

//assign #3 numco = numa ^ numb ; //不用assign,因为输出默认是reg

endtask

任务在声明时,也可以在任务名后面加一个括号,将端口声明包起来。

上述设计可以更改为:

task xor_oper_iner(

input [N-1:0] numa,

input [N-1:0] numb,

output [N-1:0] numco ) ;

#3 numco = numa ^ numb ;

endtask

任务调用时,端口必须按顺序对应。

输入端连接的模块内信号可以是 wire 型,也可以是 reg 型。输出端连接的模块内信号要求一定是 reg 型,这点需要注意。

对上述异或功能的 task 进行一个调用,完成对异或结果的缓存。

module xor_oper

#(parameter N = 4)

(

input clk ,

input rstn ,

input [N-1:0] a ,

input [N-1:0] b ,

output [N-1:0] co );

reg [N-1:0] co_t ;

always @(*) begin //任务调用

xor_oper_iner(a, b, co_t);

end

reg [N-1:0] co_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

co_r <= 'b0 ;

end

else begin

co_r <= co_t ; //数据缓存

end

end

assign co = co_r ;

/*------------ task -------*/

task xor_oper_iner;

input [N-1:0] numa;

input [N-1:0] numb;

output [N-1:0] numco ;

#3 numco = numa ^ numb ; //阻塞赋值,易于控制时序

endtask

endmodule

任务操作全局变量

任务内部变量也只有在任务中可见,如果想具体观察任务中对变量的操作过程,需要将观察的变量声明在模块之内、任务之外,可谓之"全局变量"。

例如有以下 2 种尝试利用 task 产生时钟的描述方式。

//way1 to decirbe clk generating, not work

task clk_rvs_iner ;

output clk_no_rvs ;

# 5 ; clk_no_rvs = 0 ;

# 5 ; clk_no_rvs = 1 ;

endtask

reg clk_test1 ;

always clk_rvs_iner(clk_test1);

//way2: use task to operate global varialbes to generating clk

reg clk_test2 ;

task clk_rvs_global ;

# 5 ; clk_test2 = 0 ;

# 5 ; clk_test2 = 1 ;

endtask // clk_rvs_iner

always clk_rvs_global;

automatic 任务

和函数一样,Verilog 中任务调用时的局部变量都是静态的。可以用关键字 automatic 来对任务进行声明,那么任务调用时各存储空间就可以动态分配,每个调用的任务都各自独立的对自己独有的地址空间进行操作,而不影响多个相同任务调用时的并发执行。

如果一任务代码段被 2 处及以上调用,一定要用关键字 automatic 声明。

task automatic test_flag ;

input [3:0] cnti ;

input en ;

output [3:0] cnto ;

if (en) cnto = cnti ;

endtask

reg en_cnt ;

reg [3:0] cnt_temp ;

initial begin

en_cnt = 1 ;

cnt_temp = 0 ;

#25 ; en_cnt = 0 ;

end

always #10 cnt_temp = cnt_temp + 1 ;

reg [3:0] cnt1, cnt2 ;

always @(posedge clk) test_flag(2, en_cnt, cnt1); //task(1)

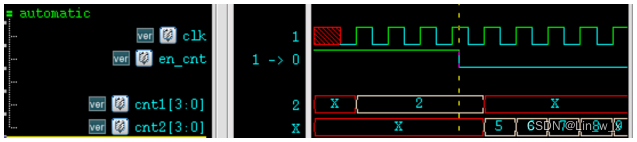

此时仿真结果如下。

en_cnt 为高时,任务 (1) 中信号 cnt1 能输出正确的逻辑值,任务 (2) 中信号 cnt2 的值为 X;

en_cnt 为低时,任务 (2) 中信号 cnt2 能输出正确的逻辑值,任务 (1) 中信号 cnt1 的值为 X;

Verilog 状态机

关键词:状态机,售卖机

有限状态机(Finite-State Machine,FSM),简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。状态机不仅是一种电路的描述工具,而且也是一种思想方法,在电路设计的系统级和 RTL 级有着广泛的应用。

状态机类型

Verilog 中状态机主要用于同步时序逻辑的设计,能够在有限个状态之间按一定要求和规律切换时序电路的状态。状态的切换方向不但取决于各个输入值,还取决于当前所在状态。 状态机可分为 2 类:Moore 状态机和 Mealy 状态机。

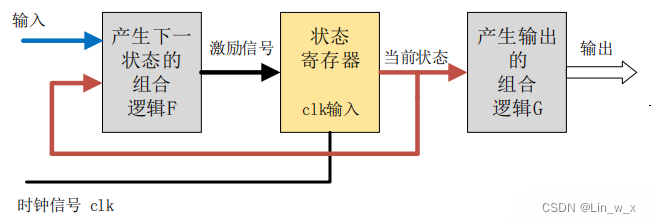

Moore 型状态机

Moore 型状态机的输出只与当前状态有关,与当前输入无关。

输出会在一个完整的时钟周期内保持稳定,即使此时输入信号有变化,输出也不会变化。输入对输出的影响要到下一个时钟周期才能反映出来。这也是 Moore 型状态机的一个重要特点:输入与输出是隔离开来的。

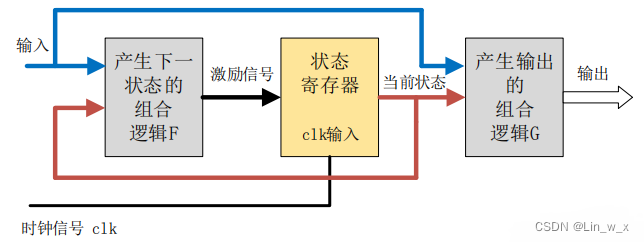

Mealy 型状态机

Mealy 型状态机的输出,不仅与当前状态有关,还取决于当前的输入信号。

Mealy 型状态机的输出是在输入信号变化以后立刻发生变化,且输入变化可能出现在任何状态的时钟周期内。因此,同种逻辑下,Mealy 型状态机输出对输入的响应会比 Moore 型状态机早一个时钟周期。

状态机设计流程

根据设计需求画出状态转移图,确定使用状态机类型,并标注出各种输入输出信号,更有助于编程。一般使用最多的是 Mealy 型 3 段式状态机。

状态机设计:3 段式(推荐)

状态机设计如下:

(0) 首先,根据状态机的个数确定状态机编码。利用编码给状态寄存器赋值,代码可读性更好。

(1) 状态机第一段,时序逻辑,非阻塞赋值,传递寄存器的状态。

(2) 状态机第二段,组合逻辑,阻塞赋值,根据当前状态和当前输入,确定下一个状态机的状态。

(3) 状态机第三代,时序逻辑,非阻塞赋值,因为是 Mealy 型状态机,根据当前状态和当前输入,确定输出信号。

Verilog 竞争与冒险

关键字:竞争,冒险,书写规范

产生原因

数字电路中,信号传输与状态变换时都会有一定的延时。

在组合逻辑电路中,不同路径的输入信号变化传输到同一点门级电路时,在时间上有先有后,这种先后所形成的时间差称为竞争(Competition)。

由于竞争的存在,输出信号需要经过一段时间才能达到期望状态,过渡时间内可能产生瞬间的错误输出,例如尖峰脉冲。这种现象被称为冒险(Hazard)。

竞争不一定有冒险,但冒险一定会有竞争。

消除方法

对数字电路来说,常见的避免竞争与冒险的方法主要有 4 种。

1)增加滤波电容,滤除窄脉冲

此种方法需要在输出端并联一个小电容,将尖峰脉冲的幅度削弱至门电路阈值以下。

此方法虽然简单,但是会增加输出电压的翻转时间,易破坏波形。

2)修改逻辑,增加冗余项

利用卡诺图,在两个相切的圆之间,增加一个卡诺圈,并加在逻辑表达式之中。

3)使用时钟同步电路,利用触发器进行打拍延迟

同步电路信号的变化都发生在时钟边沿。对于触发器的 D 输入端,只要毛刺不出现在时钟的上升沿并且不满足数据的建立和保持时间,就不会对系统造成危害,因此可认为 D 触发器的 D 输入端对毛刺不敏感。 利用此特性,在时钟边沿驱动下,对一个组合逻辑信号进行延迟打拍,可消除竞争冒险。

延迟一拍时钟时,会一定概率的减少竞争冒险的出现。实验表明,最安全的打拍延迟周期是 3 拍,可有效减少竞争冒险的出现。

当然,最终还是需要根据自己的设计需求,对信号进行合理的打拍延迟。

4)采用格雷码计数器

递加的多 bit 位计数器,计数值有时候会发生多个 bit 位的跳变。

例如计数器变量 counter 从 5 计数到 6 时, 对应二进制数字为 4’b101 到 4’b110 的转换。因为各 bit 数据位的延时,counter 的变换过程可能是: 4’b101 -> 4’b111 -> 4’b110。如果有以下逻辑描述,则信号 cout 可能出现短暂的尖峰脉冲,这显然是与设计相悖的。

而格雷码计数器,计数时相邻的数之间只有一个数据 bit 发生了变化,所以能有效的避免竞争冒险。

Verilog 书写规范

在编程时多注意以下几点,也可以避免大多数的竞争与冒险问题。

1)时序电路建模时,用非阻塞赋值。

2)组合逻辑建模时,用阻塞赋值。

3)在同一个 always 块中建立时序和组合逻辑模型时,用非阻塞赋值。

4)在同一个 always 块中不要既使用阻塞赋值又使用非阻塞赋值。

5)不要在多个 always 块中为同一个变量赋值。

6)避免 latch 产生。

1)时序电路建模时,用非阻塞赋值

前面讲述非阻塞赋值时就陈述过,时序电路中非阻塞赋值可以消除竞争冒险。

例如下面代码描述,由于无法确定 a 与 b 阻塞赋值的操作顺序,就有可能带来竞争冒险。

always @(posedge clk) begin

a = b ;

b = a ;

end

而使用非阻塞赋值时,赋值操作是同时进行的,所以就不会带来竞争冒险,如以下代码描述。

always @(posedge clk) begin

a <= b ;

b <= a ;

end

2)组合逻辑建模时,用阻塞赋值

例如,我们想实现 C = A&B, F=C&D 的组合逻辑功能,用非阻塞赋值语句如下。

两条赋值语句同时赋值,F <= C & D 中使用的是信号 C 的旧值,所以导致此时的逻辑是错误的,F 的逻辑值不等于 A&B&D。

而且,此时要求信号 C 具有存储功能,但不是时钟驱动,所以 C 可能会被综合成锁存器(latch),导致竞争冒险。

always @(*) begin

C <= A & B ;

F <= C & D ;

end

对代码进行如下修改,F = C & D 的操作一定是在 C = A & B 之后,此时 F 的逻辑值等于 A&B&D,符合设计。

always @(*) begin

C = A & B ;

F = C & D ;

end

3)在同一个 always 块中建立时序和组合逻辑模型时,用非阻塞赋值

虽然时序电路中可能涉及组合逻辑,但是如果赋值操作使用非阻塞赋值,仍然会导致如规范 1 中所涉及的类似问题。

例如在时钟驱动下完成一个与门的逻辑功能,代码参考如下。

always @(posedge clk or negedge rst_n)

if (!rst_n) begin

q <= 1'b0;

end

else begin

q <= a & b; //即便有组合逻辑,也不要写成:q = a & b

end

end

4)在同一个 always 块中不要既使用阻塞赋值又使用非阻塞赋值

always 涉及的组合逻辑中,既有阻塞赋值又有非阻塞赋值时,会导致意外的结果,例如下面代码描述。

此时信号 C 阻塞赋值完毕以后,信号 F 才会被非阻塞赋值,仿真结果可能正确。

但如果 F 信号有其他的负载,F 的最新值并不能马上传递出去,数据有效时间还是在下一个触发时刻。此时要求 F 具有存储功能,可能会被综合成 latch,导致竞争冒险。

5)不要在多个 always 块中为同一个变量赋值

与 C 语言有所不同,Verilog 中不允许在多个 always 块中为同一个变量赋值。此时信号拥有多驱动端(Multiple Driver),是禁止的。当然,也不允许 assign 语句为同一个变量进行多次连线赋值。 从信号角度来讲,多驱动时,同一个信号变量在很短的时间内进行多次不同的赋值结果,就有可能产生竞争冒险。

从语法来讲,很多编译器检测到多驱动时,也会报 Error。

6)避免 latch 产生

为避免 latch 的产生,在组合逻辑中,需要注意以下几点:

(1)if-else 或 case 语句,结构一定要完整(补全if-else结构,case-default结构)

(2)不要将赋值信号放在赋值源头,或条件判断中(增加一个always块将信号延时一个时钟周期)

(3)敏感信号列表建议多用 always@(*)

Verilog 仿真激励

关键词:testbench,仿真,文件读写

Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

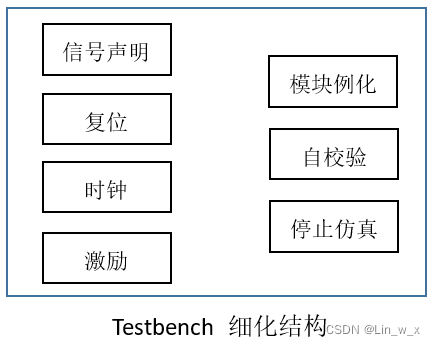

testbench 结构划分

testbench 一般结构如下:

其实 testbench 最基本的结构包括信号声明、激励和模块例化。

根据设计的复杂度,需要引入时钟和复位部分。当然更为复杂的设计,激励部分也会更加复杂。根据自己的验证需求,选择是否需要自校验和停止仿真部分。

当然,复位和时钟产生部分,也可以看做激励,所以它们都可以在一个语句块中实现。也可以拿自校验的结果,作为结束仿真的条件。

testbench 具体分析

1)信号声明

testbench 模块声明时,一般不需要声明端口。因为激励信号一般都在 testbench 模块内部,没有外部信号。

声明的变量应该能全部对应被测试模块的端口。当然,变量不一定要与被测试模块端口名字一样。但是被测试模块输入端对应的变量应该声明为 reg 型,如 clk,rstn 等,输出端对应的变量应该声明为 wire 型,如 dout,dout_en。

2)时钟生成

生成时钟的方式有很多种,例如以下两种生成方式也可以借鉴。

initial clk = 0 ;

always #(CYCLE_200MHz/2) clk = ~clk;

initial begin

clk = 0 ;

forever begin

#(CYCLE_200MHz/2) clk = ~clk;

end

end

3)复位生成

复位逻辑比较简单,一般赋初值为 0,再经过一段小延迟后,复位为 1 即可。

这里大多数的仿真都是用的低有效复位。

4)激励部分

激励部分该产生怎样的输入信号,是根据被测模块的需要来设计的。

5)模块例化

利用 testbench 开始声明的信号变量,对被测试模块进行例化连接。

6)自校验

如果设计比较简单,完全可以通过输入、输出信号的波形来确定设计是否正确,此部分完全可以删除。如果数据很多,有时候拿肉眼观察并不能对设计的正确性进行一个有效判定。此时加入一个自校验模块,会大大增加仿真的效率。

7)结束仿真

如果我们不加入结束仿真部分,仿真就会无限制的运行下去,波形太长有时候并不方便分析。Verilog 中提供了系统任务 $finish 来停止仿真。

停止仿真之前,可以将自校验的结果,通过系统任务 $display 在终端进行显示。

Verilog 数值转换

本节主要对有符号数的十进制与二进制表示以及一些数值变换进行简单的总结。

定义一个宽度为 DW 的二进制补码格式的数据 dbin ,其表示的有符号十进制数字为 ddec 。

reg [DW-1:0] dbin ;

1. 十进制有符号数转二进制补码

正数的补码为原码。

假如十进制数 ddec 为负数,则计算其对应的二进制补码的方法主要有 2 种:

将ddec 最高位符号位改写为 1,剩余数值部分取反加一

例如,4bit 数字 -6 的数值部分为 4’b0110,取反加一后为 4’b0010,高位改写后为 4’b1010。

dbin = {1'b1, ~3'b110 + 3'b1} ; //4'b1010

将负数 ddec 直接与其代表的最大数值范围数相加(有人称之为模数)

例如,4bit 数字 -6 与 16(2 的 4 次幂)的和为 10, 即对应 4’b1010。

dbin = ddec + (1<<4) ; //4'b1010

2. 二级制补码转十进制有符号数

当 dbin 最高位为 0 时,其数值大小即为其表示的十进制正数。

当 dbin 最高位为 1 时,计算其表示的十进制有符号数方法主要有 2 种:

将 dbin 取反加一,并增加符号位

例如,4bit 数字 -6 的补码为 4’b1010,取反加一后为 4’b0110,增加符号位后为 -6。

ddec = -(~4'b1010 + 1'b1) ; //-6

将 dbin 代表的无符号数值与其代表的最大数值范围数直接相减

例如,4bit 数字 -6 的补码为 4’b1010,即无符号数值为 10,10 减 16 便可得到 -6 。

ddec = dbin - (1<<4) ; //-6

3. 绝对值

求 dbin 的绝对值逻辑如下:

dbin_abs = (dbin[DW-1]? ~dbin : dbin) + 1'b1 ;

例如,4bit 数字 -6 的补码为 4’b1010,取反加 1 后的值为 4’b0110(6),即为 -6 的绝对值。

但如果 dbin 为正数,加 1 后的值比其真正的绝对值要大 1,此步操作只是为了让正数部分的绝对值数量与负数部分一致。因为一定位宽下,由于 0 值的存在,有符号数表示的负数数量会比正数多 1 个。

4. 有符号数转无符号数

将有符号数扩展成为无符号数的逻辑如下:

dbin_unsigned = {!dbin[DW-1], dbin[DW-2:0]} ;

例如:

4'b1010 (-6) -> 4'b0010 (2),4'b0010 (2) -> 4'b1010 (10)

其实转换原则是将数据代表的数值范围移动到 0 以上,有符号数转换成无符号数之后,数据相对间的差并没有改变。

5. 扩展符号位

计算时有时会根据需要对有符号数位宽进行扩展。假设位宽增量为 W,扩展逻辑如下:

dbin_extend = {{(W){dbin[DW-1]}}, dbin} ;

扩展原则就是将信号代表符号位的最高位,填充至扩展的高位数据位中。

例如 4’b1010 (-6) 扩展到 8bit 为 8’b11111010,计算其对应的负数仍然是 -6。

,即为 -6 的绝对值。

但如果 dbin 为正数,加 1 后的值比其真正的绝对值要大 1,此步操作只是为了让正数部分的绝对值数量与负数部分一致。因为一定位宽下,由于 0 值的存在,有符号数表示的负数数量会比正数多 1 个。

4. 有符号数转无符号数

将有符号数扩展成为无符号数的逻辑如下:

dbin_unsigned = {!dbin[DW-1], dbin[DW-2:0]} ;

例如:

4'b1010 (-6) -> 4'b0010 (2),4'b0010 (2) -> 4'b1010 (10)

其实转换原则是将数据代表的数值范围移动到 0 以上,有符号数转换成无符号数之后,数据相对间的差并没有改变。

5. 扩展符号位

计算时有时会根据需要对有符号数位宽进行扩展。假设位宽增量为 W,扩展逻辑如下:

dbin_extend = {{(W){dbin[DW-1]}}, dbin} ;

扩展原则就是将信号代表符号位的最高位,填充至扩展的高位数据位中。

例如 4’b1010 (-6) 扩展到 8bit 为 8’b11111010,计算其对应的负数仍然是 -6。

3438

3438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?