目录

(1) 由于是直接购买现成的开发板作为项目前期开发调试使用,故DDR3芯片已板载,其型号为MT41J256M16HA-125,美光公司生产的4Gb容量DDR3芯片。采用2片DDR3芯片并联模式,即共用地址信号线、控制信号线,数据信号线进行扩展为单片位宽的2倍。那么,如果采用4片进行并联连接,则位宽扩展为4倍。(FPGA关于DDR3控制器的上限物理数据管脚位宽为72位,故原理图设计时,不要超过该上限即可。)

(2)虽说开发板厂家已确保硬件设计完美可靠,但是作为用户开发者,至少还是需要弄明确厂家的设计人员设计思路及参考依据。本质上就是想象自己重新设计硬件原理图。开发板DDR3芯片及控制部分原理图如下所示。(采用的是黑金开发板)

(3)原理图分析。

供电电源:DDR3芯片采用1.5V电源供电,还有低电压DDR3芯片是1.35V供电。故VDD、VDDQ均为1.5V,VSS均接地。

参考电压:数据信号线参考电压 VREFDQ,地址信号及控制信号参考电压VREFCA,均为0.5* VDD。

输入时钟:DDR3芯片采用差分输入时钟,可以由外部有源晶振直接提供,还可以由源端FPGA提供,采用后者更灵活。

例如: -125速率等级的DDR3芯片上限工作频率为1600M T/s,用户可以使其工作在1200M,1000M, 800M等等。故采用FPGA提供DDR3的工作时钟。

注意:工作频率1600M T/s ≠ ≠ 1600Mb/s,因为在FPGA的MIG控制器中,会写成Mb/s,造成初学者的误解。因为如果当前DDR3芯片的DQ数据管脚位宽为x16,工作频率为1600M T/s,那么该DDR3芯片极限带宽为:1600x16Mb/s,所以二者是不相等的单位。

几个重要的物理参数见上图所示,具体含义可以参考博文:http://blog.chinaaet.com/justlxy/p/5100051913

关于DDR3芯片还有两个重要的概念:预加载Prefetch, 突发长度Burst Length

所谓prefetch,就是预加载,这是DDR时代提出的技术。在SDR中,并没有这一技术,所以其每一个cell的存储容量等于DQ的宽度(芯片数据IO位宽)。【关于什么是cell(存储单元参考博文:http://blog.chinaaet.com/justlxy/p/5100051913 )】

进入DDR时代之后,就有了prefetch技术,DDR是两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。DDR2是四位预取(4-bit Prefetch),DDR3和DDR4都是八位预取(8-bit Prefetch)。而8-bit Prefetch可以使得内核时钟是DDR时钟的四分之一,这也是Prefetch的根本意义所在。

Burst Lengths,简称BL,指突发长度,突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期数。上一部分讲到的Burst Type和Burst Order实际上就是关于Burst Length的读写顺序的配置。在DDR3 SDRAM时代,内部配置采用了8n prefetch(预取)来实现高速读写.这也导致了DDR3的Burst Length一般都是8。当然也有Bursth ength为4的设置(BC4),是指另外4笔数据是不被传输的或者被认为无效而已。在DDR2时代,内部配置采用的是4n prefetch,Burst length有4和8两种,对于BL=8的读写操作,会出现两次4n Prefetch的动作。

参考博文:http://blog.chinaaet.com/justlxy/p/5100052027

3. 新旧两代DDR3 控制器对比 — MIS vs MIG

上一代MIG控制器 — Spartan6系列

由上一代MIG控制器可知: 写指令操作 和 写数据或读数据操作是完全独立的,二者之间没有相互联系,时序控制容易实现。

cmd_bl连续指令写入的长度限制为2^6=64,故MIG单次连续写操作和连续读操作的数据长度上限为64,这个限制其实是由指令缓存FIFO的存储深度决定的。

新一代MIS控制器 — 7系列FPGA等

由上图可知,新一代MIS控制器写指令操作 和 写数据操作不再是完全独立,二者有着时序上的关联,这就为初次使用者带来麻烦。因为习惯上一代控制器MIG,就很容易忽视 地址控制信号和数据控制信号的时序匹配问题。

非连续写操作时,设计者需要关注地址控制信号和数据控制信号的时序匹配问题。当写指令操作使能后,提前1个clock或者至多延迟2个clock必须给数据。

连续写操作时,由Figure1-49黄色高亮文字说明可知,设计者此时无需关注地址控制信号和数据控制信号的时序匹配问题。只需要保证写指令的有效个数(app_en控制)和写数据(app_wdf_wren)的有效个数均相同即可。此处文档说明我经过实际板级验证是可行的。

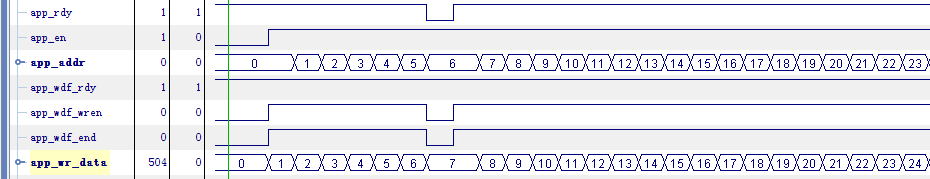

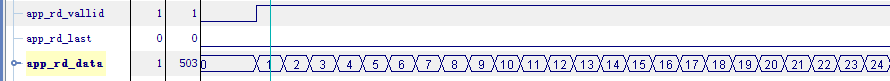

(1) 单个数据写操作 — 因为读操作很简单,故此处只讨论写操作

地址控制信号与写数据信号严格按照时序图图4要求即可,最好是都对齐。 判定写允许信号可以设定为app_rdy & app_wdf_rdy。 为简单起见,可令app_wdf_end = app_wdf_wren。且注意app_en信号有效时间为1clock,不要随意延长为2clock。如果是单个数据写操作一直写入100个数据,那么app_en信号和app_addr信号有效时间均为100clock,且需要完全对齐,且不要随意延长。我就是吃过这个亏,导致写入数据看起来是符合的。但是读数据时发现读出的数据前几个会不断变化出错。(时序还是需要严谨的)

(2) 连续写操作 — 由于写数据不用受到写指令时序的影响,可以让地址控制信号与写数据控制信号完全独立。分别用独立的计数器是控制各自的有效时间。通过实际调试发现:app_wdf_rdy有效时间 比 app_rdy有效时间更连续。举例说明如下:

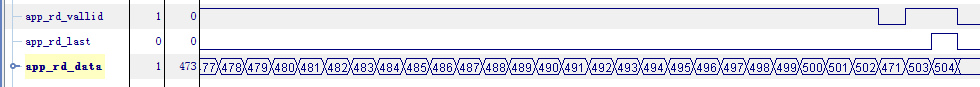

假设单次写入数据长度为128个,当写数据计数器累加到128时,可能写指令有效计数器此时为100。那么状态机可以切换到下一个状态,改状态只进行写指令操作而不进行写数据操作(因为写数据操作已完成,快于写指令操作),直到写指令计数器也累加到128,从而单次写入数据操作才算是最终完成。

说明:实际测试可知,如果一直单个数据写操作,本质上等效于连续的写操作,但是因为单个数据写操作判定写允许信号设定为app_rdy & app_wdf_rdy,要写指令ready信号和写数据ready信号同时有效才可以,故实际可能比真正的连续写操作耗时要略微多一丢丢。两种方法测试写入504个数据长度,其实差别很小。 但是前者方法更容易理解,编程更容易一些。

<li class="tool-item tool-active is-like "><a href="javascript:;"><svg class="icon" aria-hidden="true"> <use xmlns:xlink="http://www.w3.org/1999/xlink" xlink:href="#csdnc-thumbsup"></use> </svg><span class="name">点赞</span> <span class="count">2</span> </a></li> <li class="tool-item tool-active is-collection "><a href="javascript:;" data-report-click="{"mod":"popu_824"}"><svg class="icon" aria-hidden="true"> <use xmlns:xlink="http://www.w3.org/1999/xlink" xlink:href="#icon-csdnc-Collection-G"></use> </svg><span class="name">收藏</span></a></li> <li class="tool-item tool-active is-share"><a href="javascript:;" data-report-click="{"mod":"1582594662_002"}"><svg class="icon" aria-hidden="true"> <use xmlns:xlink="http://www.w3.org/1999/xlink" xlink:href="#icon-csdnc-fenxiang"></use> </svg>分享</a></li> <!--打赏开始--> <!--打赏结束--> <li class="tool-item tool-more"> <a> <svg t="1575545411852" class="icon" viewBox="0 0 1024 1024" version="1.1" xmlns="http://www.w3.org/2000/svg" p-id="5717" xmlns:xlink="http://www.w3.org/1999/xlink" width="200" height="200"><defs><style type="text/css"></style></defs><path d="M179.176 499.222m-113.245 0a113.245 113.245 0 1 0 226.49 0 113.245 113.245 0 1 0-226.49 0Z" p-id="5718"></path><path d="M509.684 499.222m-113.245 0a113.245 113.245 0 1 0 226.49 0 113.245 113.245 0 1 0-226.49 0Z" p-id="5719"></path><path d="M846.175 499.222m-113.245 0a113.245 113.245 0 1 0 226.49 0 113.245 113.245 0 1 0-226.49 0Z" p-id="5720"></path></svg> </a> <ul class="more-box"> <li class="item"><a class="article-report">文章举报</a></li> </ul> </li> </ul> </div> </div> <div class="person-messagebox"> <div class="left-message"><a href="https://blog.csdn.net/CAOXUN_FPGA"> <img src="https://profile.csdnimg.cn/C/E/4/3_caoxun_fpga" class="avatar_pic" username="CAOXUN_FPGA"> <img src="https://g.csdnimg.cn/static/user-reg-year/2x/3.png" class="user-years"> </a></div> <div class="middle-message"> <div class="title"><span class="tit"><a href="https://blog.csdn.net/CAOXUN_FPGA" data-report-click="{"mod":"popu_379"}" target="_blank">CAOXUN_FPGA</a></span> </div> <div class="text"><span>发布了29 篇原创文章</span> · <span>获赞 37</span> · <span>访问量 5万+</span></div> </div> <div class="right-message"> <a href="https://im.csdn.net/im/main.html?userName=CAOXUN_FPGA" target="_blank" class="btn btn-sm btn-red-hollow bt-button personal-letter">私信 </a> <a class="btn btn-sm bt-button personal-watch" data-report-click="{"mod":"popu_379"}">关注</a> </div> </div> </div>

3829

3829

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?