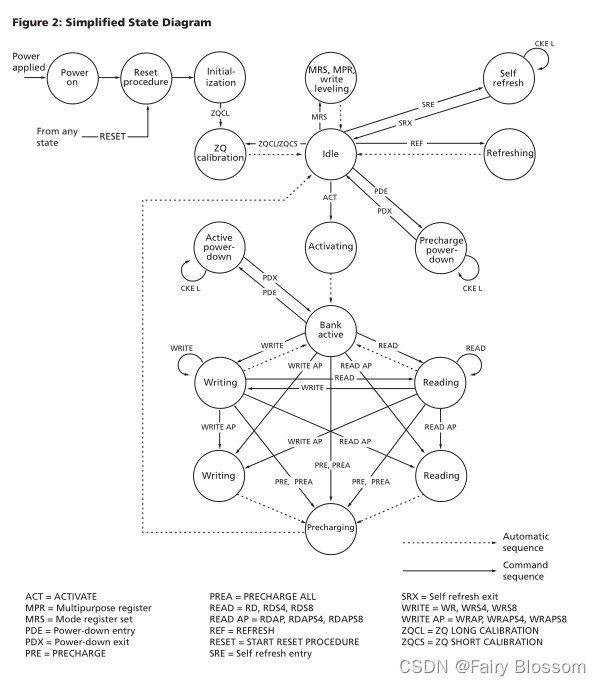

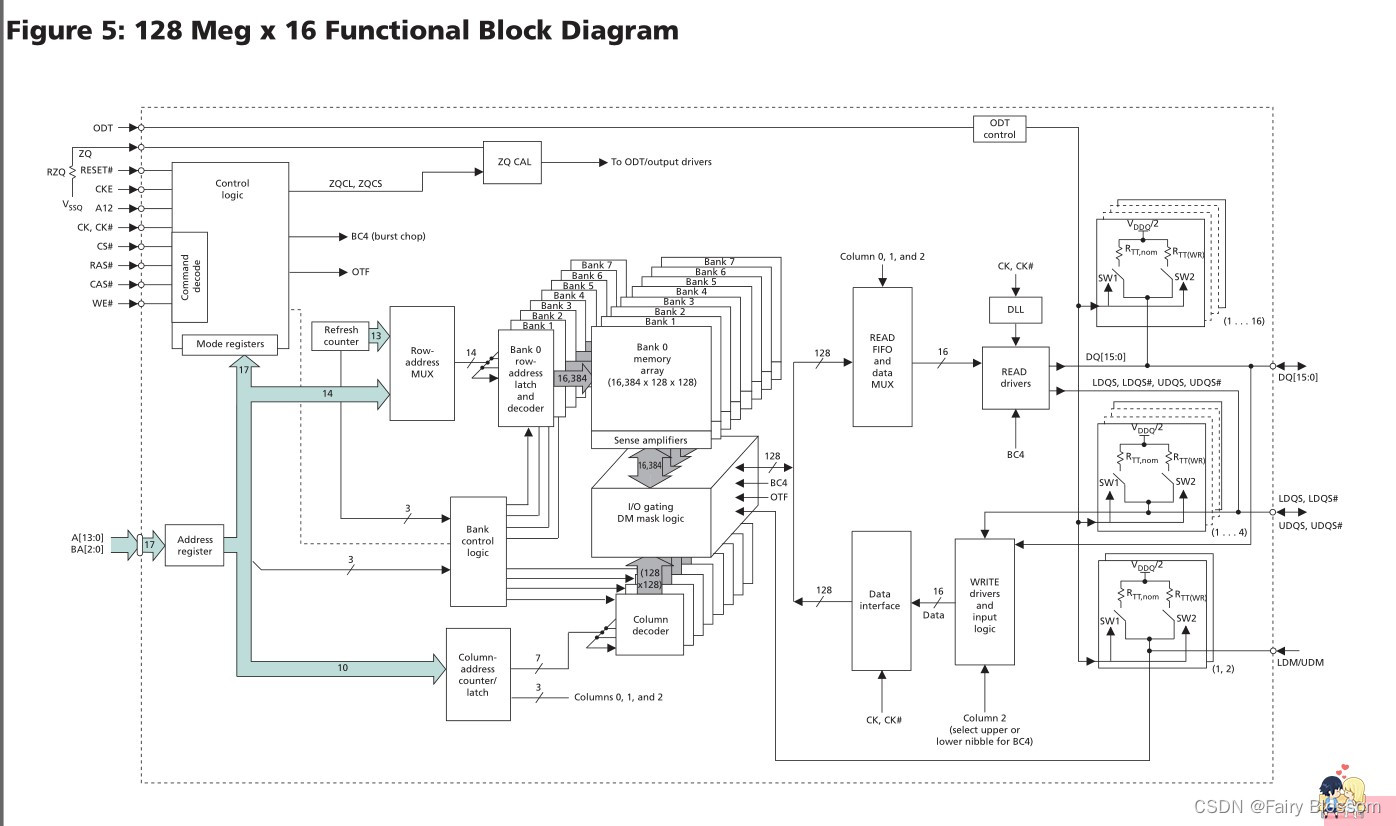

关于手册中给出的以下示意图:

- ck/ck# 在外部写数据时直接使用差分时钟,而在读数据时加了PLL

- MUX是个多路选择器,多输入单输出,上面对应的MUX的输入是128,输出是16,相差8(数据长度是16bits,突发8次)

- DM开启可对写入数据掩码

- ODI可开启内部终止电阻

- 注意input和I/O接口

COMMAND

- ZQ用于初始校准

- ACTIVATE用于启用特定bank的一行,BA[2:0]选择bank,A[n:0]提供地址

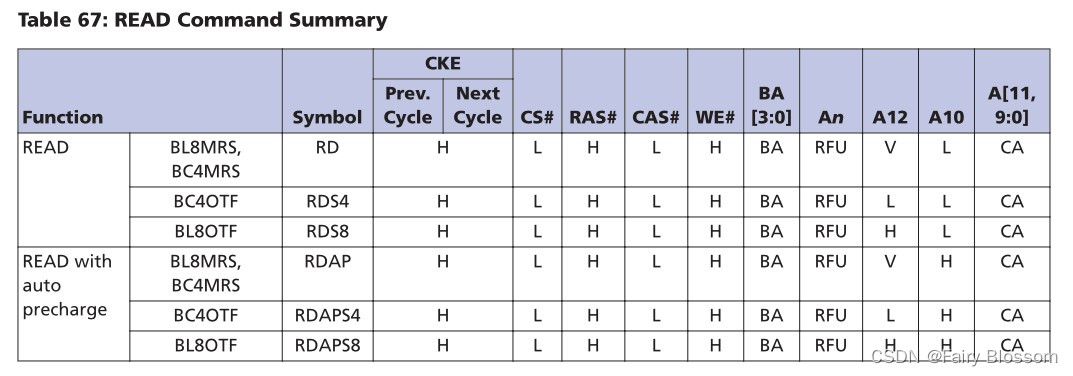

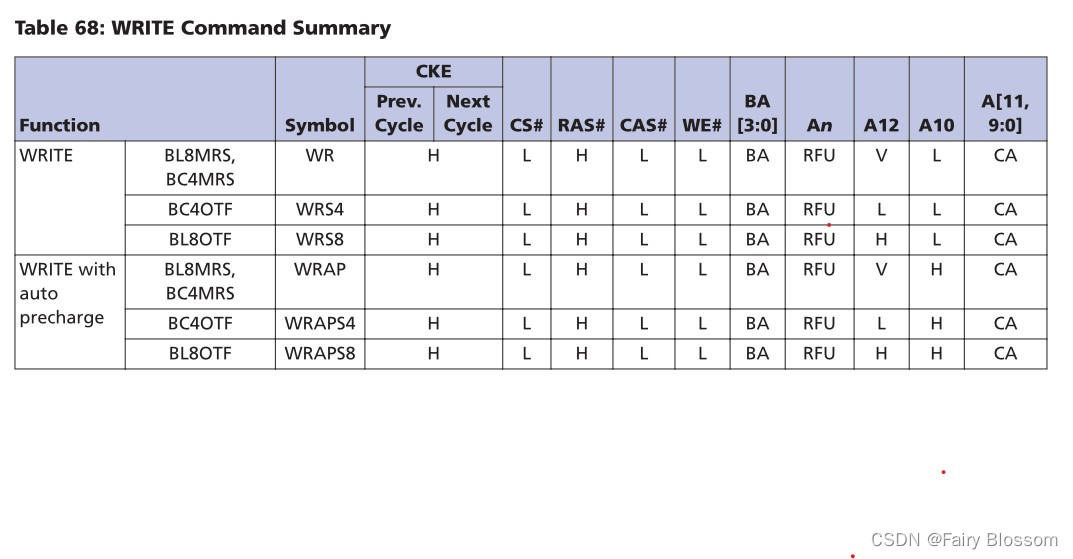

- READ WEITE 这两个命令用于发起突发访问,读是由A[2:0]确定起始地址,写是由BA[2:0]确定起始地址。根据出现在DQ上的DM输入逻辑电平,将出现在DQ上的输入数据写入存储器阵列。

- The value on input A10 determines whether auto precharge is used.

- The value on input A12 (if enabled in the mode register) when the READ command is issued determines whether BC4 (chop) or BL8 is used.

DDR配置完成以后MIG信号解释(非AXI)

app_en

MIG输入,在声明app_en之前,用户必须先对app_addr、app_cmd、app_hi_pri进行赋值,之后声明app_en将该请求提交给MIG,在MIG接收之后会发送app_rdy确认握手成功。

驱动程序收到外部的读写请求后,驱动程序将该信号发给MIG。在完成要求的突发周期后才会拉低该信号。

app_rdy

MIG输出,向用户显示当前提交给UI的请求是否被接受(握手成功?)。如果在app_en asserted之后,MIG未声明该信号,则必须重试当前的请求,在以下三种情况下,MIG不会声明app_rdy的输出:内存初始化未完成;有bank被占用(请求读取,读取缓冲区满;请求写入,并无写缓冲区指针可用)正在插入定期读取。

只有拉高时才能进行地址的增加。

app_wdf_rdy

MIG输出,表示写入数据FIFO准备好接收数据,注意接收写入数据操作要在app_wdf_rdy和app_wdf_wren都有效时进行。

这一信号要通过驱动程序输出给外部程序,告知外部程序DDR3中的FIFO缓存区已经准备好,而外部程序接收到该信号就可以给data赋值了。

app_wdf_data

MIG输入,该信号直接与驱动程序的输入wr_burst_data连接。

app_wdf_wren

MIG输入,表示app_wdf_data[]总线上的数据有效,驱动程序中该信号的赋值操作为:

assign app_wdf_wren = app_wdf_wren_r & app_wdf_rdy;是在wr_burst_data_req拉高以后。

app_wdf_end

MIG输入,该输入表示当前周期中app_wdf_data[]总线上的数据是当前请求写入到外部DDR存储器的数据。程序中使用的是app_wdf_end = app_wdf_wren;

app_rd_data_valid

MIG输出,读取的数据有效。

init_calib_complete

校准完成会拉高。

app_wdf_mask

关于DDR3的配置

- 区分几个不同的时钟:

- 第一个配置的400M的时钟是系统工作时钟(芯片运行时钟——DDR会以这个时钟采集数据,注意DDR3是双边沿采集),他与MIG IP用户时钟ui_clk之间的关系是4:1。DDR3的系统工作时钟是350M一下的时候会有2:1和4:1两种,否则一般默认4:1。4:1用于高速,2:1用于低速。

- 还有一个时钟是 input clock,这是MIG IP核系统输入时钟sys_clk_i,由PGA内部产生,一般是晶振加锁相环DDL产生输入进来。

- 关于几个数据位宽(在axi下):

- 根据型号可以看出DDR3的数据位宽;

- DDR3突发读写最多是8(可以少于8)因此输出的数据位宽最多是上面根据芯片设置好的数据位宽的8倍;

AXI协议下的DDR驱动程序解释:(以7035开发板第30个例程为例)

- 外部程序只需要提供读写请求,读写长度,读写地址,以及等待驱动程序传回来的ddr可写可读请求和读写完成信号

- 驱动程序收到外部程序的写请求后,WR_FIFO_RE是驱动程序输出给外部程序的写请求wr_burst_data_req;而rd_burst_data_req是在读地址握手拉高之后。

- 传输地址和突发长度是以字节为单位的,当数据位宽为64bit时,一次传输的数据为8字节,地址增量为8。因此接进来的地址和长度要左移3位来保证一个地址写一个字节,同时数量写够了。一次突发长度为256时,突发地址的增量为 256*8 =2048。

- 在发送数据之前首先要建立握手,首先是地址传输的握手,完成以后是数据传输的握手。写完一次数据传输周期(最大256bit)后要等待DDR3响应再次建立握手。

- 只有没有完成一次数据传输,一个周期将会传输一个数据,这个数据对应的64bits,所以DDR3会在8个地址中自动递增8次也就是突发读8次。因此这里有reg_wr_adrs[31:0] <= reg_wr_adrs[31:0] + 32'd2048。

- 文章FPGA大赛中对信号的解释:FPGA大赛【六】具体模块设计--DDR的数传输

- 关于各个信号的含义可以看文章:ZYNQ AXI4(AXI-full)总线学习(一)三种AXI总线以及AXI-full总线端口总结

2717

2717

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?