这两天对网表生成这一部分的工作做了不少,记录一下过程中的问题与解决方案

dcp网表生成:

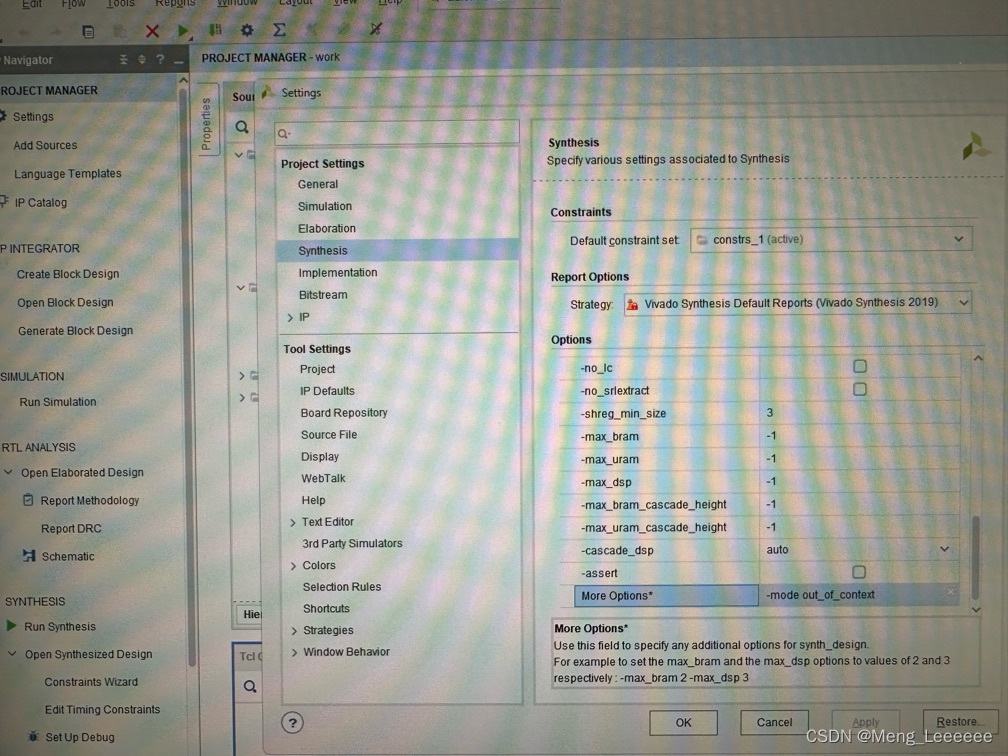

- 如下图,将setting,synthesis,options,more options*填写为-mode_out_of_context (ug901-p27(2019)有解释)

- 设置需要压缩的文件为顶层,并debug file 掉xdc文件,然后进行综合

- 综合好打开综合设计(open synthesized design) 再在tcl栏输入write_checkpoint D:/**/**/***.dcp(**为自己所需路径,***为顶层名称)

- 对刚刚生成的dcp进行调用,调用方式为替换并删除原本的顶层文件,vio,ip。 主要的点在于原本的例化里可能有parameter类型的值,全替换成实际常数。

- 注意事项:在实际操作时必须打开综合设计之后再写tcl命令才成功生成了dcp文件,直接写可能会报错error: common 17-35 user exception: no open design.please open an elaborated,synthesized or implemented design before executing this command;必须将例化的所有信号都有实际输入值或连接到另一处工作的模块接口上,否则会报严重警告,显示为synth 8-4442 blackbox module****has unconnected pin **

- edf网表生成

- 同dcp1

- 同dcp2

- 打开综合设计,tcl命令框中输入:write_edif -force -security_mode all D:/**/**/***.edf(**为自己所需路径,***为顶层名称)wirte_verilog -mode synth_stub D:/**/**/***.v(**为自己所需路径,***为顶层名称) 以上命令直接加了输出路径,这里如果不输出对应的.v而只将.edf文件移植替换到工程(新工程)编译会报错,tcl命令参考ug835。

3261

3261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?