配置msp432e401y的ADC采样达到2M

配置msp432e401y的ADC采样达到2M

电赛期间收到了TI公司提供的msp432e401y开发板。手册上标明ADC采样率可以达到2M,但在TIDriver里好像最大开到500k的采样率。在网上找了半天,没有找到相关代码的帖子,索性自己研究手册,配置出2M采样率。

例程代码

在msp432e4的sdk文件中里找到.\examples\nortos\MSP_EXP432E401Y\demos\cmsis_msp432e4_dsp_example工程文件。

例程使用driverlib库,开启ADC与DMA传输,使用定时器作为ADC的trigger,结合ARM的DSP库,实现DMA乒乓模式采集ADC数据&FFT操作。

通过修改cmsis_msp432e4_dsp_example.c中的

//cmsis_msp432e4_dsp_example.c

#define NUM_SAMPLES 1024

#define SAMP_FREQ 100000

来修改采样点数与采样速率。直接修改此代码的参数,可使ADC最大速率达到1M,SAMP_FREQ大于此速率时ADC采样率也为1M。

ADC采样率提高到2M

ADC采样率

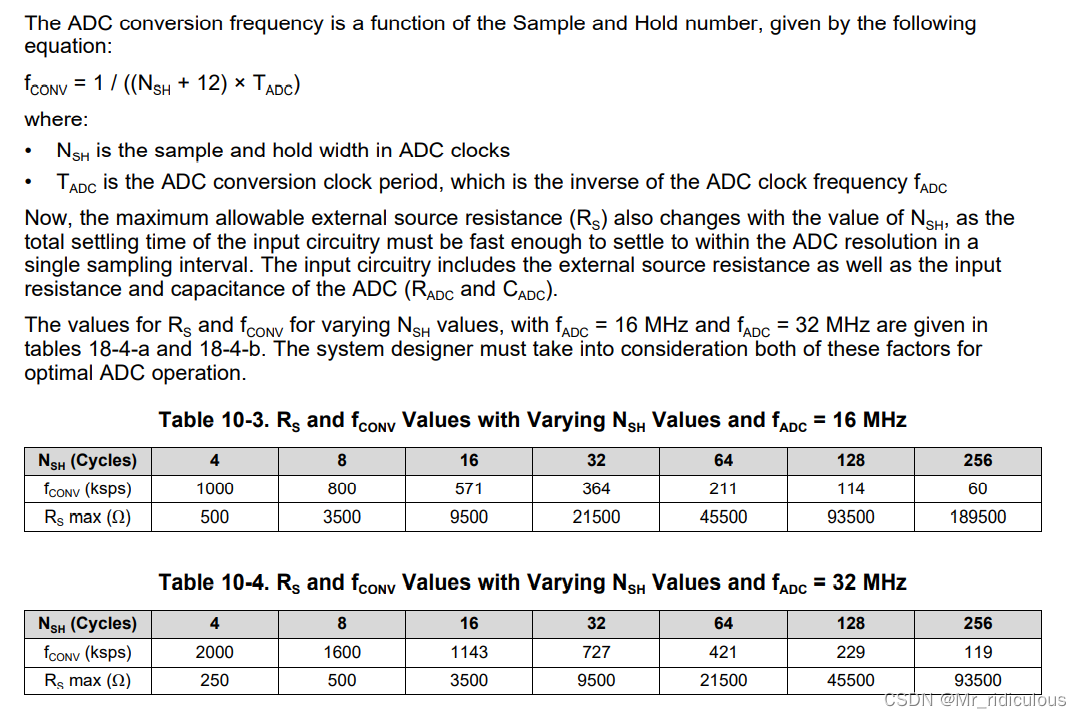

在官方参考手册《MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual》中

P707:

指出了采样速率与ADC时钟、采样保持时间的关系。可以看到,在fADC=16MHz时,ADC最大采样率fCONV=1Msps(NSH默认为4),想要达到fCONV=2Msps,须使fADC=32MHz。

ADC时钟

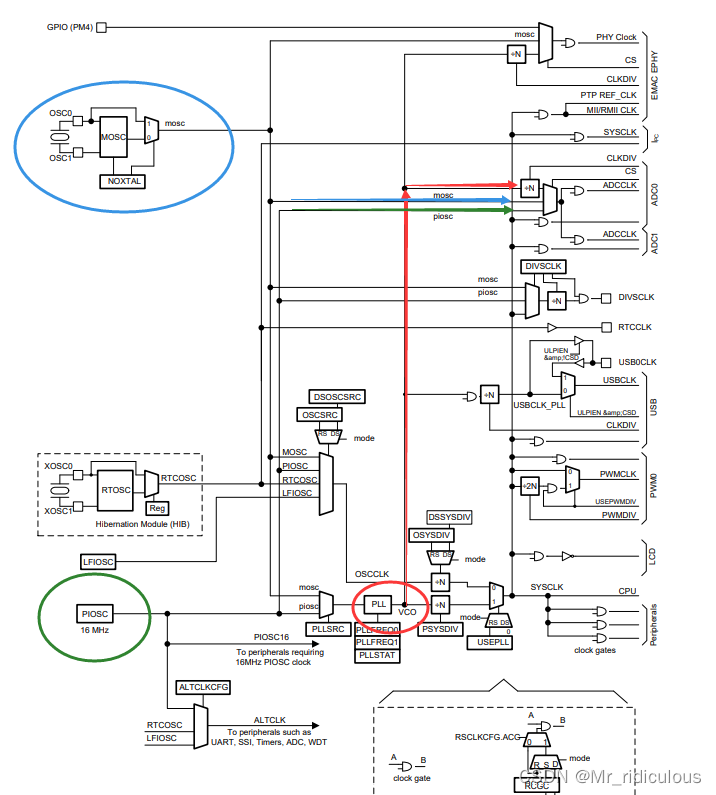

在官方参考手册《MSP432E4 SimpleLink™ Microcontrollers Technical Reference Manual》中

P205

给出了ADC的三个时钟源(也可见P206-4.1.5.2.1.1)。

其中

- MOSC为主晶振,连接到外部晶振,MSP432E401Y开发板上面的外部高速晶振Y3频率为25MHz。

- PIOSC为内部精密时钟,频率为16MHz。此时钟为默认ADC时钟。

- PLL VCO为锁相环输出频率,可设置为480MHz或320MHz(见P209-4.1.5.5.1)。此时钟满足我们的要求。

修改代码

在例程中,PLL被设置到了480MHz,我们需要将其15分频给ADC,由此产生36MHz的ADC时钟。但是尝试之后仍还是1Msps采样率。经过试验,发现由于某些原因,由PLL到ADC经过分频之后会再2分频。我没有在手册中找到说明,可能需要再研究一下手册。

知道此信息之后,我们需要给ADC提供一个64MHz的频率,480MHz不方便通过整数分频得到64MHz,但是可以通过320MHz的时钟进行5分频得到。

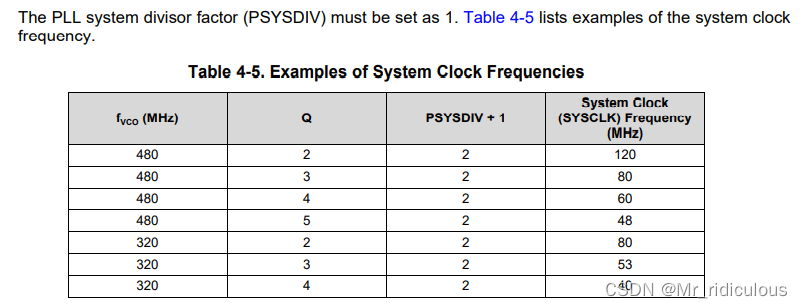

我们参考P209

首先将fVCO=480MHz,fSYSCLK=120MHz

修改为fVCO=320MHz,fSYSCLK=80MHz

代码修改如下↓:

//cmsis_msp432e4_dsp_example.c

/* Configure the system clock for 120 MHz */

//systemClock = MAP_SysCtlClockFreqSet((SYSCTL_XTAL_25MHZ |

// SYSCTL_OSC_MAIN |

// SYSCTL_USE_PLL |

// SYSCTL_CFG_VCO_480), 120000000);

/* Configure the system clock for 80 MHz */

systemClock = MAP_SysCtlClockFreqSet((SYSCTL_XTAL_25MHZ |

SYSCTL_OSC_MAIN |

SYSCTL_USE_PLL |

SYSCTL_CFG_VCO_320), 80000000);

同时,配置ADC的时钟,使用PLL时钟,进行5分频

在例程语句↓:

//cmsis_msp432e4_dsp_example.c

/* Enable the clock to ADC-0 and wait for it to be ready */

MAP_SysCtlPeripheralEnable(SYSCTL_PERIPH_ADC0);

while(!(MAP_SysCtlPeripheralReady(SYSCTL_PERIPH_ADC0)))

{

}

之后加上语句↓:

//cmsis_msp432e4_dsp_example.c

ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADC_CLOCK_RATE_FULL, 5);

最后修改采样触发速率参数↓:

//cmsis_msp432e4_dsp_example.c

#define NUM_SAMPLES 1024

#define SAMP_FREQ 2000001

此处SAMP_FREQ为2000001而不是2000000,是因为测试发现2000000时采样率只能达到1.8Msps,而2000001就正好为2Msps了(1999999为1.8Msps,1900000为1.85Msps左右),很奇怪。

此外,可以选择fVCO=480MHz,再进行7分频得到约68.5MHz的ADC时钟,再修改相关参数可以达到更大的采样速率,而且不会降低主频(上述代码将主频从120M降低到80M),测试了一下发现ADC在2.5Msps速率下也是可以运行的,但是不知道长时间使用会对ADC造成什么影响。

结果

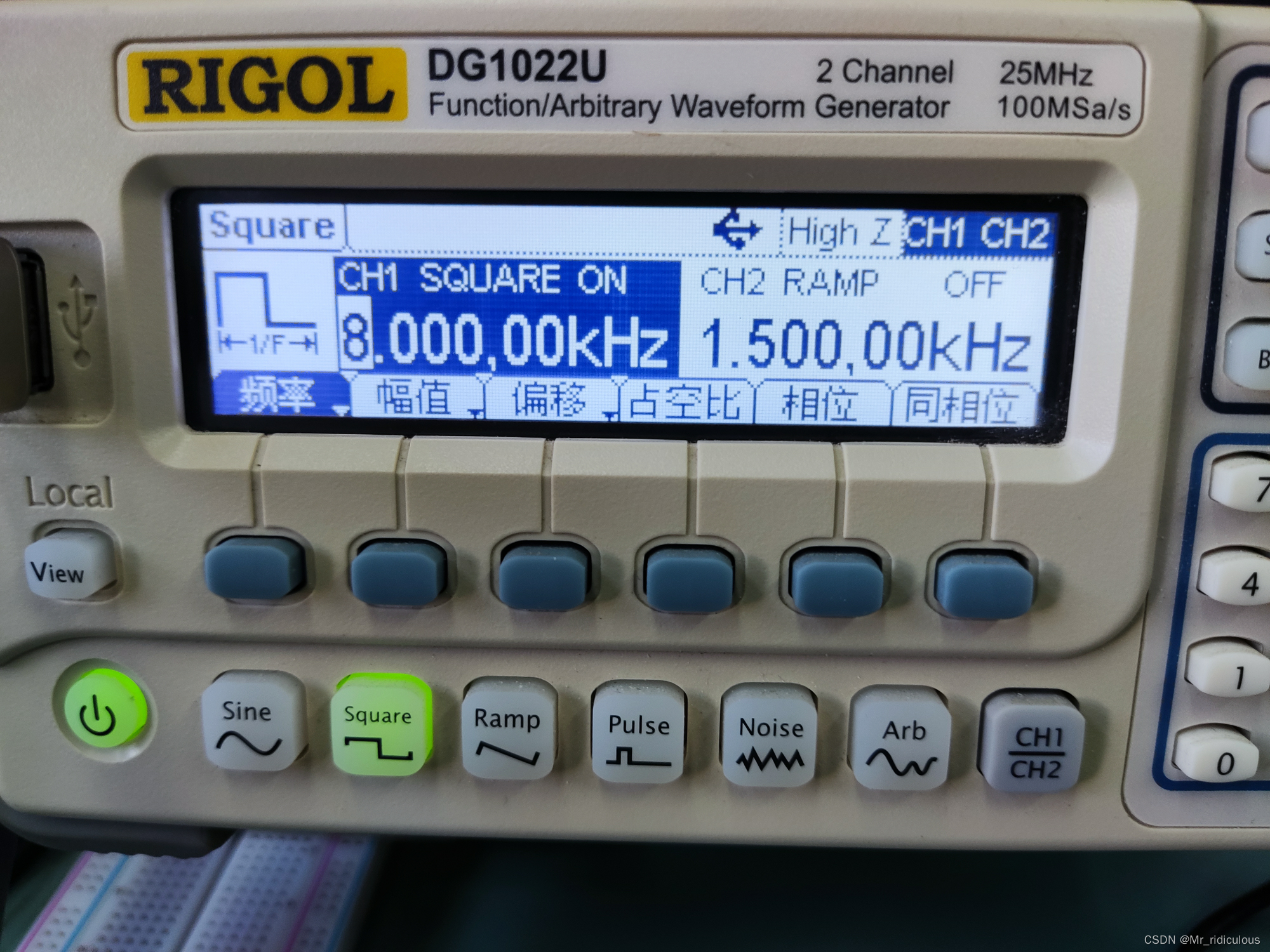

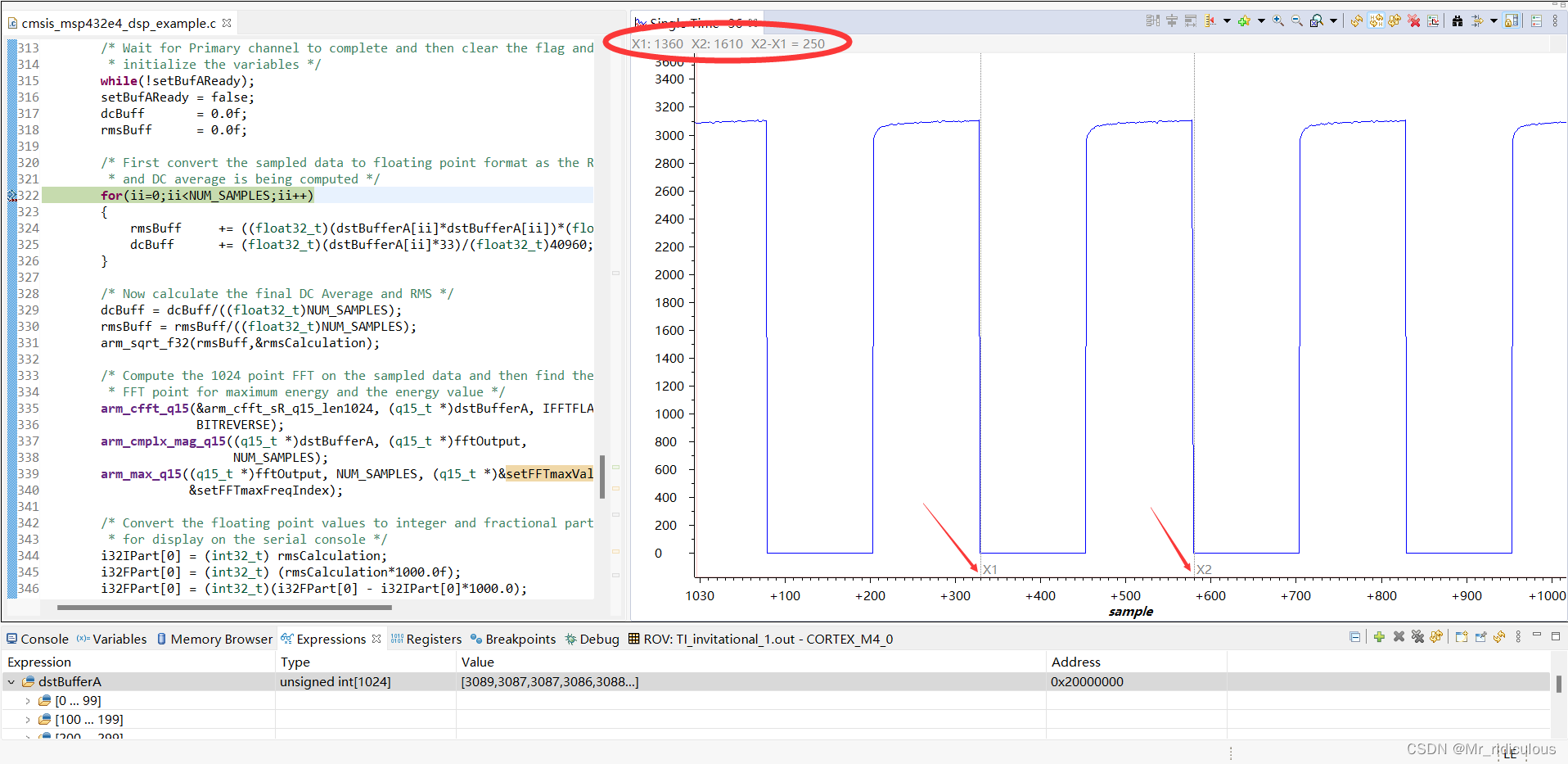

测试信号使用8kHz的方波:

在CCS中设置断点查看采集的数据

在CCS中设置断点查看采集的数据

可以看到方波一个周期采集了250个点,采样率为250*8k=2Msps。

可以看到方波一个周期采集了250个点,采样率为250*8k=2Msps。

END

上文为配置msp432e401y的ADC采样达到2M的方法,目前对这个板子的了解还不深,文中有什么错误请指出。也有一些疑惑比如为什么PLL到ADC会再2分频,SAMP_FREQ为2000000与2000001为什么会相差较大,有没有大神可以指点一下。

本文详细介绍了如何通过配置TI MSP432E401Y的ADC,利用定时器和ARM DSP库实现2M采样率,涉及系统时钟设置、PLL分频及代码修改,包括解决ADC时钟分频谜团和采样频率精确调整的技巧。

本文详细介绍了如何通过配置TI MSP432E401Y的ADC,利用定时器和ARM DSP库实现2M采样率,涉及系统时钟设置、PLL分频及代码修改,包括解决ADC时钟分频谜团和采样频率精确调整的技巧。

1258

1258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?