主要总结一下逻辑器件作为热插拔单板的接口保护器件的功能。

一、背景

在带电插入时,单板的电源、地以及输入、输出端口几乎同时与背板上的电源、地及信号线接触,由于单板上的电源有较大的容性,上电缓慢,这使得存在输入/输出端口到电源平面或地平面的电流,构成倒灌,从而损伤接口器件。带电拔出时同样也可能发生。

为了实现热插拔,接口器件需要满足一定要求。由此逻辑器件可以分为以下四个等级。

1、级别0:完全不支持带电插拔,在插拔前必须关闭主电源。绝大多数常见逻辑器件属于这个类别。例如:AC\ACT\AHC\ALS\HSTL\LS\SSTL\TTL等。

2、级别1:逻辑器件支持局部掉电(Partial-Power-Down)。支持在器件掉电时,关断接口到电源的通路,避免接口信号的电流倒灌到电源引脚。但在插拔前,主系统必须暂停接口信号传输。要求接口支持I_off 特性。例如:AVC/LV/LVC等。

3、级别2:支持热插拔(Hot Insertion)。除了级别1的功能,还能防止插拔时可能产生的总线冲突。要求接口支持I_off、PU3S特性。例如:ABT\ALVT\LVT。

4、级别3:支持在线插拔(Live Insertion)。除了级别2的功能,还能保证单板插拔时接口总线的数据不受影响。要求接口支持I_off、PU3S、BIAS Vcc特性。

后文对I_off、PU3S、BIAS Vcc特性进行详细介绍。

二、I_off

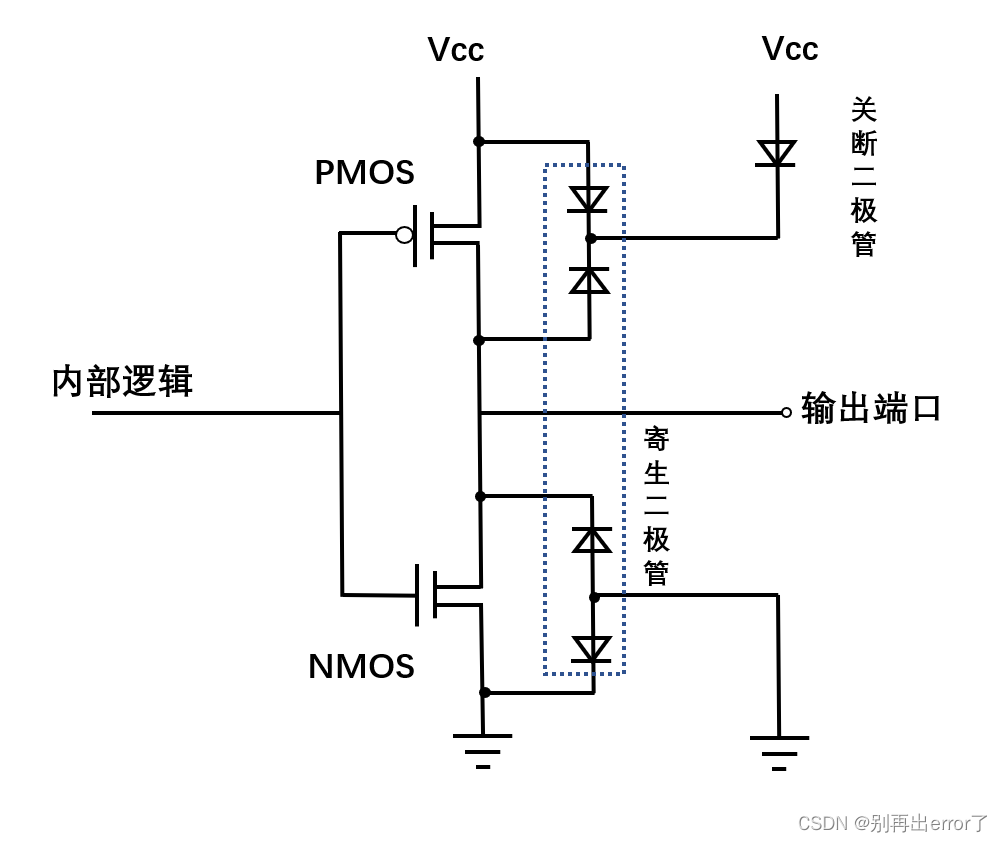

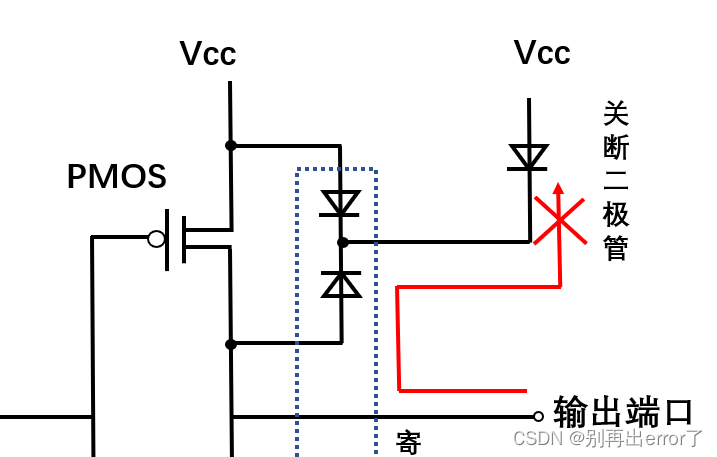

如图所示为支持I_off的CMOS器件输出端口结构图。I_off结构在输出端增加了一个关断二极管。

作用机理:逻辑器件下电时,Vcc电平变为0,但输入输出端口仍与其他处于工作状态的器件相接,端口上存在一定的电流,如器件端口不包含关断二极管,该端口的电流将通过PMOS管的寄生二极管流入Vcc引脚。关断二极管正是来阻断该通路的。

同理,在I_off结构中,是否需要加一个二极管在NMOS和GND之间呢?这是不需要的,因为NMOS管已经起到了关断二极管的作用。

三、PU3S

在连在同一总线不同单板之间,可能由于其中一个Vcc上电缓慢可能导致在两个单板之间形成Vcc到另一单板GND 的通路,从而带来损坏。

而针对这种问题,解决方法就是在Vcc上电完成前,输出端口保持高阻而不对输入信号做出响应,称为上电三态。

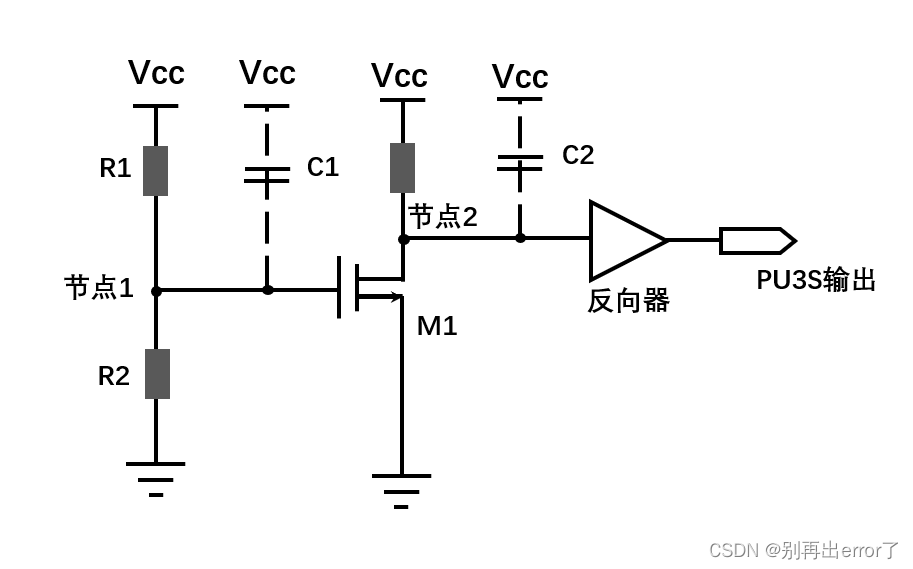

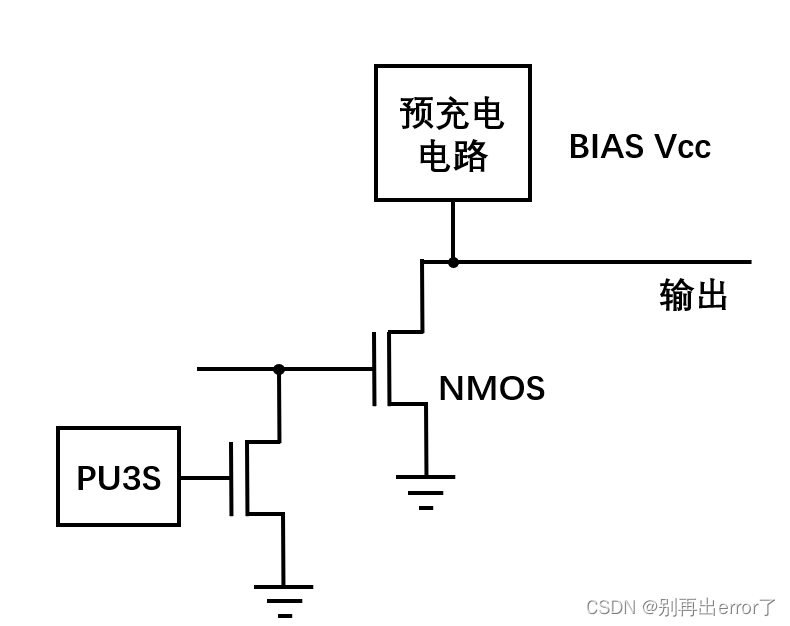

支持PU3S的逻辑器件结构如图所示:

工作原理:R1、R2构成分压电路,使M1管只有在Vcc的电平超过阈值后才导通,因此在Vcc上电过程中,节点2保持为高电平,驱动PU3S输出低电平;而在上电完成后,M1导通,节点2变为低电平,驱动PU3S输出高电平,器件的输出端开始正常工作。

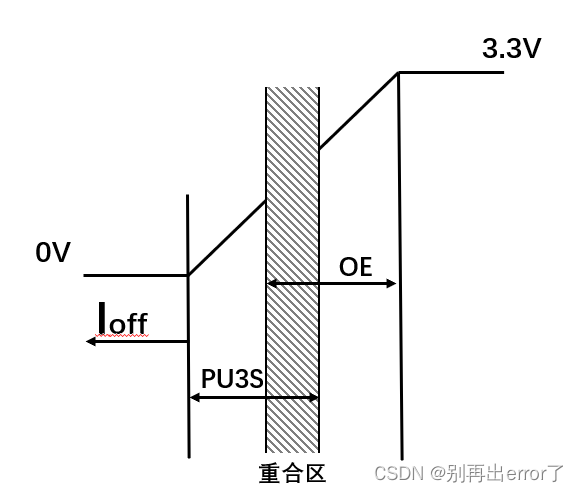

根据Vcc上电的步骤,可将控制过程分为三个阶段,即I_off阶段、PU3S阶段、OE#控制阶段。

阶段1,Vcc=0V时,Ioff结构利用关断二极管阻断输出端口与Vcc之间的通道。

阶段2,Vcc上电过程中,PU3S结构使输出端口呈现高阻态。

阶段3,Vcc上升到阈值后,PU3S释放对输出端口的控制权,交由OE控制。

重合区的目的是确保接口器件对输出信号的完全控制,在控制中,建议将OE信号弱上拉到Vcc。

注意:由于电容C1、C2的存在,当Vcc上电过快时,PU3S结构不能正常工作。因此该结构对上电速率有一定要求,由参数确定。对存在上电过快的电源,可以适当增加电容或使用缓启动电路。

PU3S相关的4个参数:

I_OZPU/I_OZPD:分别表示在上电/下电过程中,输出引脚上流入或流出电流的最大值。

I_OZH/I_OZL:分别表示当Vcc到达阈值电平后,由于输出使能信号无效,导致端口输出高阻态,此时,输出端口上流入或流出的最大值。

三、BIAS Vcc

上述两个结构实现了对接口器件的硬件保护,BIAS Vcc结构可保护接口总线上的正在传输的数据。利用BIAS Vcc可预充电待插入单板的输入/输出接口,避免对正处于工作状态的总线构成干扰。

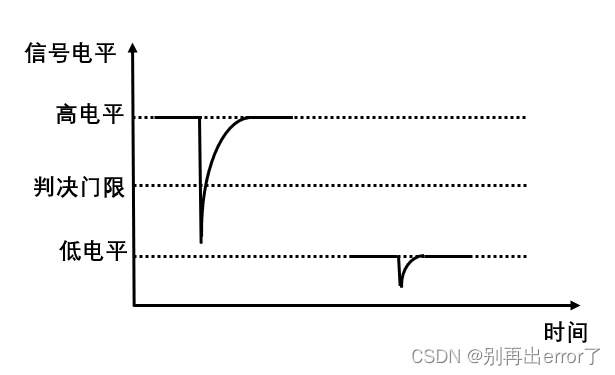

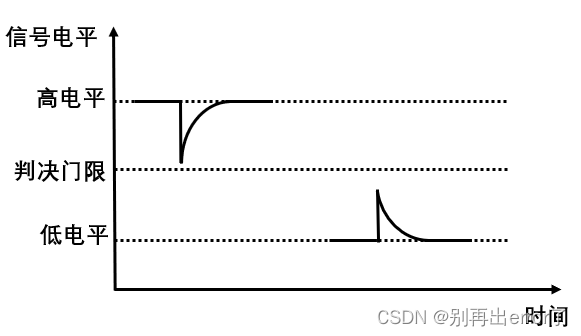

如图是接口信号分别处于高/低电平时,单板插入可能造成的影响,在高电平时有可能将信号拉至判决门限以下。

而BIAS Vcc结构如图,增加一个预充电电路,由BIAS Vcc供电(BIAS Vcc电平一般与Vcc相同,但早于接口器件Vcc引脚上电),在信号引脚与背板连接器接触之前预充电到某一电平。例如,可以选择为判决门限电平。当信号引脚与背板连接器接触时,由于引脚容性,接口信号仍会被拉向判决门限电平。但不会跨越门限,从而避免了判断错误。

BIAS Vcc相关的参数有

BIAS Vcc:预充电电路的电源,应先于Vcc上电。

Icc(BIAS Vcc) :预充电电路的电流,一般很小。

DONE!

本文介绍了逻辑器件在热插拔单板接口保护中的关键功能,包括I_off、PU3S和BIASVcc特性,以及它们如何防止电流倒灌、总线冲突和数据干扰。详细解析了相关结构的工作原理及其参数设置。

本文介绍了逻辑器件在热插拔单板接口保护中的关键功能,包括I_off、PU3S和BIASVcc特性,以及它们如何防止电流倒灌、总线冲突和数据干扰。详细解析了相关结构的工作原理及其参数设置。

1809

1809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?