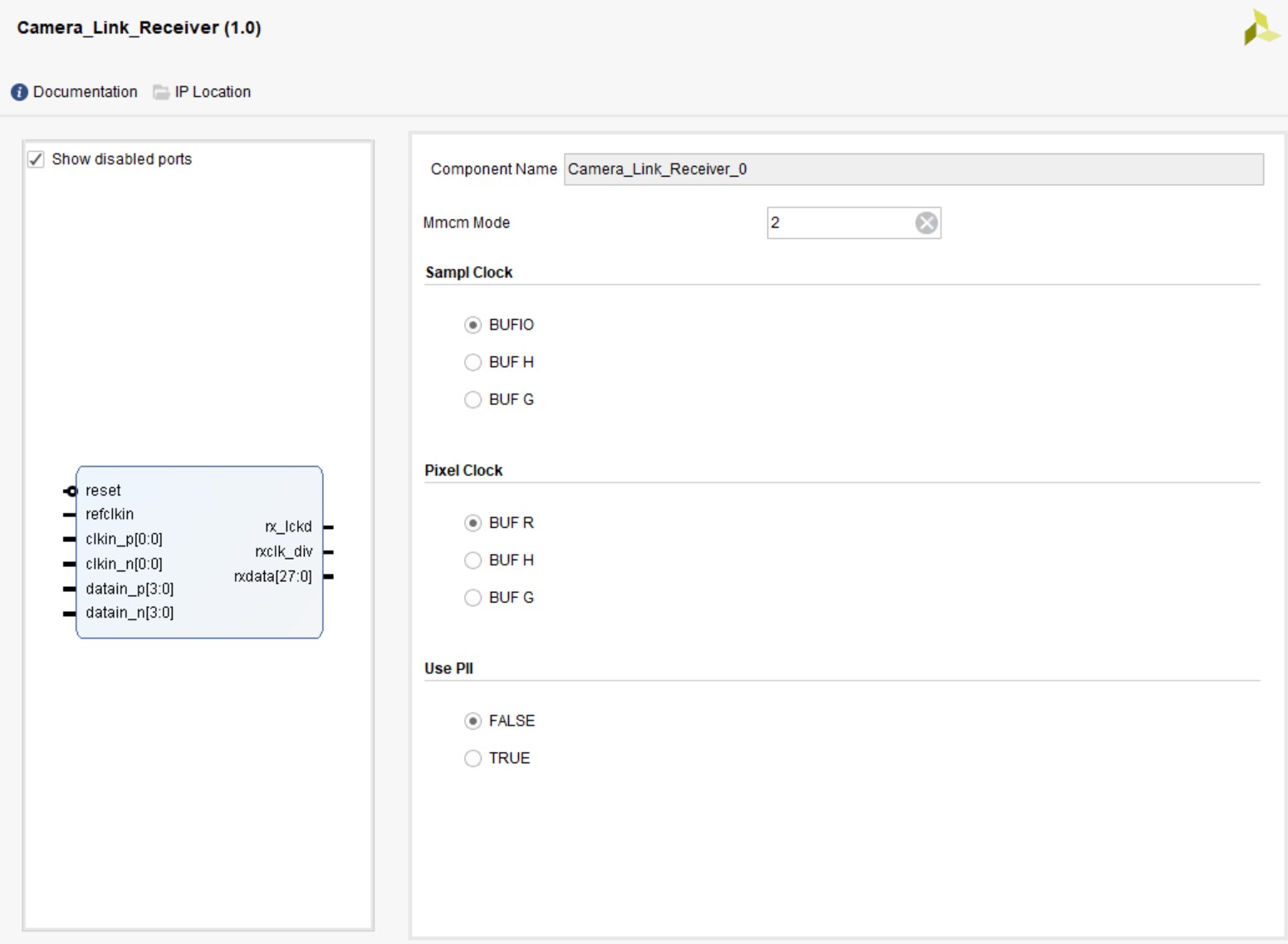

xilinx vivado cameralink图像接收与发送代码,最大支持并行速度100MHz,优于编解码接口芯片。

不利用解码与编码芯片,直接在FPGA内部进行接收解码和发送。

YID:76199649532614127

初见

在现代数字图像处理领域,高速且高效的图像传输是至关重要的。为了满足这一需求,Xilinx Vivado Cameralink图像接收与发送代码应运而生。该代码支持最大并行速度达到100MHz,并且相比于传统的编解码接口芯片,具备更出色的性能。

传统的图像传输方案通常需要依赖解码与编码芯片,这样会引入额外的复杂性和延迟。而利用Xilinx Vivado Cameralink代码,我们可以直接在FPGA内部进行图像接收解码和发送,以提升整体系统的性能和效率。

首先,使用Xilinx Vivado Cameralink代码可以实现高速的图像接收。传输速度是衡量图像传输性能的重要指标之一,而该代码支持最大并行速度达到100MHz,大大超过了许多传统方案。通过并行传输的方式,可以快速、稳定地接收图像数据,满足高速图像处理的需求。

其次,借助Xilinx Vivado Cameralink代码,我们可以在FPGA内部进行图像解码。传统的解码芯片通常需要额外的外部硬件支持,且可能引入较高的延迟。而利用FPGA内部的逻辑资源,我们可以在接收到图像数据后快速进行解码处理,避免了对外部解码芯片的依赖,降低了系统复杂性和延迟。

最后,Xilinx Vivado Cameralink代码还支持图像数据的发送。通过在FPGA内部实现图像数据的发送,我们可以直接将处理后的图像数据传输到接收端,避免了额外的编码芯片使用。这样一来,不仅提高了图像传输速度,还降低了系统的成本和复杂性。

综上所述,Xilinx Vivado Cameralink图像接收与发送代码在高速图像传输领域具有显著的优势。其支持的最大并行速度达到100MHz,超过了许多传统方案。通过在FPGA内部进行接收解码和发送,避免了对解码与编码芯片的依赖,提高了整体系统的性能和效率。这一创新性的解决方案在数字图像处理领域具有广阔的应用前景。期待未来能够看到更多基于Xilinx Vivado Cameralink代码的创新性应用,推动数字图像处理技术的进一步发展。

相关的代码,程序地址如下:http://coupd.cn/649532614127.html

1561

1561

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?