#致知穷理,学古探微;立德立言,无问西东。

最近做Robei 的东西,进展一点都不好,sobel边缘检测导出来的显示图像简直要我命,临近期末,又有特别多的课程报告要写,身心俱疲。每每想放弃比赛,却又不甘心止步于此,所以,继续加油!

这篇博客的内容,刚好是别人来问我的问题,灵机一动觉得是一个好的博客素材,就拿出来写一写。(现在写博客简直是我坚持比赛的唯一动力)

——————————————————正文的分割线————————————————————

Robei EDA 有一个问题,就是所有的代码,都是直接开源的,这样固然显示清晰,但是也出现了一个问题,没法调用IP核,也许一般的数字IP可以利用Verilog来描述,但是PLL就不一样了。由于PLL的特殊性,没法直接用Verilog来描述,那么如何让代码在实际烧录的时候带有IP,却又不影响Robei 综合出的代码原有的结构。

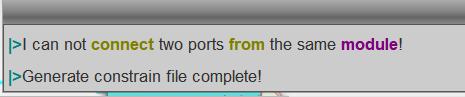

我的思路是这样的,在Robei EDA里生成一个假的PLL模块,为它封装好IO,但是保留代码编写部分,然后先把它作为一个正常的IO来给整个代码进行层次的连线,最后生成Verilog代码和管脚约束文件。之后再在Vivado 或者 Quartus 上,为导入的Project 配置PLL IP核。配好IP之后,在之前robei里创建的假的时钟模块上,例化一下。这样,一个尴尬又不失礼貌的IP就配置好了。

具体操作如下:

此处以Quartus为例(为什么不用Xilinx,因为在宿舍写博客,笔记本上的Vivado 编译太慢了)

Robei 操作

- 创建一个模块,给模块命名并配上管脚。注意,此处的管脚一定要按照PLL配置出来有几个口,一一对应上。一般是一个clock时钟信号,一个 rst_n 复位信号,一个locked信号,剩下的就是输出倍频/移相后的信号。此处输出时钟有俩。

- 将模块连接上管脚,导出Robei。

此处只单独调用 PLL IP 不作为给别的模块的时钟信号。

Quartus 部分

- 新建Project,同时导入Verilog代码和qsf管脚约束文件

- 新建IP核,并将IP核例化进之前设置的模块中。

- 编译成功,下载代码

————————————————————结束的分割线——————————————

这个内容是略微短小了一些,但是本身这个内容也非常简单,就是告诉一下如何规避一下robei里无法直接配置IP核的问题。利用空模块去代替IP,可以保证在Robei EDA 里可以完整实现一个工程的架构,导入Vivado之后只需要补一下小缺口就可以了。

至于如何仿真,仿真的时候可以不用空模块,直接通过仿真的代码给时钟信号即可。

2079

2079

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?