#沐朝露兮以自华,觅大道兮以求成

我又滚过来了,研究了20多天RISCV,结果最后因为硬件问题导致无法在比赛中使用RISCV CPU,虽然已经临近比赛后期了,非常的崩溃,但是也没有什么办法。唉,一切不过是从头再来罢了。(写写博客舒缓我心中苦闷)

————————————————进入正文的分割线————————————————

今天介绍一下如何利用 Robei EDA 生成文件,导入vivado中,综合下载到开发板里。拿我一个PWM控制舵机的代码为例。

Robei EDA设置

假设代码模块(model文件)经过仿真验证,已经封装好了。

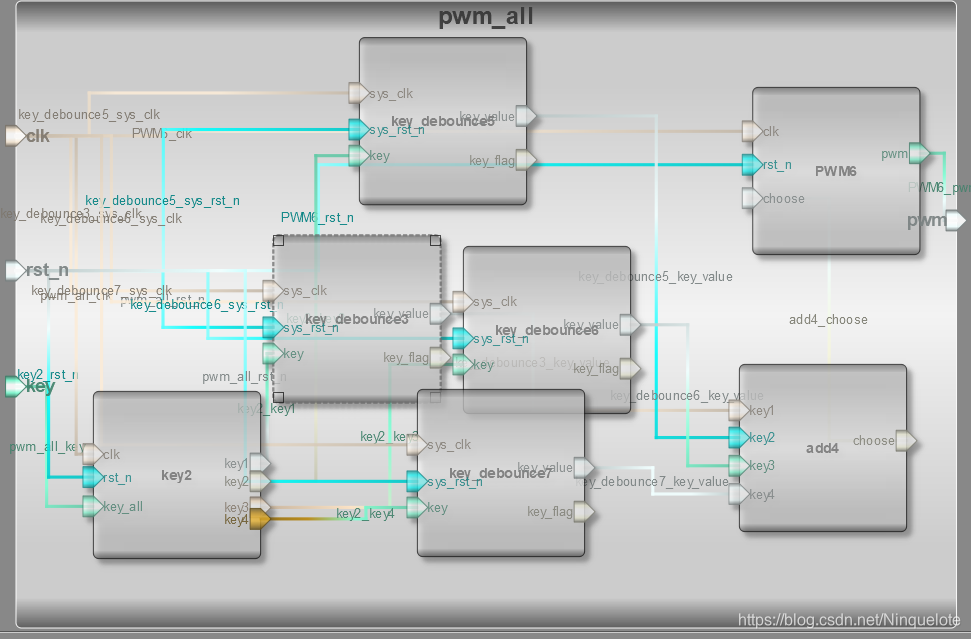

如图

把所有的模块封装好了,那么,就到了生成管脚约束文件(xdc文件)的时候了。

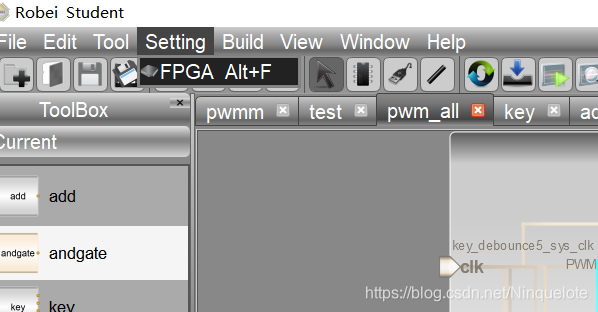

在菜单栏,选择Setting—FPGA,这个选项是针对FPGA的品牌,生成对应文件的设置。

目前只支持Xilinx 和 Altera 这两家公司,希望 Robe i能够尽快把适配国产FPGA开发环境提上日程。比如上海安路的TD,还有广东高云的

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4405

4405

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?