#天下凡人皆庸于懒,天下才子皆毁于傲。

Altera (现在已经被Intel收购了,新一代的FPGA都被冠上Intel的名字了) FPGA,所用的开发环境是Quartus II,目前是出到19.1好像,我电脑上的是17.1。

Quartus II的版本支持的芯片是有限制的,像Cyclone II类型的芯片,超过13.0之后就不支持了,而像最新的Cyclone 10还有Intel下面的一些 SoC FPGA也不支持,这种就要尽可能选择高一点的版本,比如15.0,17.1,18.0这样的。

这里就拿一个流水灯的Demo来介绍一下怎么样入门Quartus 的环境。

创建工程

一、 工程文件的创立

-

选择一个文件夹(全英文路径,只能包含英文和下划线。不能含有任何中文和非法字符,否则工程文件就不能正常打开)

新建文件夹,也是要命名为英文。

-

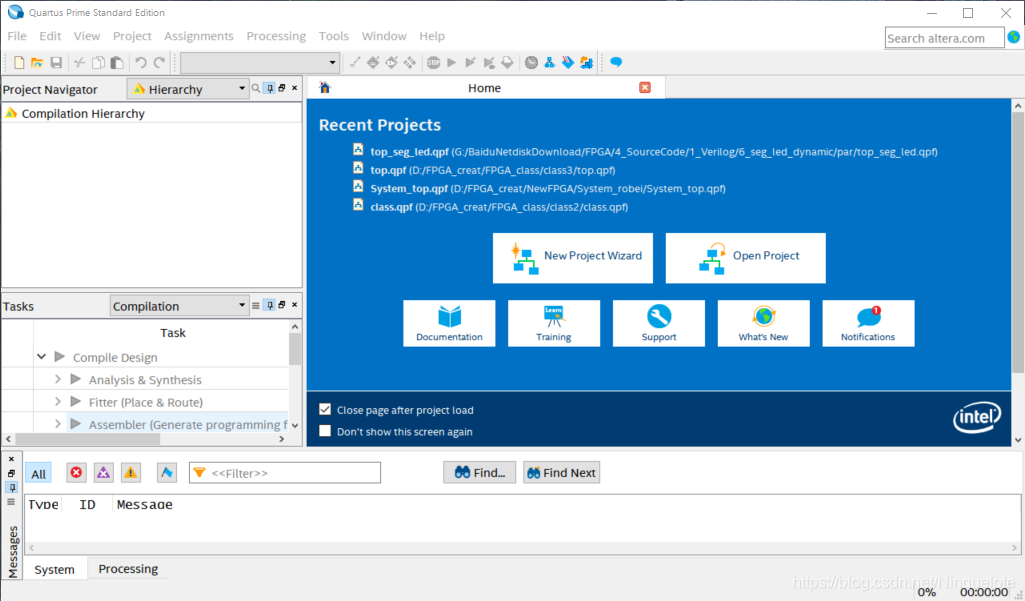

打开Quartus II软件

-

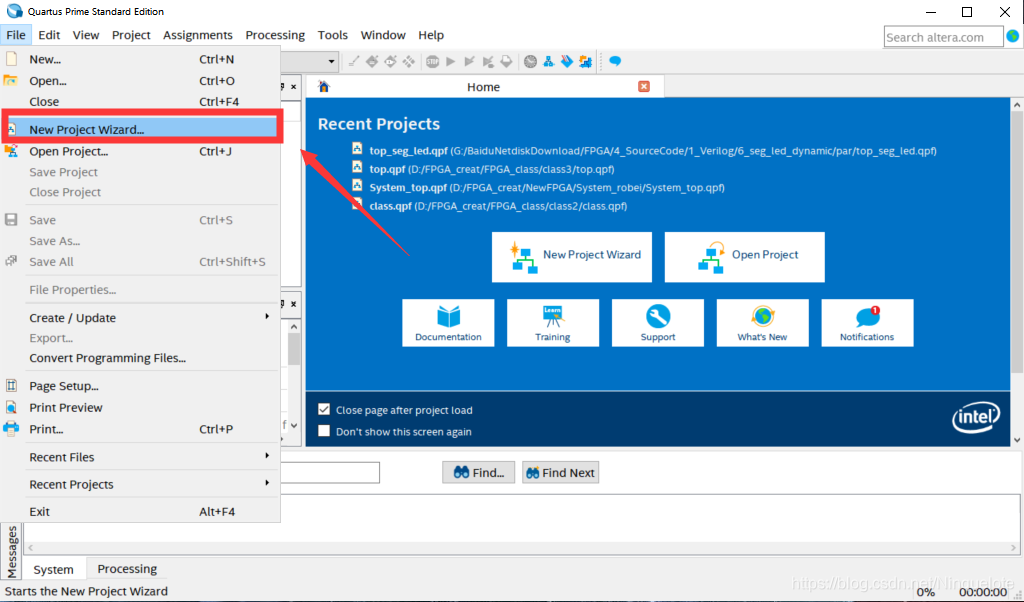

选择File-- New Project Wizard

-

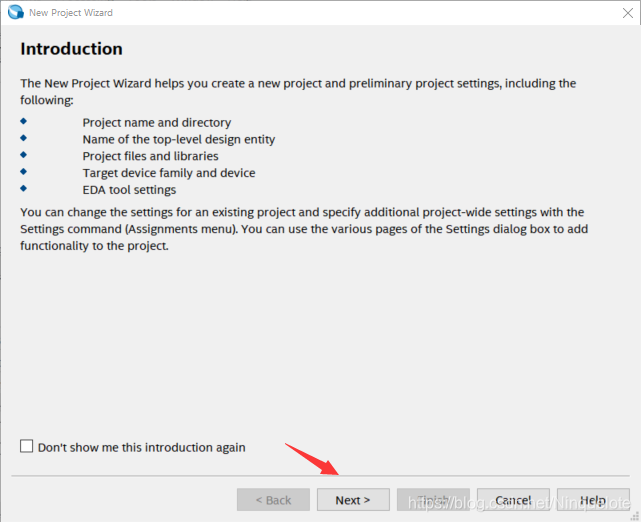

Next

-

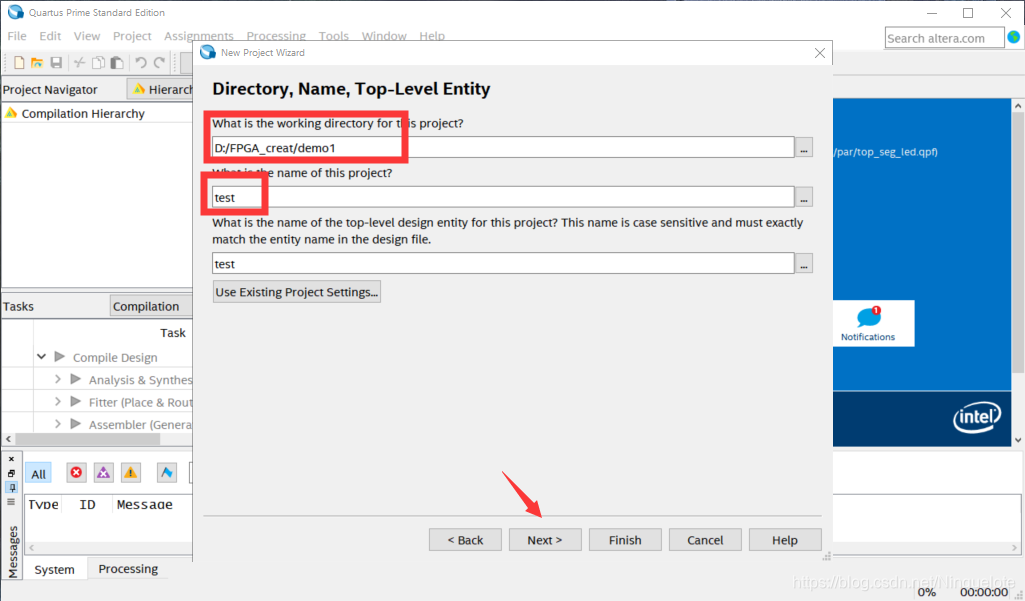

选择之前自己新建的文件夹,并为自己的工程命名,然后点击“Next”

-

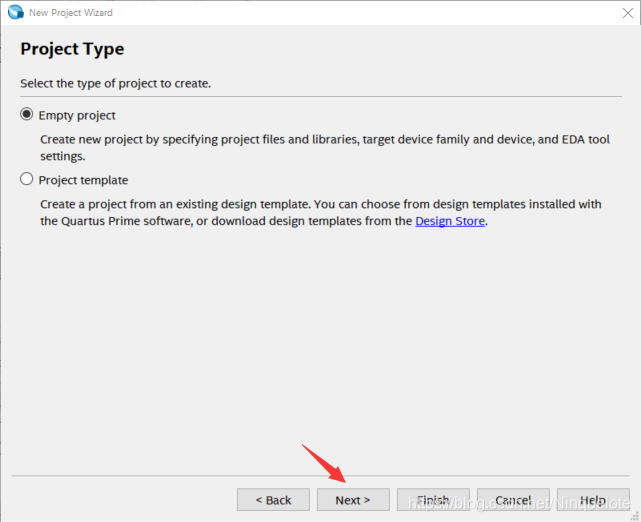

选择“Next”

-

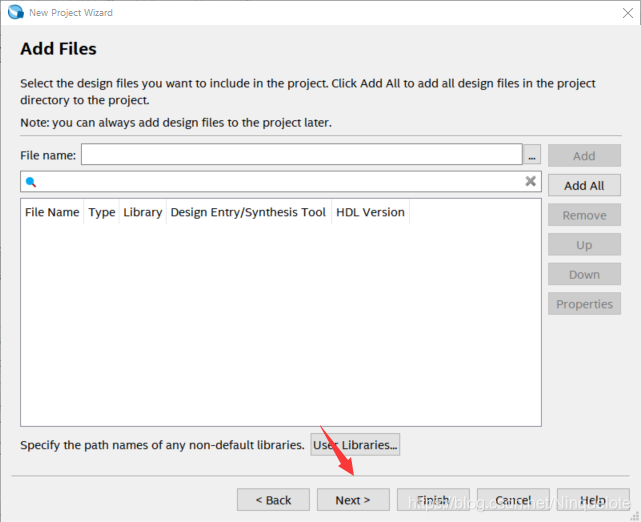

选择“Next”(因为我们是没有代码的,所以这里不需要 Add Files)

-

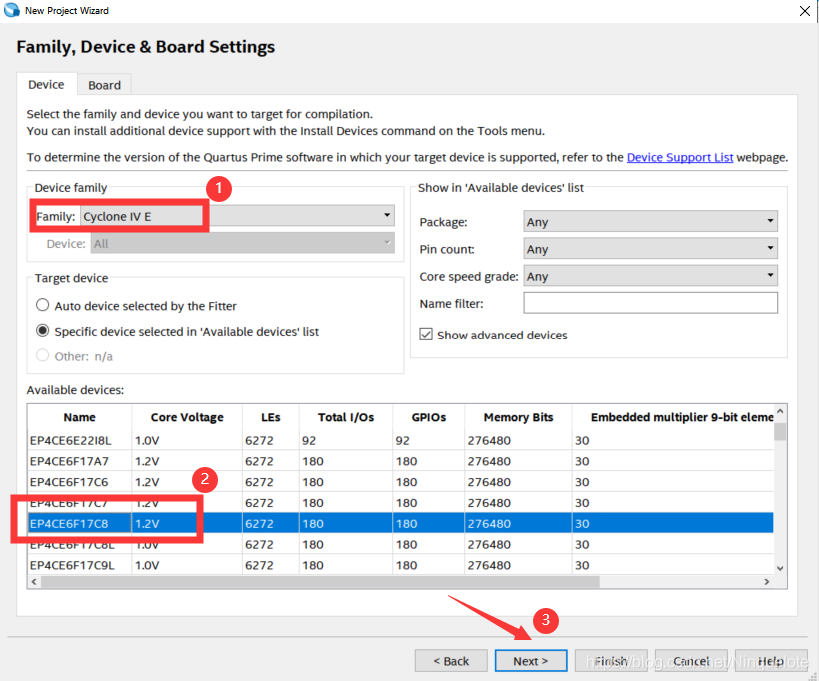

选择器件型号

Family这里,选择芯片的系列,如果你的芯片系列是Cyclone IV,就在上面选择Cyclone IV。但如果你发现你的芯片在这个上面没有,同时这个版本是支持这个芯片系列的,那么就是没有添加这个芯片的器件库,你需要上网找一下,下载你这个Quartus版本对应的芯片器件库,然后添加到软件路径里。

在 Available device 里,选择自己开发板的芯片型号,点击后选择“Next”

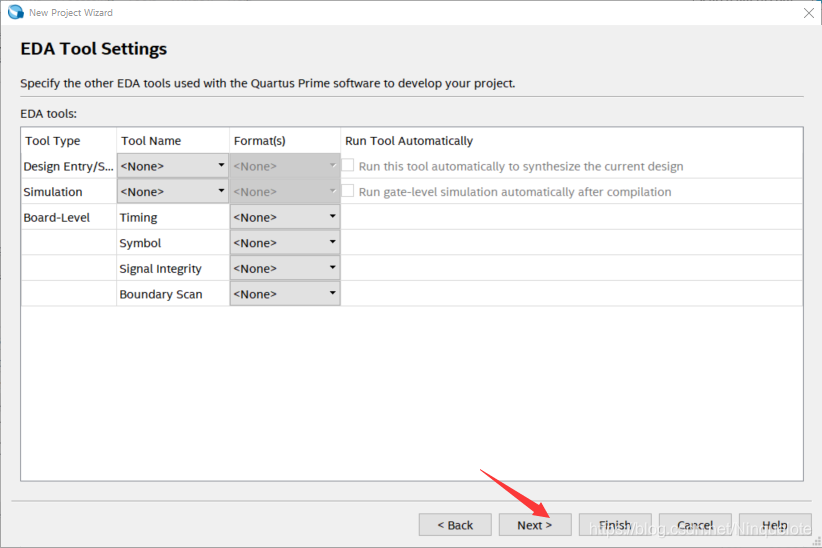

- 选择“Next”

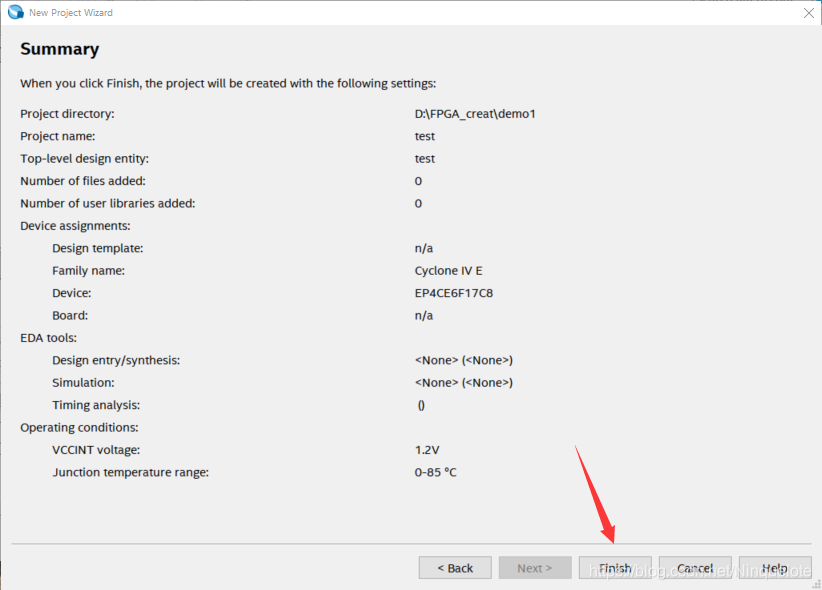

- 确认无误,选择"Finish"

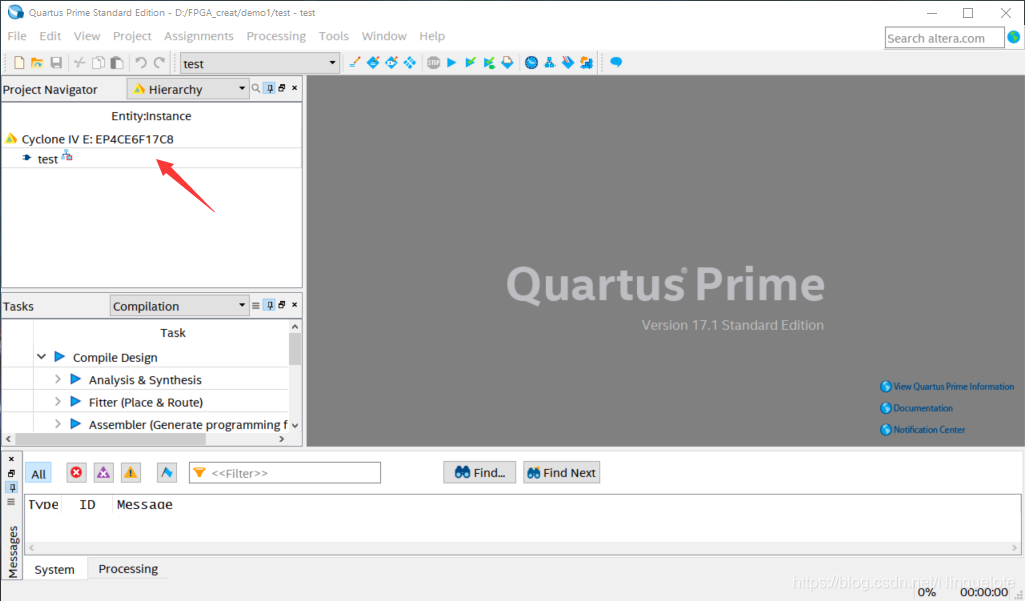

- 现在出现的,就是我们刚刚新建好的工程了。

二、代码的写入

-

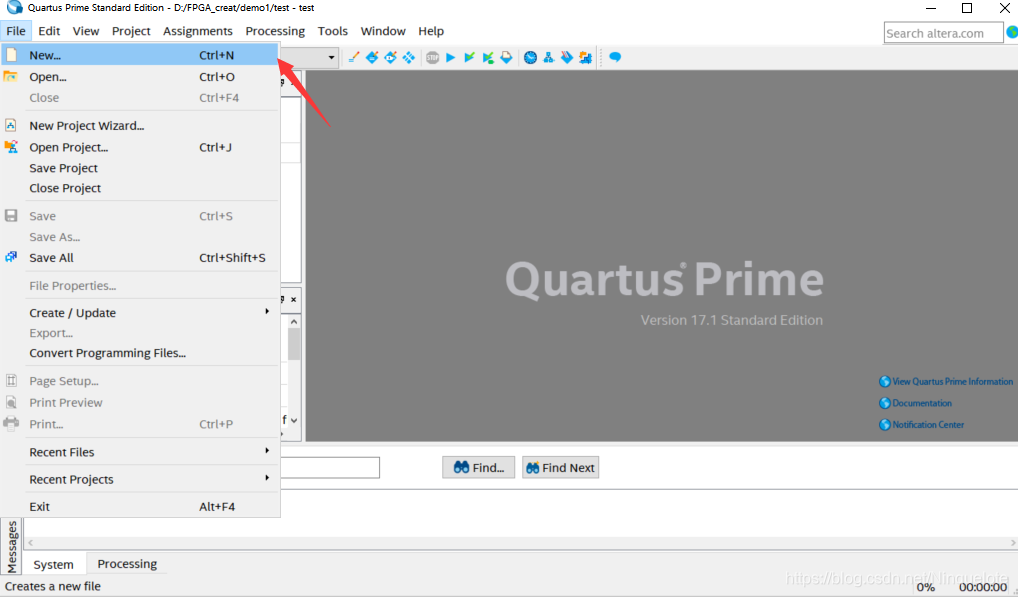

新建代码文件

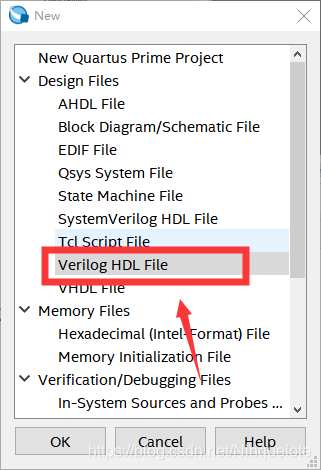

此处我用的是Verilog代码来描述这个硬件电路,FPGA支持多种代码来进行HDL描述,例如VHDL,System Verilog,Verilog HDL,等……

-

选择 “Verilog HDL File”

-

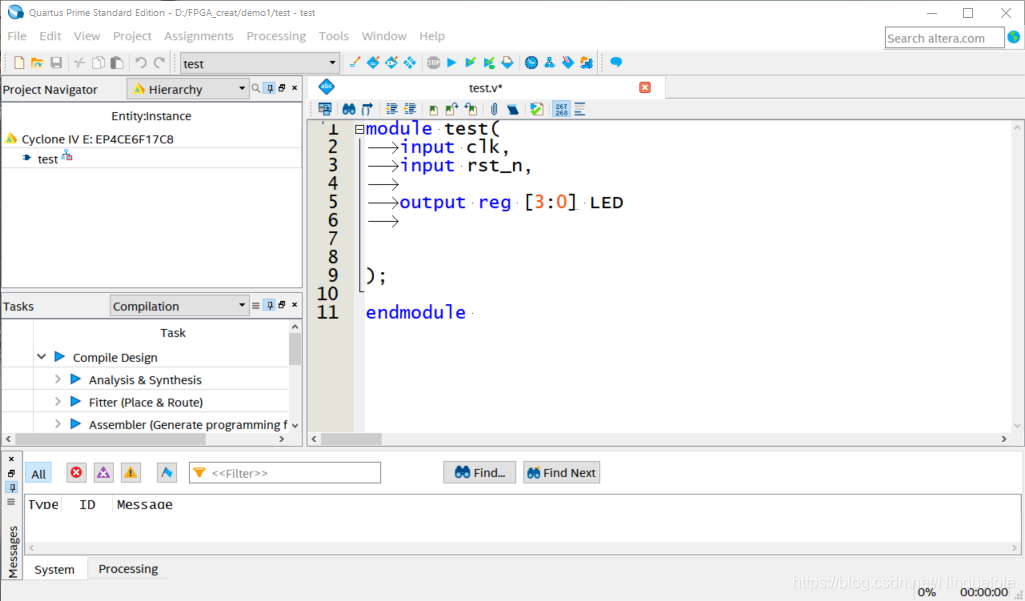

编写代码

因为流水灯是一个很简单的代码,所以我只用了一个文件,因此不存在文件的例化和顶层文件的问题。(模块例化放在下一个博客讲)

先说顶层文件

顶层文件顾名思义,就是最“顶层”的文件,也可以理解为就是C语言里头的main文件,对于工程来说,top文件里包含了所有其他模块(也就是其他文件)的例化;如果工程只有一个文件,那么这个文件就是顶层文件。

顶层文件有一个要求,命名必须要和工程名字一致,也就是工程名字,顶层文件保存的命名,和顶层文件module的命名,都必须一样,否则编译的时候会被认为不属于一个工程。

-

工程的编译与综合

(因为这个博客只想介绍过程,代码什么的下次再说)

在Quartus的工具栏上,有三个编译的小箭头,但是这个编译效果并不一样

Start Compilation是完整的系统工程综合,包括代码的编译,时序约束、管脚约束, 适配和最终生成sof文件,分析时序。

Start Analysis&Elaboration只是编译代码的正确性,生成HDL语言描述的硬件结构图,RTL逻辑图,展开结构。

Start Analysis&Synthesis这一步更进一步,具体生成啥文件,我也不是很懂,如果需要用sjgnaltap抓数据,就必须走过这一步

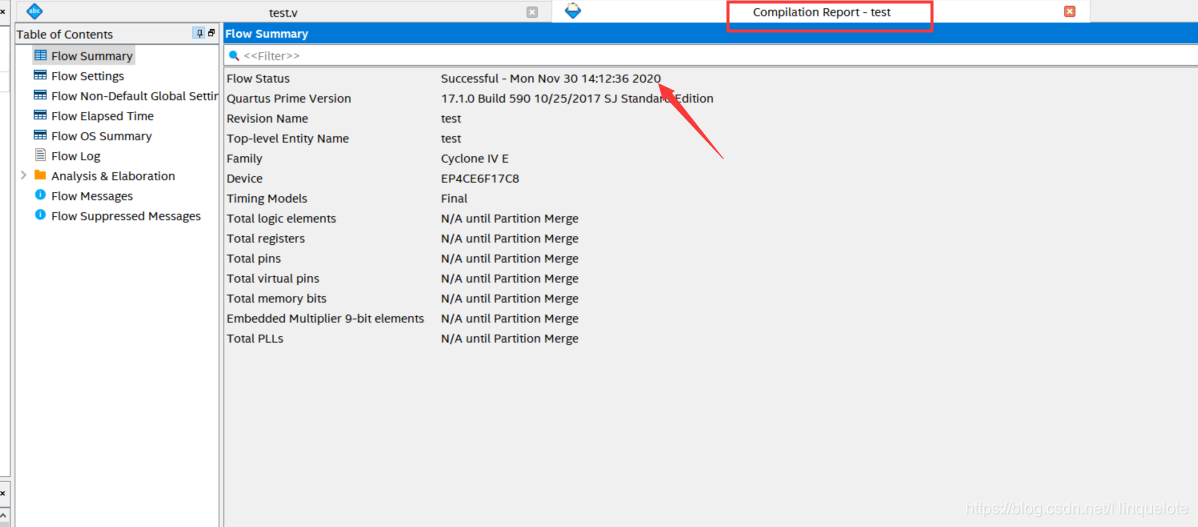

对于我们普通的入门代码来说,首先是对代码逻辑进行分析,也就是中间的小箭头。编译成功之后,会提供一个Compilation Report,告诉你算是编译成功了。

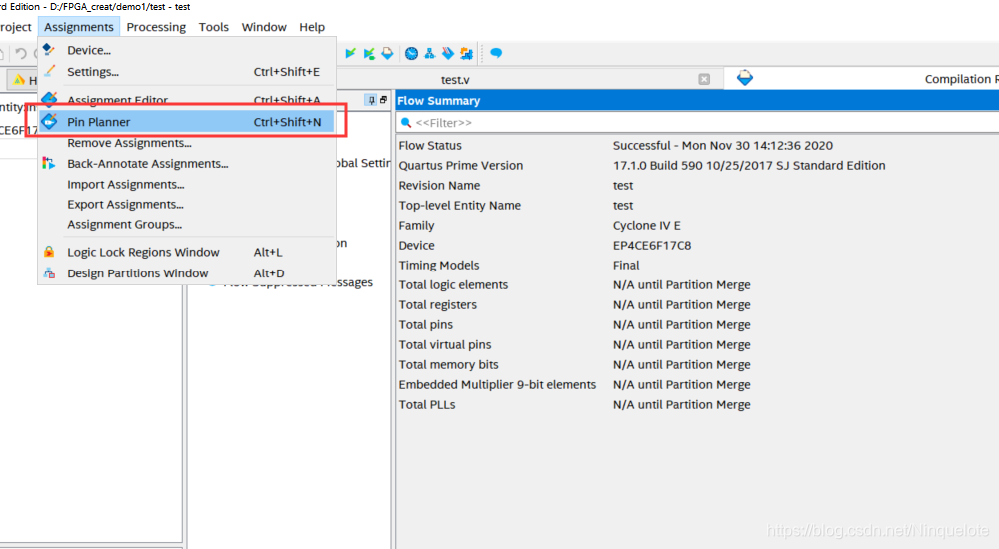

然后是对这个工程分配管脚(Quartus II是默认一般不进行时序约束的,或者俗称你的代码太简单了,还不配进行约束。我在Quartus写程序,一般是超过15k的逻辑资源才会进行时序约束,因为那个时候的时序约束才有实际意义,或者说才能看出一点点效果)

工具栏上面选择Pin Planner,或者选择 Assignment – Pin Planner

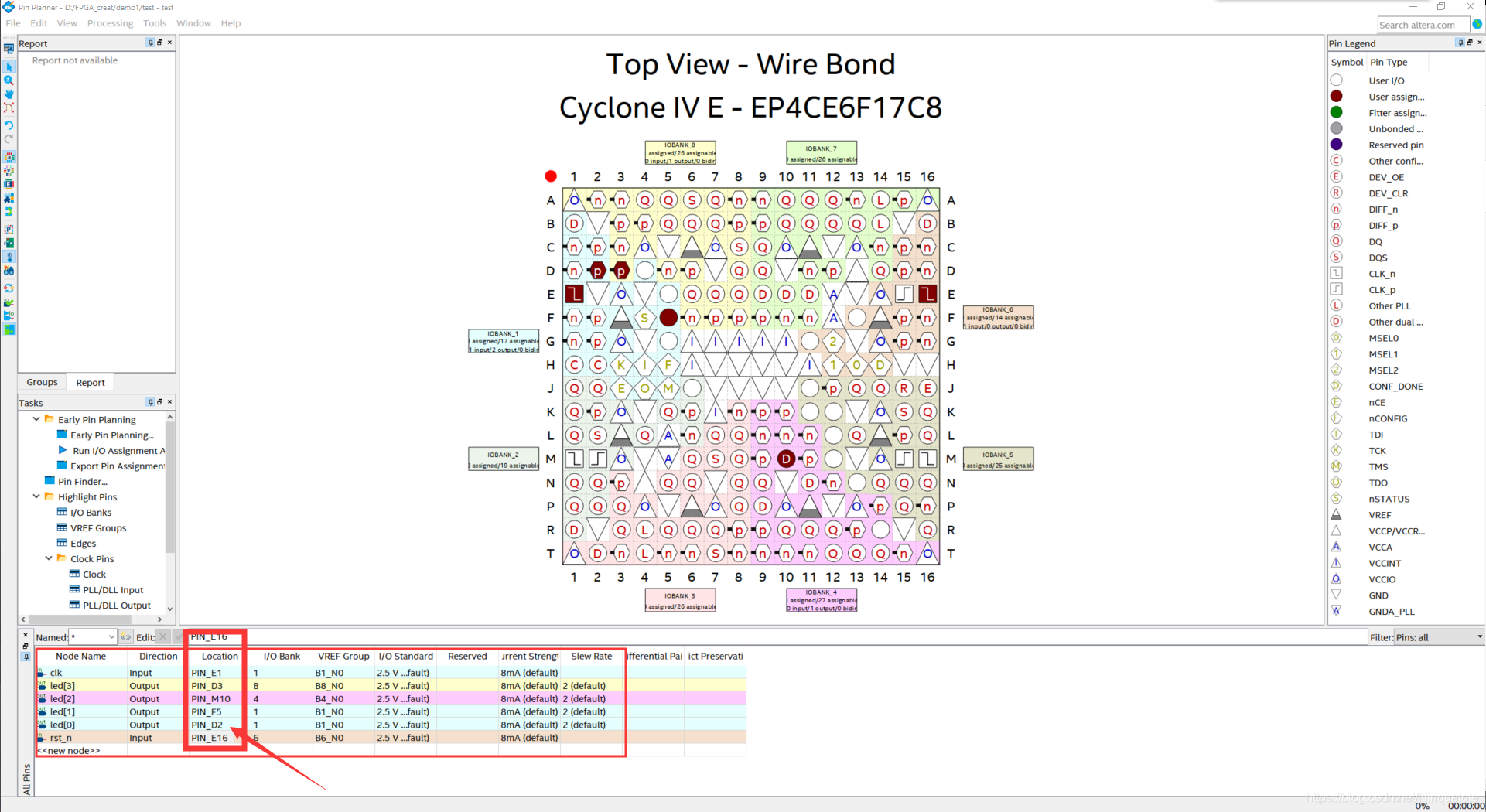

打开管脚配置界面,开始配置I/O(根据开发板给的用户手册)

我是瞎配的(图),在红框里点击输入就可以配置IO了。

配好之后关闭界面(自动保存),然后点击第一个小箭头,进行工程综合。

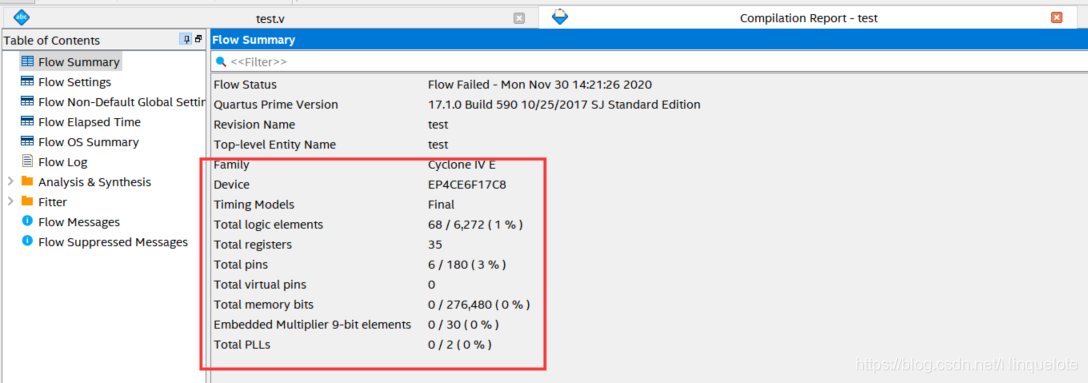

给出的Compilation Report 就会显示你具体用了什么逻辑资源,比如PLL,IO口,LUT,寄存器资源,还有像存储单元这样的。

这个时候就可以进行下一步,烧录代码了。

- 代码的烧录与下载

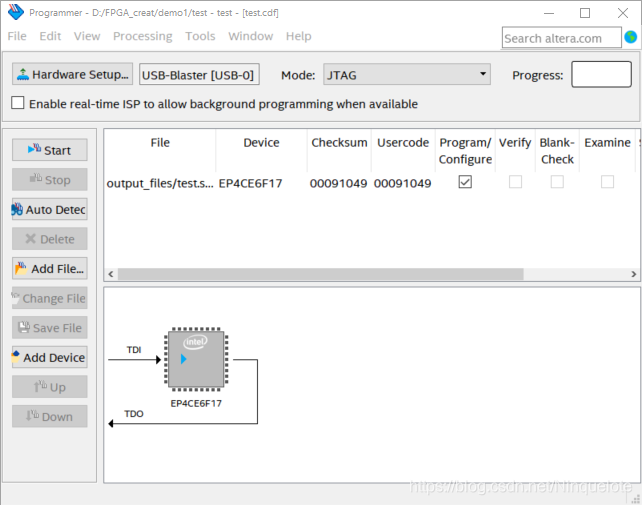

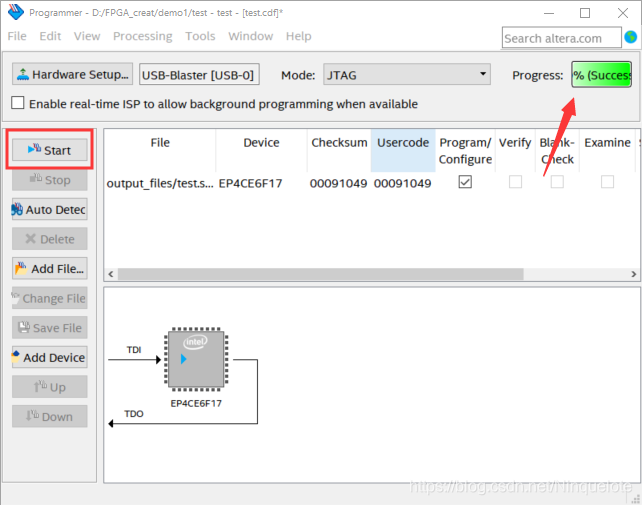

在工具栏选择Programmer

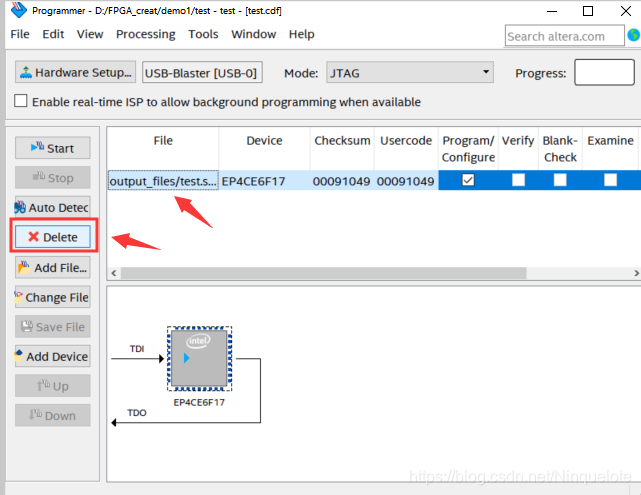

出现下载界面。

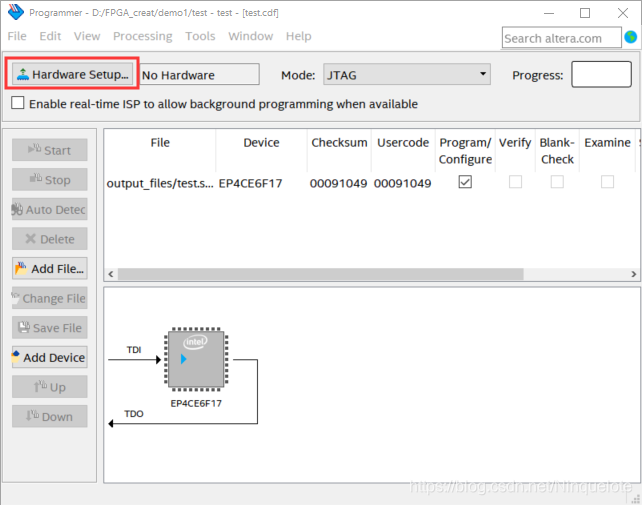

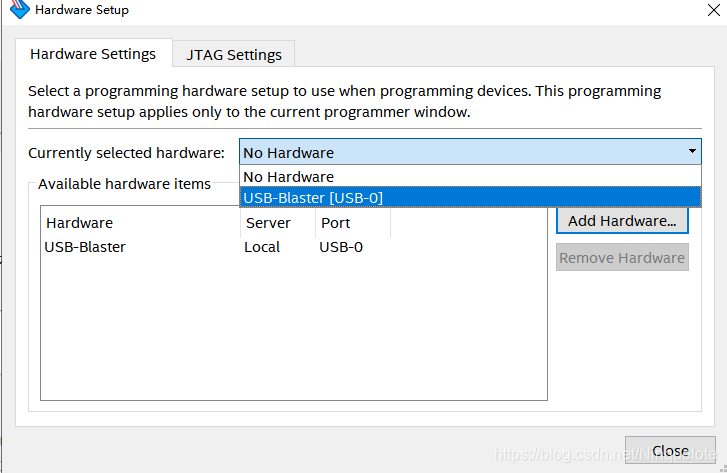

如果发现下载器没有识别到的话,可能是它没有自动接入,这里手动连接一下。

这样就OK了,如果界面芯片没有出现,或者是程序不正确,稍微调整一下就可以。

首先,点击文件,删除。

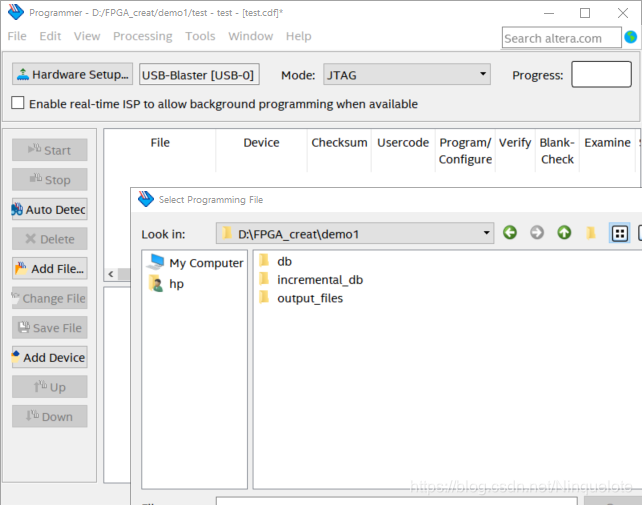

在新界面选择“Add File“

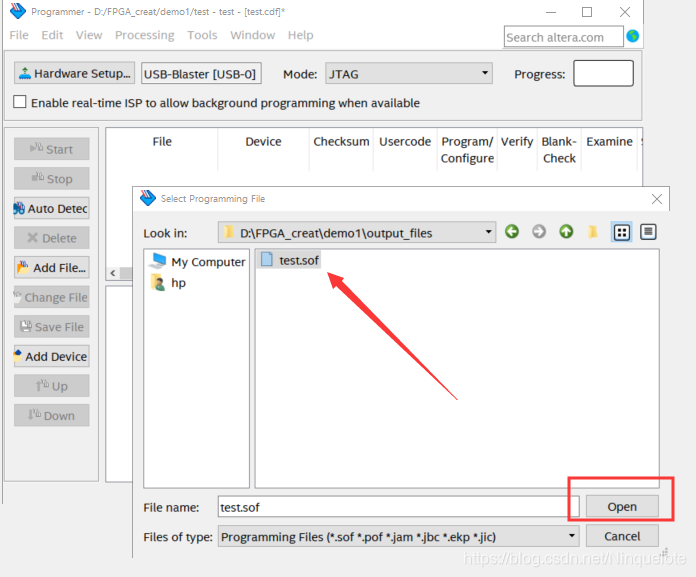

选择”output_file”进入,选择sof文件。

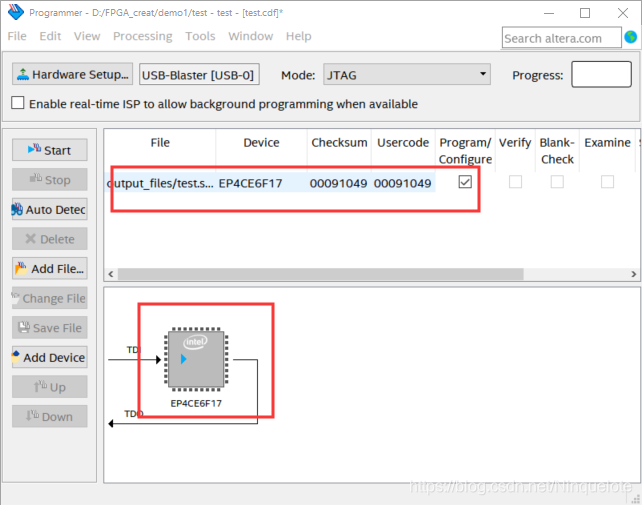

完成,现在下载界面就会出现一个芯片,还有你写程序的下载文件。

点击“Start“,进行下载,下载成功后,***Progress***那个会出现100%,告知你下载成功。

这样你就可以在开发板上看到你的效果了。

——————————————正文结束的分割线——————————

看完喜欢的话请点个赞再走吧QUQ~

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?