主时钟概念

- 主时钟通常是FPGA以外的板级时钟(晶振、数据传输的同步时钟)或FPGA的高速收发器输出数据的同步恢复时钟信号等;

- 约束主时钟时,必须关联FPGA设计网表中已有的某个时钟节点或引脚(定义整个时序分析的时序零点);

- 主时钟的定义需要优先进行;

主时钟约束语法

creat_clock -name<clock_name> -period<period> -waveform{<rise_time><fall_time>} [get_ports<port_name>]

- clock_name:创建的主时钟名称,若后续的约束需要引用一句定义的主时钟,则clock_name为唯一标识;若该项缺省,则默认使用<port_name>所指定的时钟物理节点作为时钟名称;注:在定义虚拟时钟时,不指定<port_name>,必须指定<clock_name>

- period:创建的时钟周期,单位为ns,取指必须大于0;

- port_name:表示主时钟的物理节点为FPGA引脚;FPGA内部的时钟网络也能作为主时钟的物理节点,可以使用get_nets进行定义

设计时钟识别

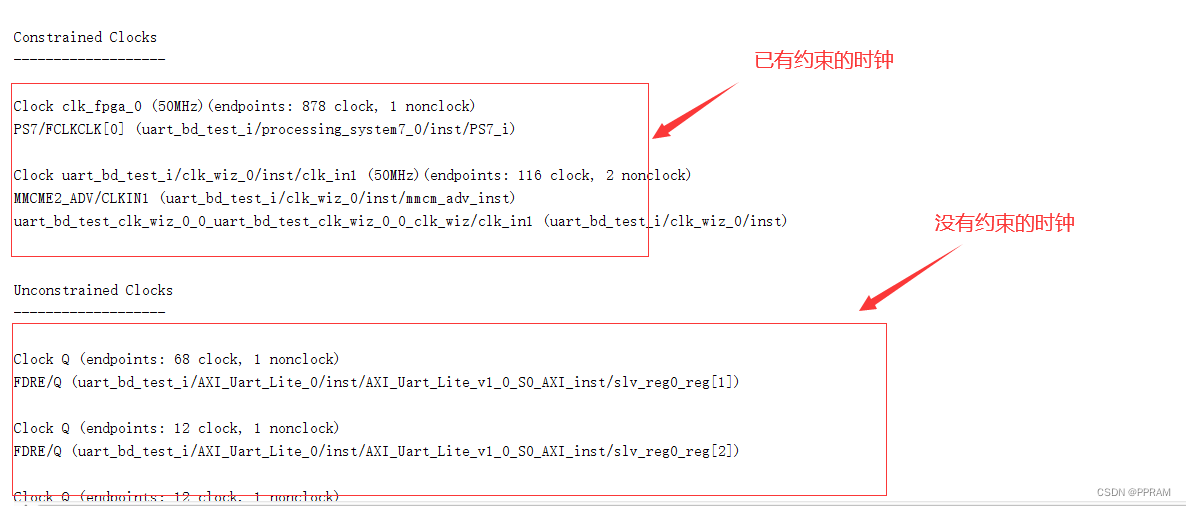

通过查看时钟网络报告和时序确认报告,可以掌握设计中的所有时钟信号,识别需要进行约束的时钟信号,获取其基本信息,以便更好地对其添加约束;

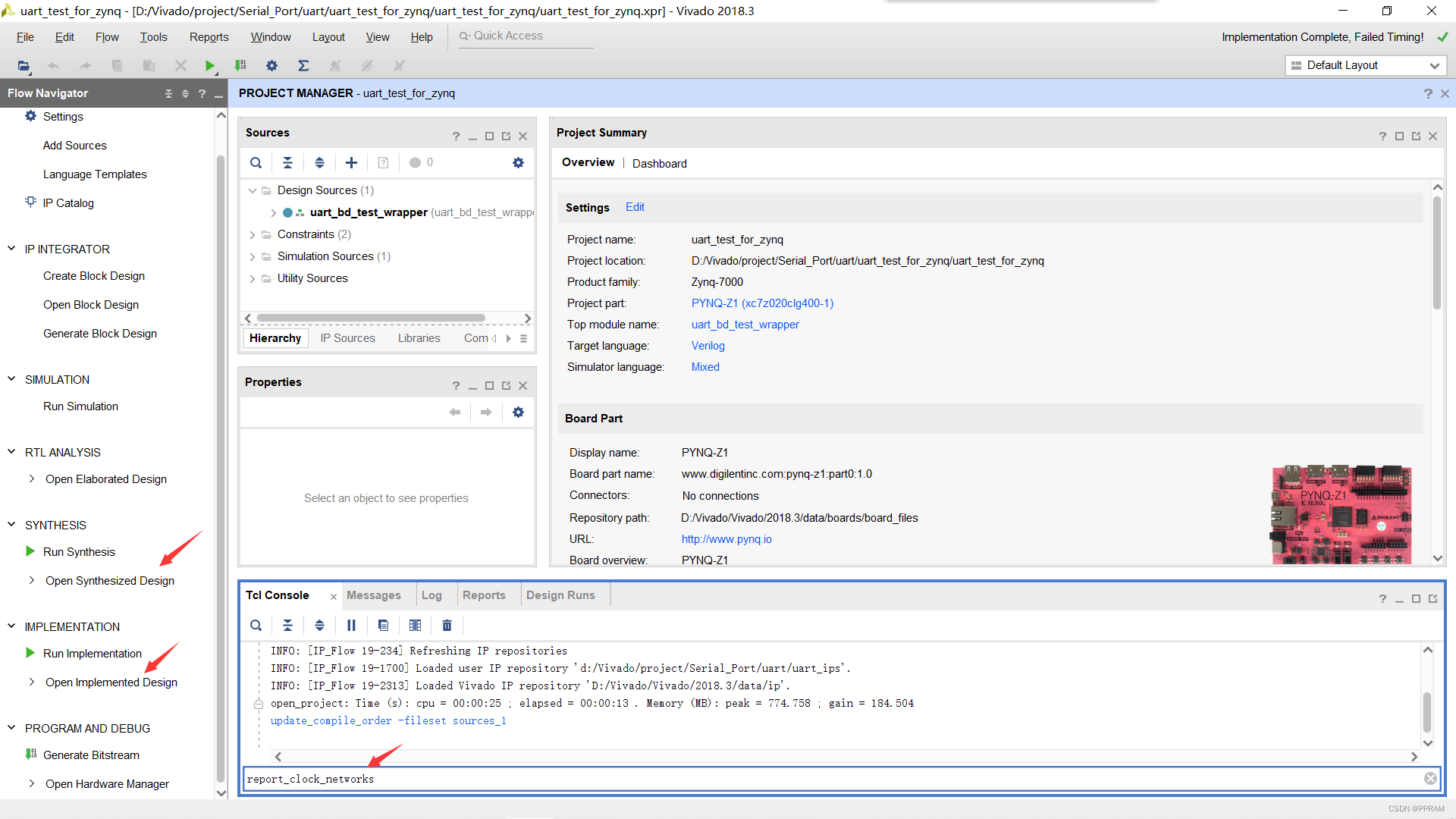

1)时钟网络报告

首先进行实现Implemented Design -> Open Implemented Design

然后 Tcl_Console -> report_clock_networks

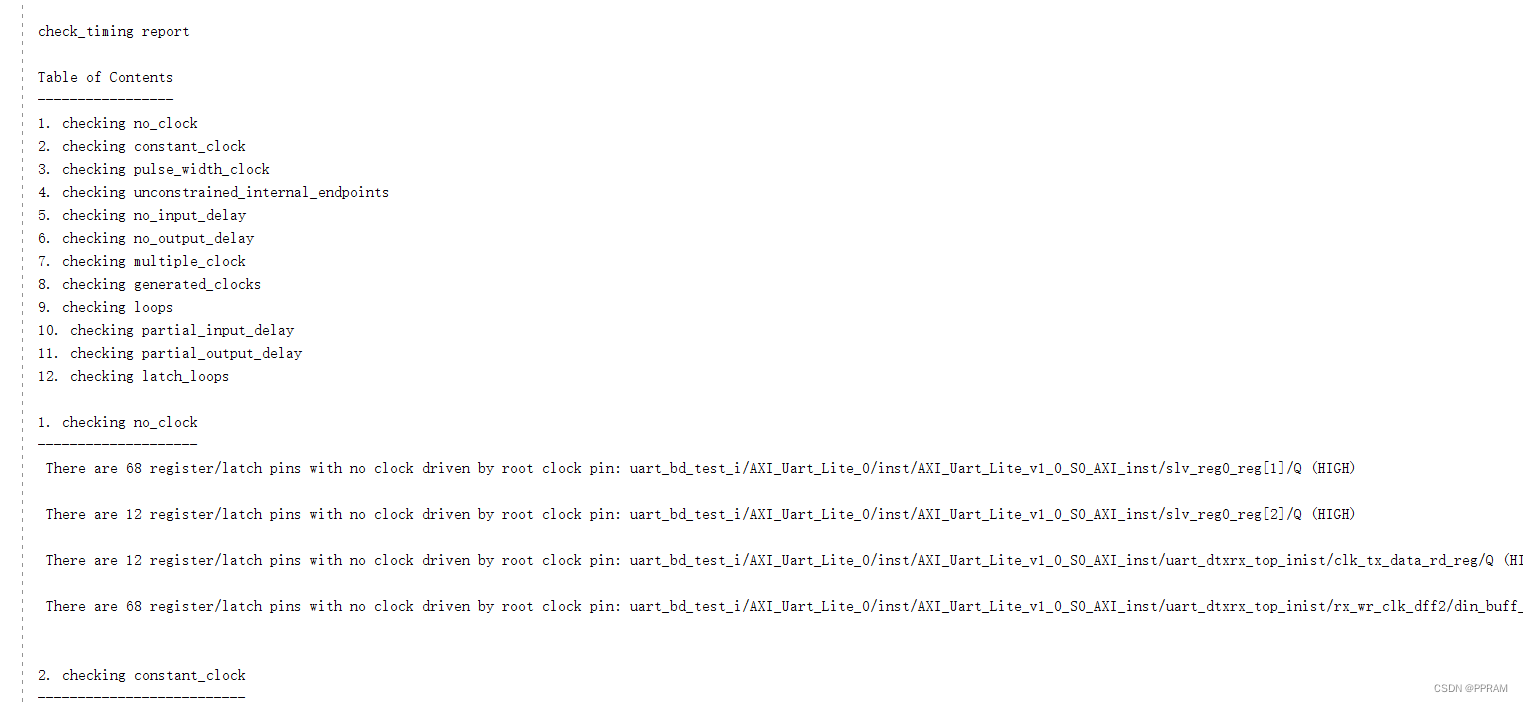

2)时序确认报告

Tcl_Console ->check_timing

主时钟约束实例

1)创建主时钟Sysclk 周期为10ns 占空比为 50%

creat_clock -name Sysclk -period 10 -waveform{0 5} [get_ports Sysclk]

- 从引脚输入的主时钟devclk 周期为10ns 占空比25% 90°相移

creat_clock -name devclk -period 10 -waveform{2.5 5} [get_ports devclk]

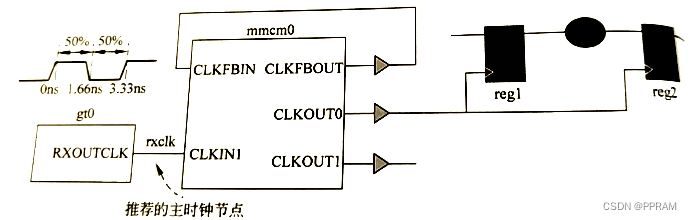

- 高速传输器输出的主时钟约束

creat_clock -name rxclk -period 6.667 [get_nets gt0/RXOUTCLK]

4)差分信号的主时钟约束

creat_clock -name sysclk -period 3.33 [get_ports sys_clk_p]

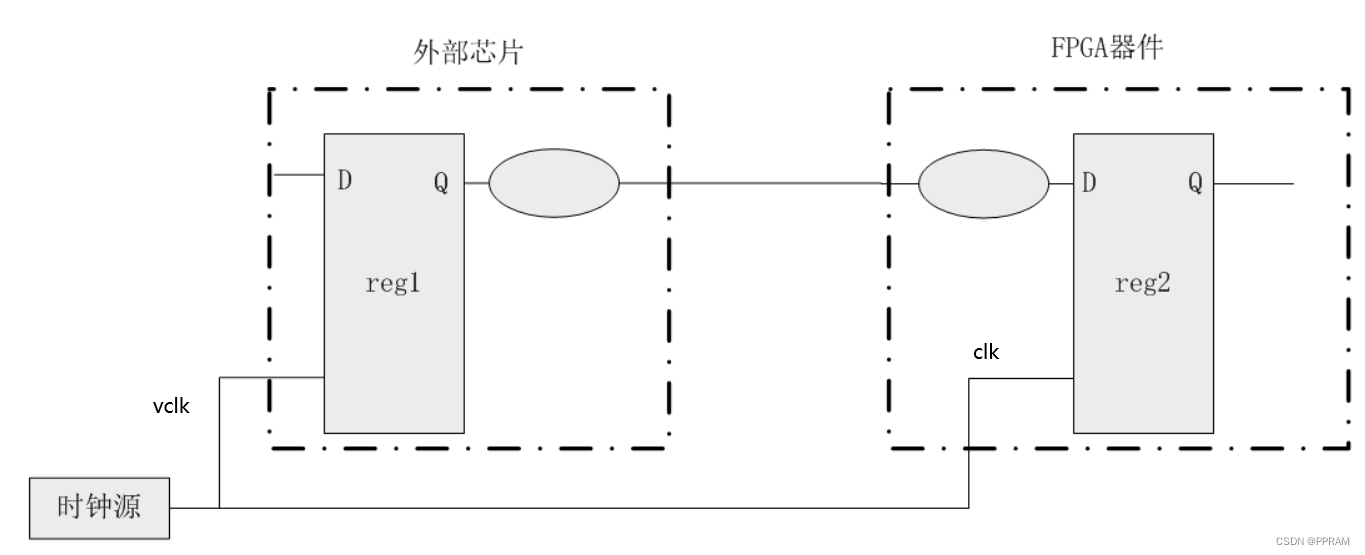

虚拟时钟概念

- 在一些时序路径中,如一些引脚上的数据信号,其同步时钟只存在于外部芯片,并不存在于FPGA内;

- 需要定义一个虚拟时钟用于描述时序数据引脚的外部时钟信号;

- 虚拟时钟并不是实际存在于FPGA中的,因此它在定义时无须依附于任何设计中的实际物理节点;

虚拟时钟的应用场景

- 时序分析(一般是I/O引脚相关的时序路径)的参考时钟并不是FPGA内部的某个设计时钟;

- 与FPGA器件的I/O路径相关的内部驱动时钟与其板级驱动时钟并不是完全同步的;

- 设计者希望对I/O的驱动时钟指定一些特殊的抖动和延时值,但又不希望影响此时钟在FPGA内部的时钟传输特性;

虚拟时钟约束实例

1)系统同步时钟的pin2reg的虚拟时钟约束

目的寄存器reg2的时钟是真实存在的,而源寄存器的主时钟不会传输到FPGA; 1.同频同相

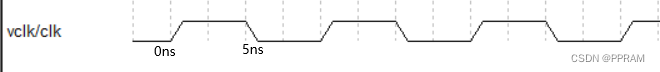

1.同频同相

creat_clock -name VIR_CLK -period 10.000 -waveform{0.000 5.000}

creat_clock -name SYS_CLK -period 10.000 -waveform{0.000 5.000} [get_ports clk]

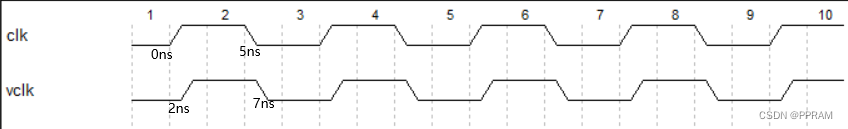

2.同频异相

creat_clock -name VIR_CLK -period 10.000 -waveform{2.000 7.000}

creat_clock -name SYS_CLK -period 10.000 -waveform{0.000 5.000} [get_ports clk]

2)系统同步时钟的reg2pin的虚拟时钟约束

源寄存器reg1的时钟是真实存在的,而目的寄存器的主时钟不会传输到FPGA;

1.同频同相

creat_clock -name VIR_CLK -period 10.000 -waveform{0.000 5.000}

creat_clock -name SYS_CLK -period 10.000 -waveform{0.000 5.000} [get_ports clk]

2.同频异相

creat_clock -name VIR_CLK -period 10.000 -waveform{2.000 7.000}

creat_clock -name SYS_CLK -period 10.000 -waveform{0.000 5.000} [get_ports clk]

3642

3642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?