前面的博客中,介绍了有关时序分析的基础,光说不练可不行,接下来的博客就对Vivado的时序分析工具操练一番。所使用的工程是一个以太网收发数据的工程。

1. 基准时钟约束

基准时钟,也就是有FPGA外部输入到管脚从而进入FPGA内部的时钟。通常需要对这个时钟进行约束,编译器才能识别出其周期是多少。约束基准时钟,简单来说,就是为了让综合工具知道输入的驱动时钟的周期等信息。

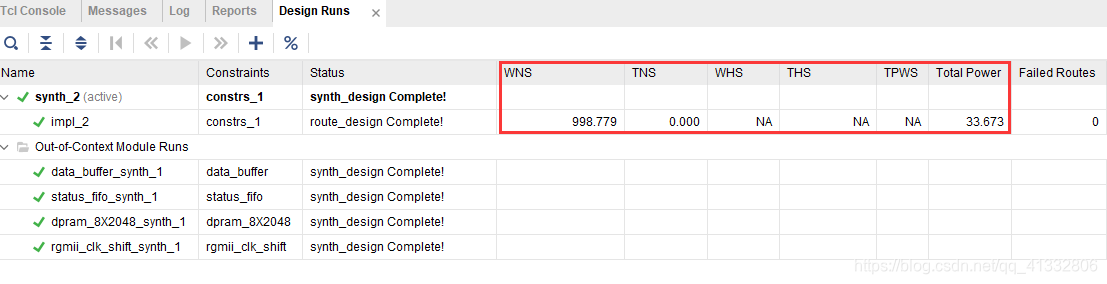

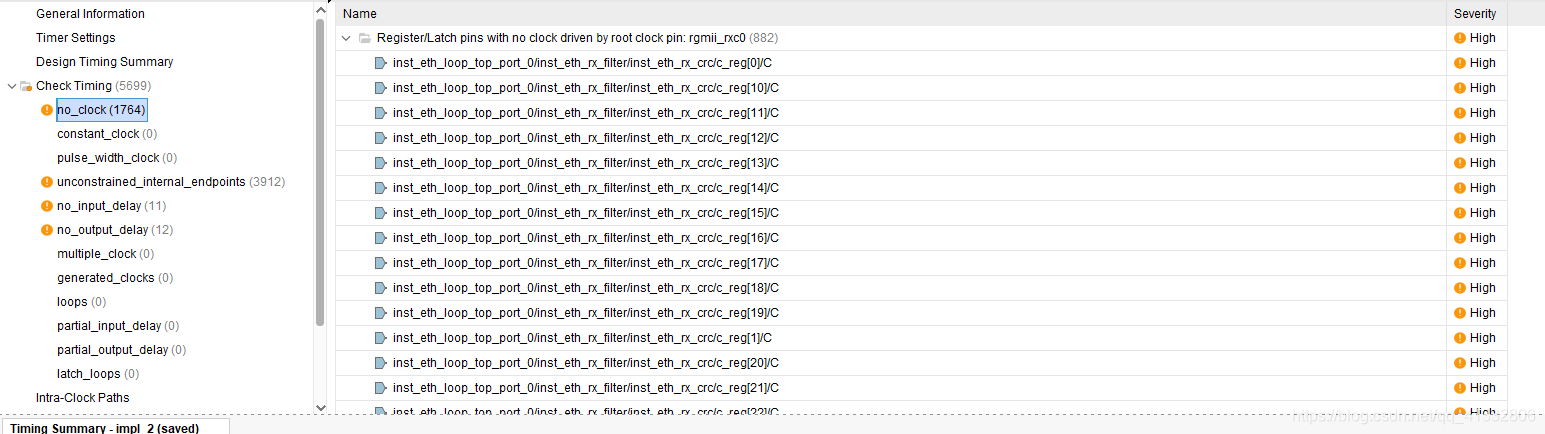

这里有一个已经综合好的工程,当前没有对输入的以太网时钟rgmii_rxc进行约束,可以看到当前时序信息虽然没有报错。但是当前的工程的设计是不完整的。若打开时序分析工具,可以看到会有一些黄色的提示信息,提示信息表明当前没有时钟和内部端点没约束。

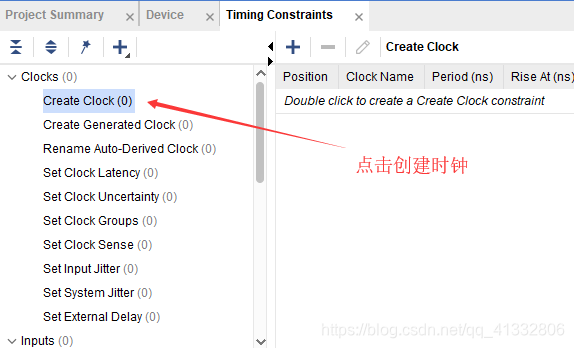

此时对基准时钟进行约束:

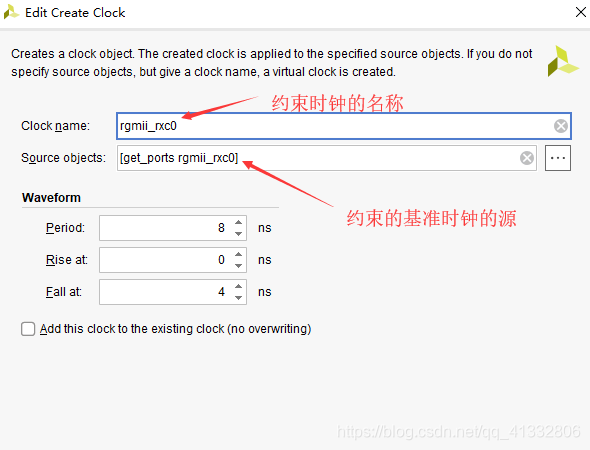

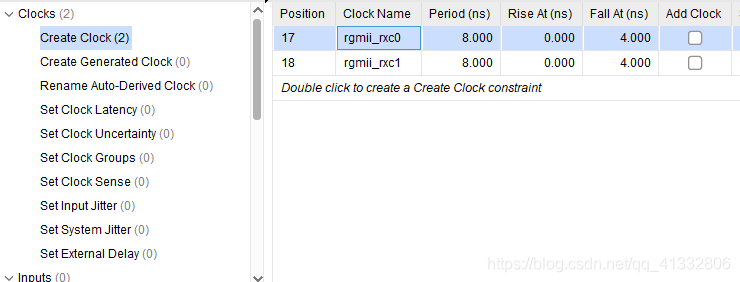

点击+号,可以创建一个时钟,首先要输入要约束的时钟的名称,然后要选中时钟的源。在我这个工程中,有两个以太网,每个以太网口都有一个输入时钟,首先找到rgmii_rxc0,然后设置其周期。

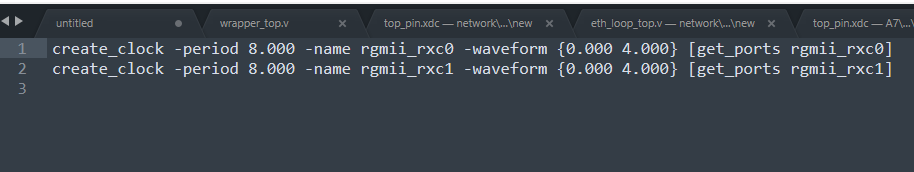

然后可以发现新增了两条约束,保存,就会把约束信息添加到约束文件中,这里选中新增一个文件,用于保存时序相关的约束。

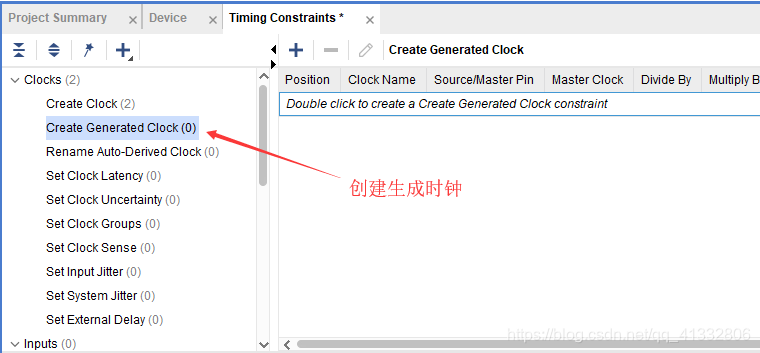

2. 生成时钟约束

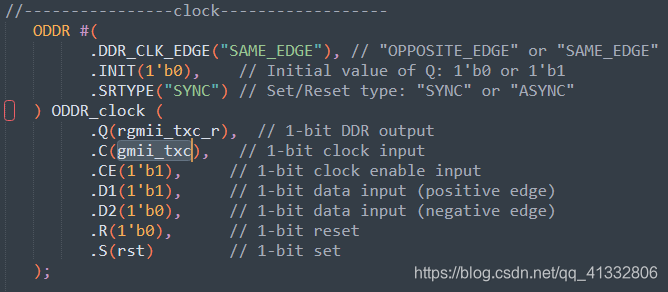

生成时钟有多种,可以是由PLL分频倍频得到的,也可以是用户自己分频得到的时钟。通过PLL生成的时钟,就不需要添加生成时钟约束了,但是其他方式生成的生成时钟,就需要添加约束了。在这个工程中,以太网的输出时钟是通过ODDR原语输出的。并没有对其进行约束,若在将来要考虑output_delay时,没有这个时钟,就无法进行output delay的约束了,因此需要对这个生成时钟进行约束。

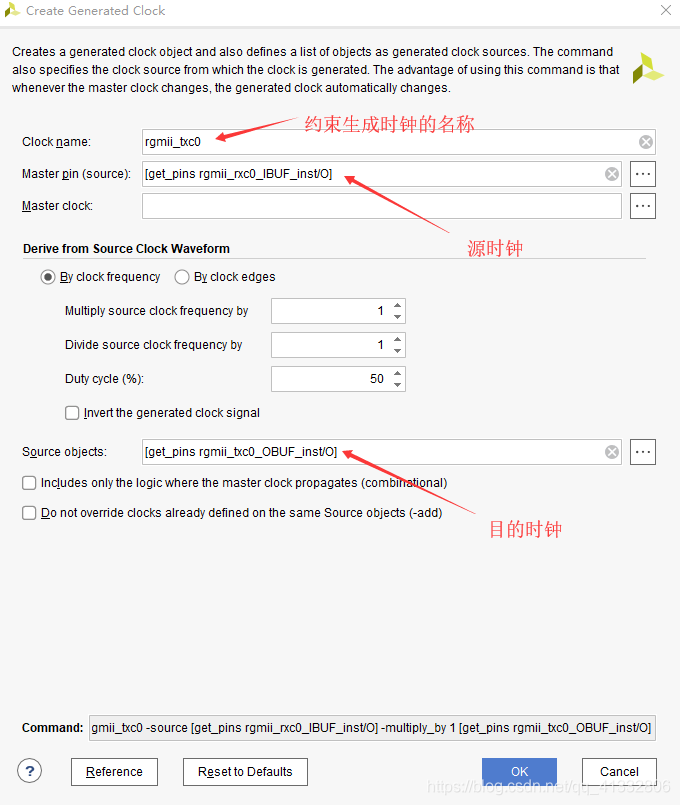

对生成时钟呢,约束方法,与上面的基准时钟差不多。

生成时钟的约束,需要知道生成时钟的源时钟和目的时钟,本工程里面的rgmii_txc是以太网输出时钟,直接就是由输入的时钟驱动的。

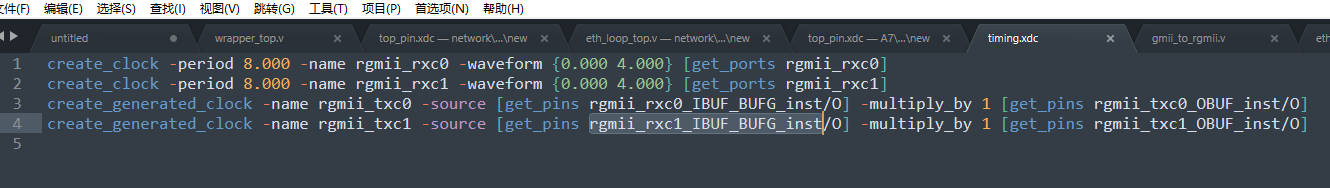

约束完成后的约束文件。

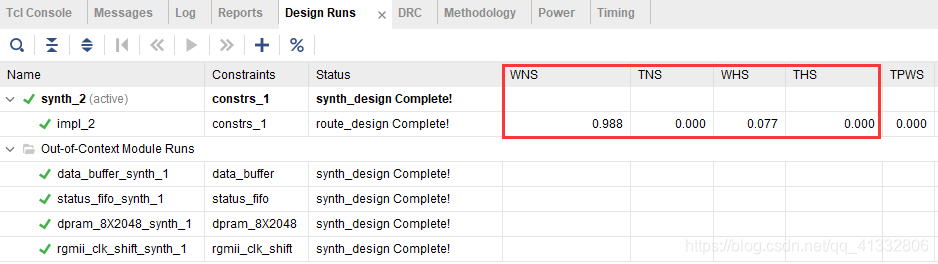

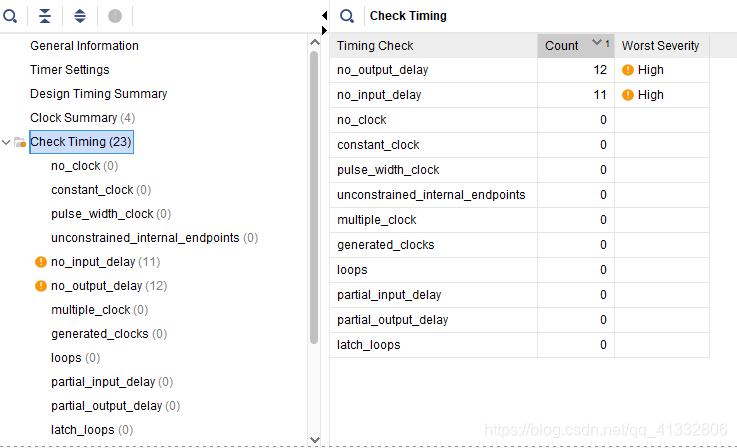

添加完约束后,重新综合,然后再次查看时序报告,就可以看到更新后的时序报告。可以看到综合后的结果与之前不同。可以看到,前面没有添加约束的那些提示信息已经没有了,还剩下input delay和output delay没有约束。

到这里基准时钟和生成时钟就已经约束完成了。

3. 虚拟时钟

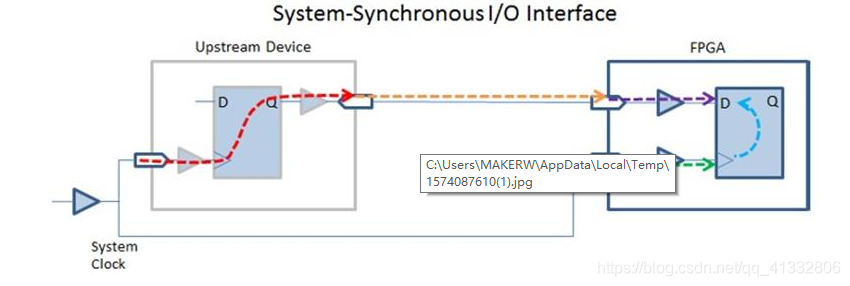

虚拟时钟一般用于系统同步的情况下,即整个系统是由同一个时钟来驱动的,这样在FPGA进行分析时,就不知道上游芯片传来的数据和时钟之间的关系,因此需要添加一个虚拟时钟来帮助分析这种情况。虚拟时钟的约束与生成时钟完全一致,只要不指定生成的源时钟,就生成了一个虚拟时钟的约束。

当前这个工程被我这么搞了不能正常工作了,因为原来系统的时钟rgmii_rxc是经过了PLL移相来采集数据,现在没有移向,导致我采集到的数据不对,整个系统就不能通信了,因此在之后的将解决这个问题。

参考:

V3学院资料

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?