1.2 PC读写访问板卡

那PC 如何读写板卡的数据呢?简单的解释, PC 启动是, BIOS 探测所有的外设。对 PCIe( PCI)设备来说, BIOS 检测到板卡有多少个 BAR 空间,每个空间有多大,然后对应为这些 BAR 空间分配地址。对 PC 设备来说,它能“看”到 PCIe 板卡的空间只有 BAR 空间,也就只能访问这些 BAR 空间。也就是说,板卡可以发送合法的PCIe TLP 包,并得到 PC 端的相应;但是 PC 端访问板卡被局限在 BAR 空间。

简单来说,PC机想操作PCIE设备的内存空间,只能通过bar空间来进行操作。PC机只能看见bar空间(忽略地址起始和开始),PCIE核通过检测不同的地址来判断要进行task1还是task2。

2. Pcie是一种总线。总线是用来传输数据,例如USB是一种总线,Pcie是一种总线,串口也是一种总线。

DMA是一种内存访问技术。它允许电脑外设(网卡、显卡),可以独立地直接读写系统内存,而不需中央处理器(CPU)介入处理。

3.

generate -if 语句不需要 genvar,可以不对 generate 块进行命名,而且可以不写 begin / end。由于在一个 generate - if 语句中通过判断语句最多执行一个代码块,所以对各个代码块用相同名称命名是合法的,且有助于保持对代码的层次化引用[2]。

需要注意的一点是,在 generate 块中的判断条件必须是常量!

ADC知识点:

1. 采样率(采样时钟频率):250MSPS(1S中采250M个点及频率为250MHZ)

2.dbfs(db full scale):dbfs=20log10(x/1111 1111 1111),eg:fin=-1dbfs 通过该公式算出来为满幅度的0.8913

3.采样两点间隔(采样周期)时间最好大于adc的转换时间

4.采样时钟的选取

三、具体分析如下

(1)我们的输入信号是50Hz (周期为20ms),初步定为1周期200个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个采样点间隔为20ms/200=100us,在一个输入信号周期(20ms)内100us就要采集一次,以下计算都是以一个输入信号的周期为单元进行计算。

ADC可编程的通道采样时间我们选最小的1.5周期,则ADC采样周期一周期大小为

根据采集时间间隔来计算采集完200个点需要以什么样的频率才能完成,这个频率就是ADCCLK,当采样时间1.5周期:100us/1.5≈66us。 根据f=1/T公式,ADC时钟频率为1/66us=1/0.000066s≈15151.515Hz≈15KHz。

ADC可编程的通道采样时间我们选71.5 周期,则ADC采样周期一周期大小为(100us/71.5)。 100us/71.5≈1.3986us,ADC时钟频率为1/1.3986us=1/0.0000013986s≈0.715MHz。

(2)接下来我们要确定系统时钟:我们 用的是 8M Hz 的外部晶振做时钟源(HSE),估计得 经过 PLL倍频 PLL 倍频系数分别为2的整数倍,最大72 MHz。为了 提高数据 计算效率,我们把系统时钟定为72MHz,(PLL 9倍频)。则PCLK2=72MHz,PCLK1=36MHz;

我们通过设置时钟配置寄存器(RCC_CFGR) 中 有 为ADC时钟提供一个专用的可编程预分器,将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为 9MHz

从手册可知ADC转换时间:STM32F103xx增强型产品:ADC时钟为56MHz时为1μs(ADC时钟为72MHz为1.17μs)

(3)由以上分析可知:不太对应,我们重新对以上中 内容调整,提出如下两套方案:

方案一:我们的输入信号是50Hz (周期为20ms),初步定为1周期2500个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个 采样点间隔为 20ms /2500 = 8 us

ADC可编程的通道采样时间 我们选71.5周期,则 ADC采样周期一周期大小为8us /71.5 。 ADC时钟频率约为 9 MHz。

将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为 9MHz

方案二:我们的输入信号是50Hz (周期为20ms),初步定为1周期1000个采样点,(注:一周期最少采20个点,即采样率最少为1k) ,每2个 采样点间隔为 20ms /1000= 20 us

ADC可编程的通道采样时间 我们选239.5周期,则 ADC采样周期一周期大小为20us /239.5 。 ADC时钟频率约为 12 MHz。

将PCLK2 6 分频后作为ADC 的时钟,则可知ADC 时钟频率为 12MHz

5.ADC精度

精度:精度是在ADC最小刻度基础上叠加各种误差的参数。是可以直接衡量ADC采样精准的指标。通常ADC的精度=N*LSB+Vc_sample+Vshift+Vnoise+Vref+… N一般在ADC的数据手册中体现,表征ADC的集散误差。Vc_sample是ADC内部的采样电容引起的误差。Vshift一般是外围电路带来的偏置,Vnoise是综合前端的驱动电路和ADC得出的噪声电压。Vref一般是由参考电压的散差引起的误差。所以从这里可以看出来。虽然一些ADC的分辨率很高,但是需要精度高,还需要做好各个方面的工作,尽量降低系统误差。从而提高精度。

6.(DR)

指模数转换器能处理的最大模拟输入信号与能分辨的最小模拟输入信号的比值。

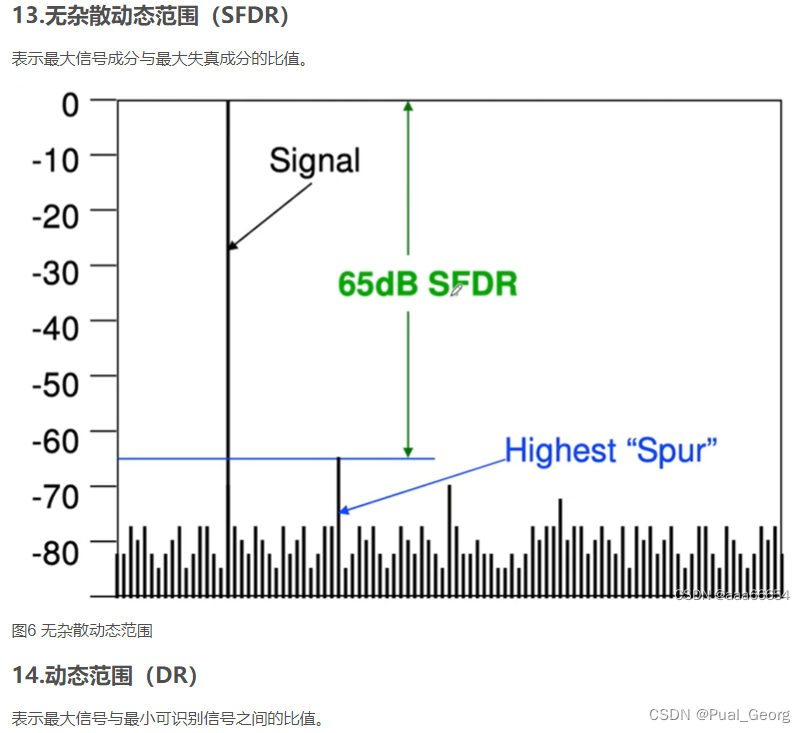

7.SFDR(无杂散动态范围)

指模数转换器 输出 频谱中,信号功率与最大杂波功率或最大谐波功率之间的比值.

8.SNDR(信噪失真比)

指模数转换器输出频谱中,输出信号功率与噪声、杂波、谐波功率总和的比值,即输出信号功率与其余所有非输出信号功率之比。

9.ENOB(有效位数)

有效位数是实际测得的模数转化器的信噪失真比值为衡量标准,来评判其性能相当于理想情况下一个多少位的模数转换器,ENOB与SNDR的关系可表示为下式:

ENOB=SNDR-1.76/6.02

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?