7.1 去耦和旁路特性

去耦和旁路可以防止能量从一个电路传播到另一个电路上去,进而提高电源分配系统的质量。

引入耦合电容,利用电容的充电和放电这一基本特性,其目的是提供充足的动态电压和电流。通过在电路走线和电源层上确保一个低阻抗电压源来实现去耦,以至于使高频干扰能从信号路径有效地转移出去,同时使低频射频(RF)能量相对地不受影响。

去耦:去除在元件切换时从高频元件进入到电源分配网络中的RF能量。去耦电容还可以为元件提供局部化的直流电压源,减少跨板浪涌电流的干扰。

旁路:从元件或走线中转移出不需要的共模RF能量。这主要是通过实现交流旁路消除无用的能量进入敏感的部分,另外还可以提供基带滤波功能。

体电容:信号引脚在最大电容负载状态下同步切换时,用于保持元件里的直流电压和电流恒定。还可以防止由元件产生的冲激电流“dI/dt”引起的电压击穿。

7.2 去耦和旁路电路属性参数

理想的去耦电容器可以提供逻辑装置进行状态变换时所需的所有电流

ESR表示电容器中的电阻损耗 , 高频下的趋肤效应会增加器件的引线电阻值,所以高频ESR大于直流下的ESR。;

ESL也能表示电容器的损耗。

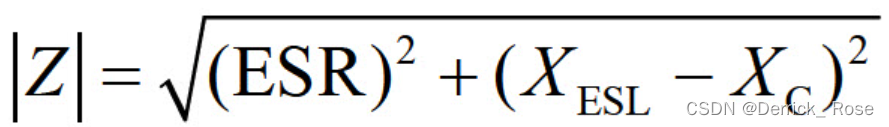

电容器的阻抗用ESR与ESL表示为:

式中,XESL=2πf(ESL);XC=1/2πfC。

ESL的作用等同于寄生电感器,而ESR的作用等同于寄生电阻,他们都与电容器串联。(两者必须要很小)

低于谐振频率以下,电容器表现为容性,高于谐振频率以上,电容器表现为感性

7.3 电源层和接地层电容

多层PCB通常包括一对或多对电源和接地层。

电源层的功能等同于一个低电感的电容器,能够约束在元件和信道上产生的RF电容。

和电容一样,电源和接地层也有非常小的等效引线长度电感,但没有ESR。

在多层PCB中通常是用分立的去耦电容

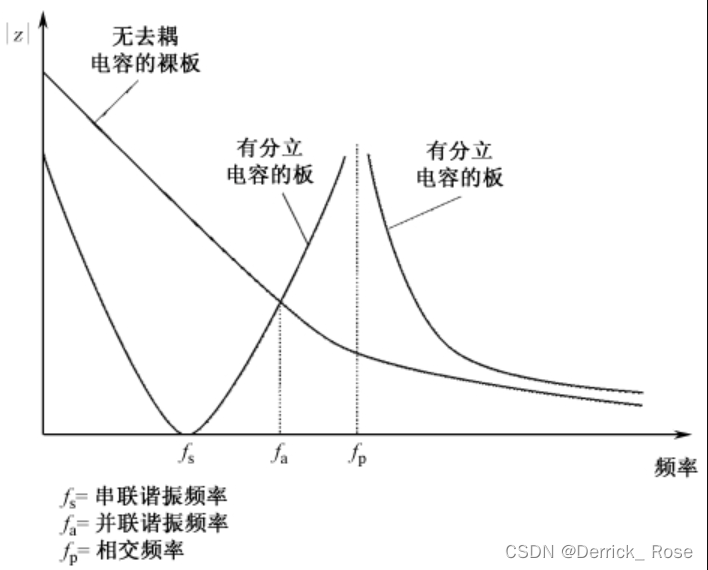

裸板”的阻抗非常接近理想去耦电容器的阻抗

当频率高于fa,附加的n个分立去耦电容不能带来附加的好处,这是因为裸板的阻抗远远小于有独立电容器负载时的阻抗。当接近负载板极点频率(并联共振)时,负载板阻抗的值异常高,负载板的去耦性能比无负载(没有附加分立去耦电容器)时差很多。

减小去耦电容器连线的串联电感是获得在宽频范围内理想性能的关键。

并联谐振对应于极点,串联谐振对应于零点。当提供多个电容器时,极点和零点将交替出现。

在每一对串联谐振频率之间都有一个并联谐振。两个串联谐振间总存在一个并联谐振点。

7.4 电容选择举例

7.4.1 去耦电容的选择

在高速时钟电路中,尤其要注意元件的RF去耦问题,因为元件会把一部分能量耦合到电源/地系统之中,这些能量以共模或差模RF的形式传播到其他部件中。

在PCB上放置元件时,必须提供对高频RF的去耦。必须确保所选去耦电容能满足可能的要求。考虑自激频率的时候需要考虑对重要谐波的抑制,一般考虑到时钟的5次谐波。

在射频(RF)频谱分布中,射频能量随频率下降而减少,从而改善了电磁干扰(EMI)的性能。

在已知时钟信号的边沿速率时,用下式

决定了所要滤除的最高频率时,用下式

tr 信号的边沿速率,Rt 为电路等效阻抗

在使用去耦旁路电容时,需要考虑以下几点:

①使电容的引线最短,线路电感最小;

②选择适合的额定电压和介电常数的电容;

③如果边沿速率的畸变容许3倍于C的大小,应使用大一级的电容标称值;

④电容安装好后,必须检查是否工作正常;

⑤太大的电容会导致信号的过大畸变。

7.4.2 大电容的选择

在最大容性负载情况下,大电容既可为电路提供能量储存,又可以给元件提供直流电压及电流,从而为电路提供稳定的最佳电压和电流

一般在每两个LSI和VLSI器件之间要放一个大电容,另外在下面几处位置也需放置去耦电容。

● 电源与PCB的接口处;● 功率损耗电路和元器件的附近;● 自适应卡、外围设备和子电路I/O接口与电路终端连接处;● 输入电压连接器的最远位置;● 时钟发生电路和脉动敏感器件附近;● 远离直流电压输入连接器的高密元件布置。

获得理想的最佳大电容:

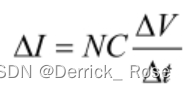

(1)假设板上的所有切换器件同时开关,获得了最大的损耗电流,其中包括逻辑交叉产生的电压冲激效应(交叉电流)。

(2)计算允许的最大电源噪声容限ΔV。

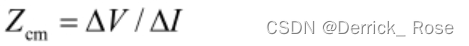

(3)判断电路允许的最大共路径阻抗Zcm:

(4)如果使用实心板,则应分配好连接电源和接地层的连接阻抗Zcm。

(5)计算从电源到板之间连接电缆的阻抗Zcable,在电源合理布线的基础上,通过Ztotal=Zcm+Zcable来决定频率。

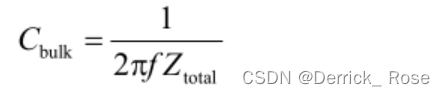

(6)如果实际切换频率低于上式中的计算频率f,则电源布线是合理的。若高于f,则需要加电容Cbulk。在频率为f,阻抗为Ztotal时,可通过下式计算出所需的电容值。

7.4.3 选择电容的其他考虑因素

在选择一个具体电容时,不仅要考虑其自谐振频率,还同样要考虑电容的介质材料工艺。

VLSI及高速元件(如CMOS、ECL、BCT逻辑门器件)需要并联去耦电容。元器件的转换速率越陡峭,产生的射频电流频谱就越大

去耦电容的并联放置一般用于过滤高频RF能量并能对电源板噪声产生旁路作用

7.5 集成芯片内电容

随着时钟频率的提升,每个VLSI器件存在切换电流,切换电流的傅里叶频谱产生RF能量,使得数字器件必然会存在辐射。

切换开关在电源分配网络中的来回转换,会在电源板和接地板之间引起差模电流的不平衡。随着共模、差模电流的失调,在EMI测试中,会发现共模电流在电缆组装连接处或PCB元件中产生辐射。

原文见《高速电路PCB设计与EMC技术分析》

1569

1569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?