在设计和使用DCDC Buck电路时,常见的问题涉及电路设计、元件选型、PCB布局以及实际调试中的异常现象。以下是几个典型问题及其解决方案:

1.输出电压值偏高或者偏低

1)问题现象:输出的电压值与理论设计的电压值有偏差。

2)原因及解决方案:

a)FB反馈的两颗电阻选型设计问题,首先电阻需要选用1%精度,若选用5% 精度可能造成一致性不好,电压偏高或者偏低。

b)FB值差异影响,对于有些pin to pin的电源芯片,其FB值可能有微小差异造成输出电压值与理论设计有偏差,因此设计选型时需注意。

2.电感选型不当导致的问题

1)问题现象:电感发热、啸叫或输出电流不足。

2)原因:电感饱和电流低于实际峰值电流。电感值计算错误,导致纹波电流过大或过小

3)解决方案:使用公式计算电感值:![]() 其中 ΔIL 通常取负载电流的20%~40%。选择饱和电流高于最大负载电流1.2~1.5倍的电感。

其中 ΔIL 通常取负载电流的20%~40%。选择饱和电流高于最大负载电流1.2~1.5倍的电感。

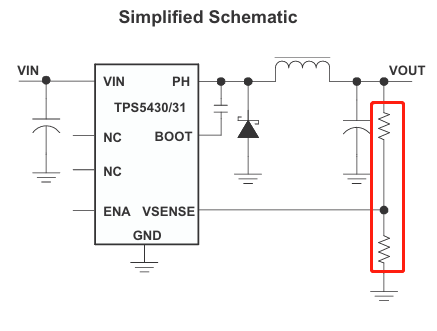

3.自举电容(BOOT电容)问题

1)问题现象:Buck电路中,上管MOSFET驱动不足,导致开关损耗增加或无法正常导通;EMI测试不过,在开关频率及其倍频处有尖峰。

2)原因:自举电容(连接SW和BOOT引脚)容值不当或布局不良,导致上管驱动电压不足。自举电容充电不足(如占空比过高时)。自举电容自举电容的快速充放电会引入高频噪声,可能通过SW节点辐射或传导到其他电路。

3)解决方案:选择合适容值的自举电容(通常0.1μF~1μF)。确保自举电容靠近BOOT和SW引脚,布线短且宽(≥20mil)。串联电阻(如10Ω~100Ω)与自举电容形成RC滤波,阻尼高频振荡,减少振铃对驱动信号的干扰,可限制充电电流的峰值,降低瞬态冲击。

4.轻载效率低或跳频模式不稳定

1)问题现象:轻载时效率骤降或输出电压波动,输出纹波较大。

2)原因:芯片进入脉冲跳跃(Pulse Skipping)或突发模式(Burst Mode),导致纹波增大。

3)解决方案:检查芯片是否支持强制PWM模式。调整反馈环路补偿或增加一个小负载。输出端增加一颗容值稍大的电解电容,如220uf。

5.PCB布局不良导致噪声或EMI问题

1)问题现象:输出纹波大、反馈环路不稳定或EMI测试失败。

2)原因:功率回路(输入电容-开关管-电感-输出电容)面积过大。敏感信号(如FB反馈)靠近噪声源(SW节点或电感)。

3)解决方案:缩短功率回路路径,减小环路面积。FB走线尽量短,远离SW和电感。单点接地(AGND和PGND单点连接)。

6.输入电容选择与布局问题

1)问题现象:输入电压纹波大,导致芯片工作不稳定或损坏。

2)原因:输入电容容值不足或ESR过高。输入电容布局远离芯片Vin引脚,引入寄生电感。

3)解决方案:选择低ESR的陶瓷电容(如X5R/X7R),容值根据纹波要求计算。输入电容尽量靠近Vin和PGND引脚,间距<40mil。

2729

2729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?