1 新建工程文件

找到图标并双击打开

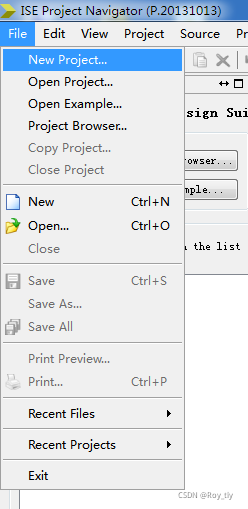

点击新建工程

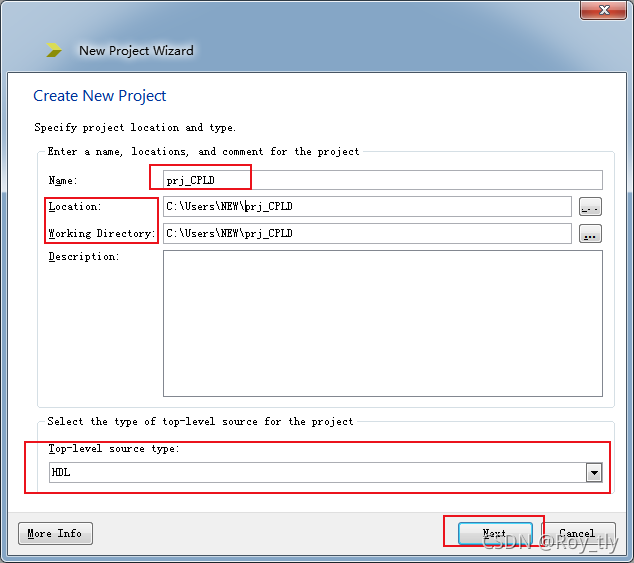

设置新建工程名及路径,并next

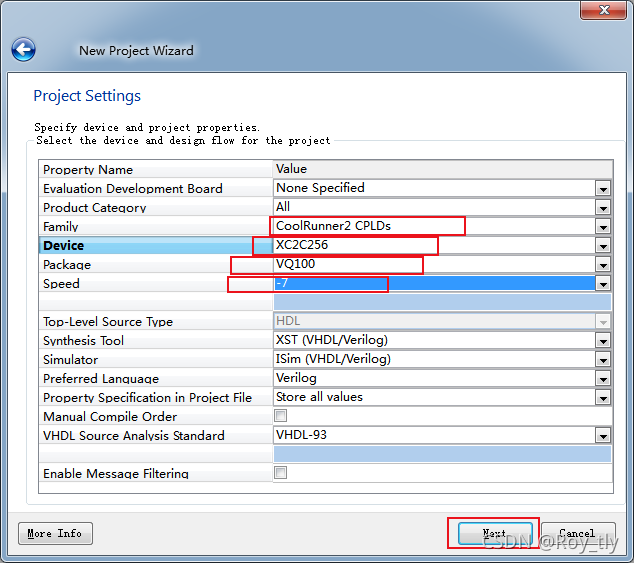

选择芯片型号,此处使用的是xilinx CPLD,型号为XC2C256-7VQ100,根据应用型号设置,并next

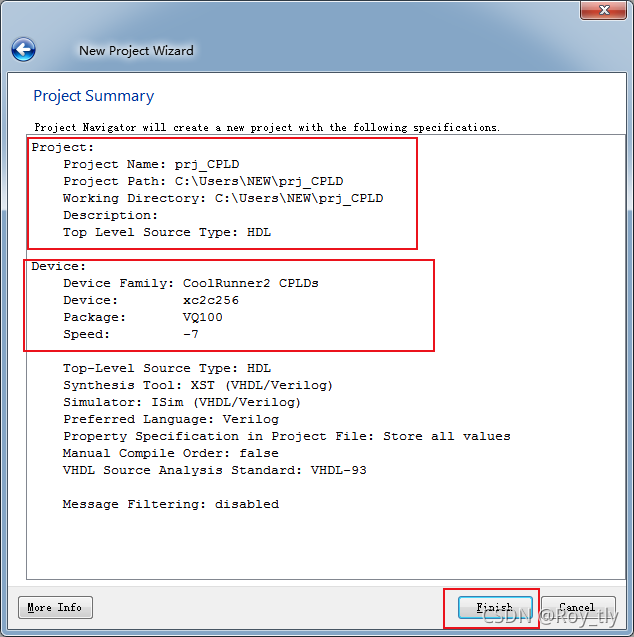

确认设置并Finish

以上步骤,工程建立完成。

2 新建/添加源程序文件

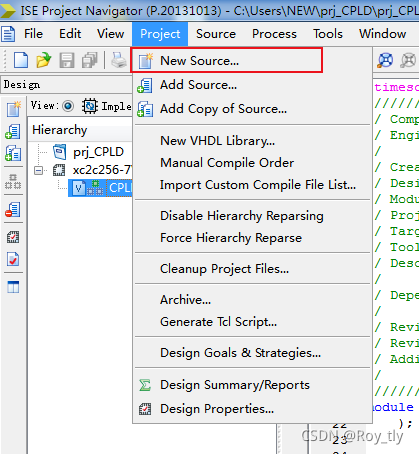

新建选择New Source...,此处选择新建

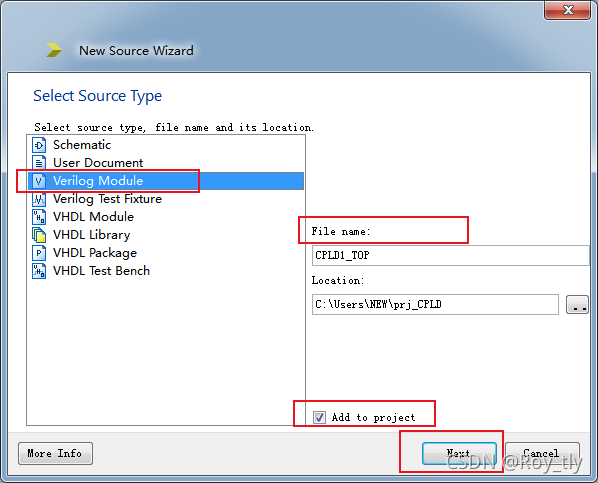

选择新建文件类型并命名文件,此处选择Verilog类型,完成后点击Next

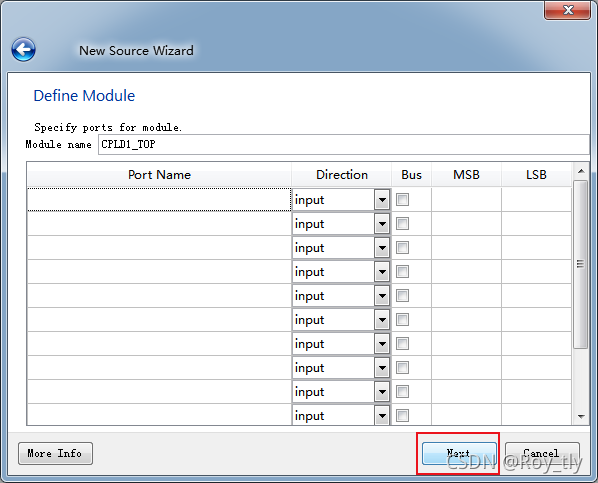

点击Next

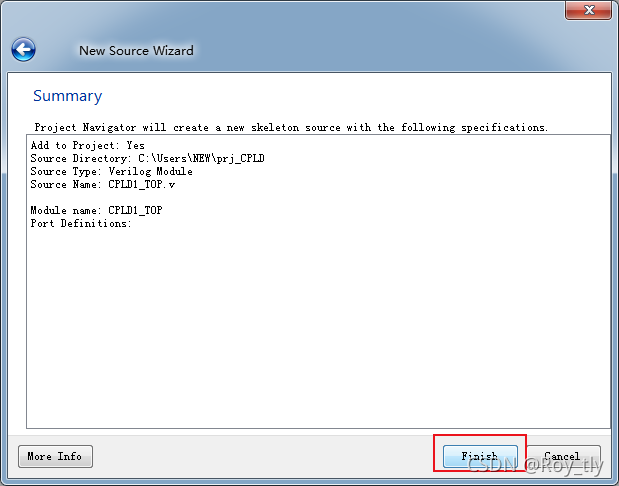

确认并点击Finish

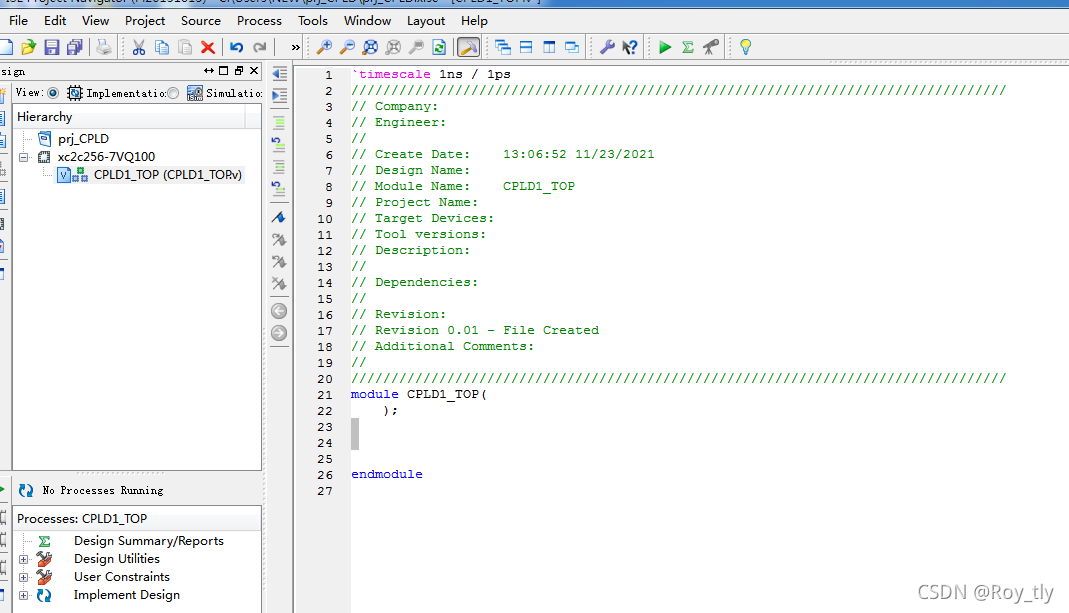

双击需要编辑的文件,并在右侧编辑框中完善驱动代码,并保存。

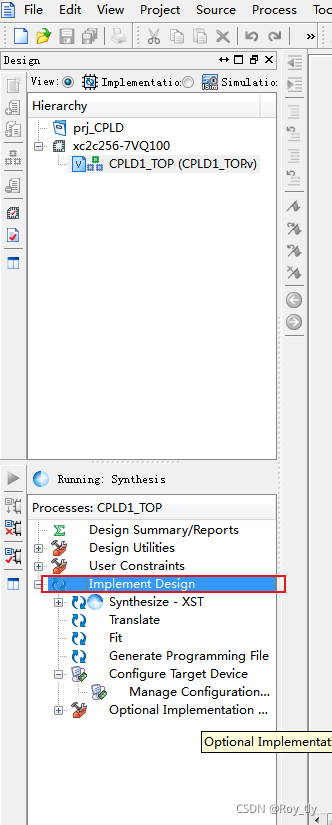

驱动源码编辑完成后,开始点击Implement编译

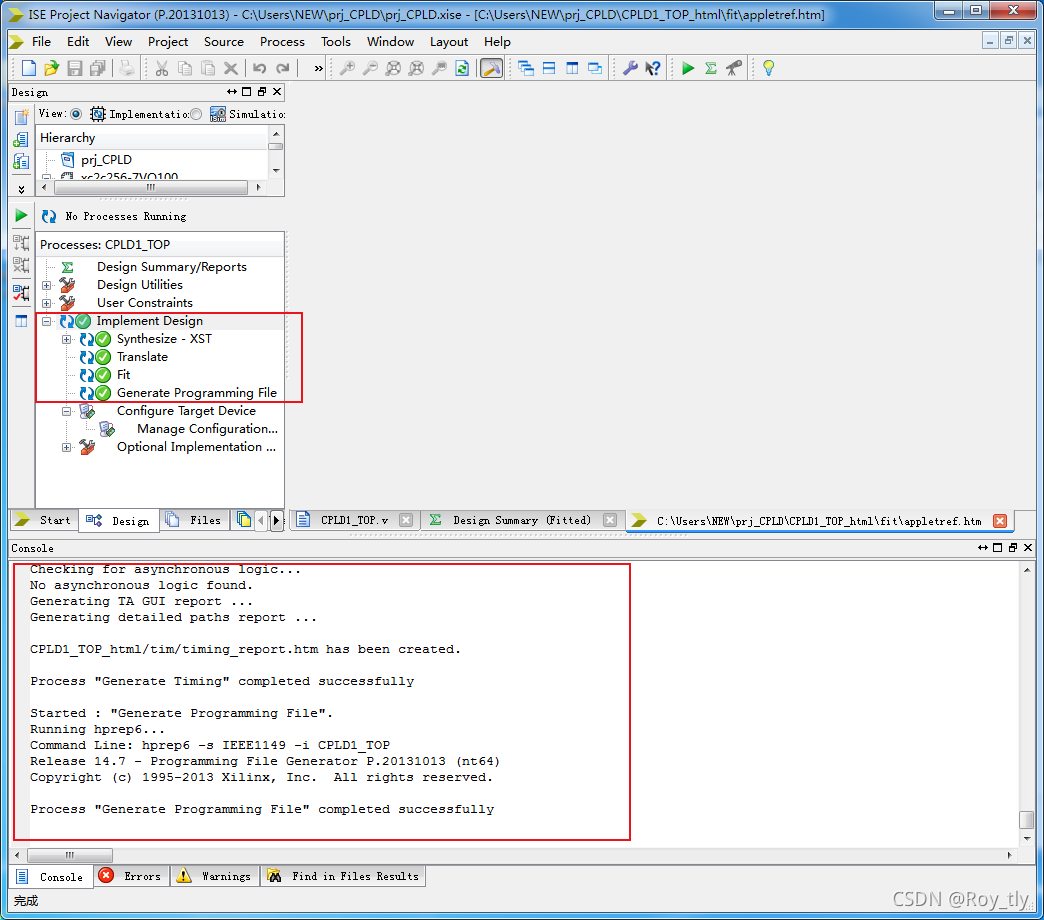

编译通过后界面如下所示绿色√,不通过会是红色的X;

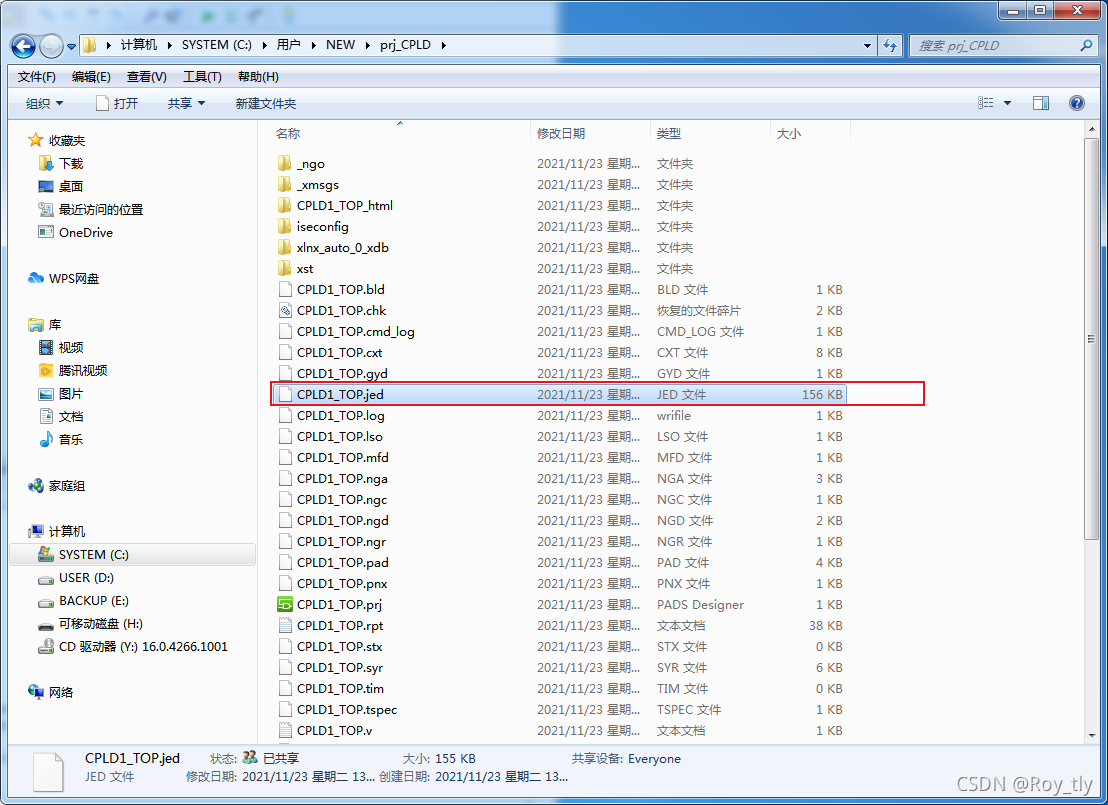

编译完成后,自动生成.jed文件。

以上,CPLD的操作完成,因CPLD自带存储,可将.jed文件直接烧录到CPLD中。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?