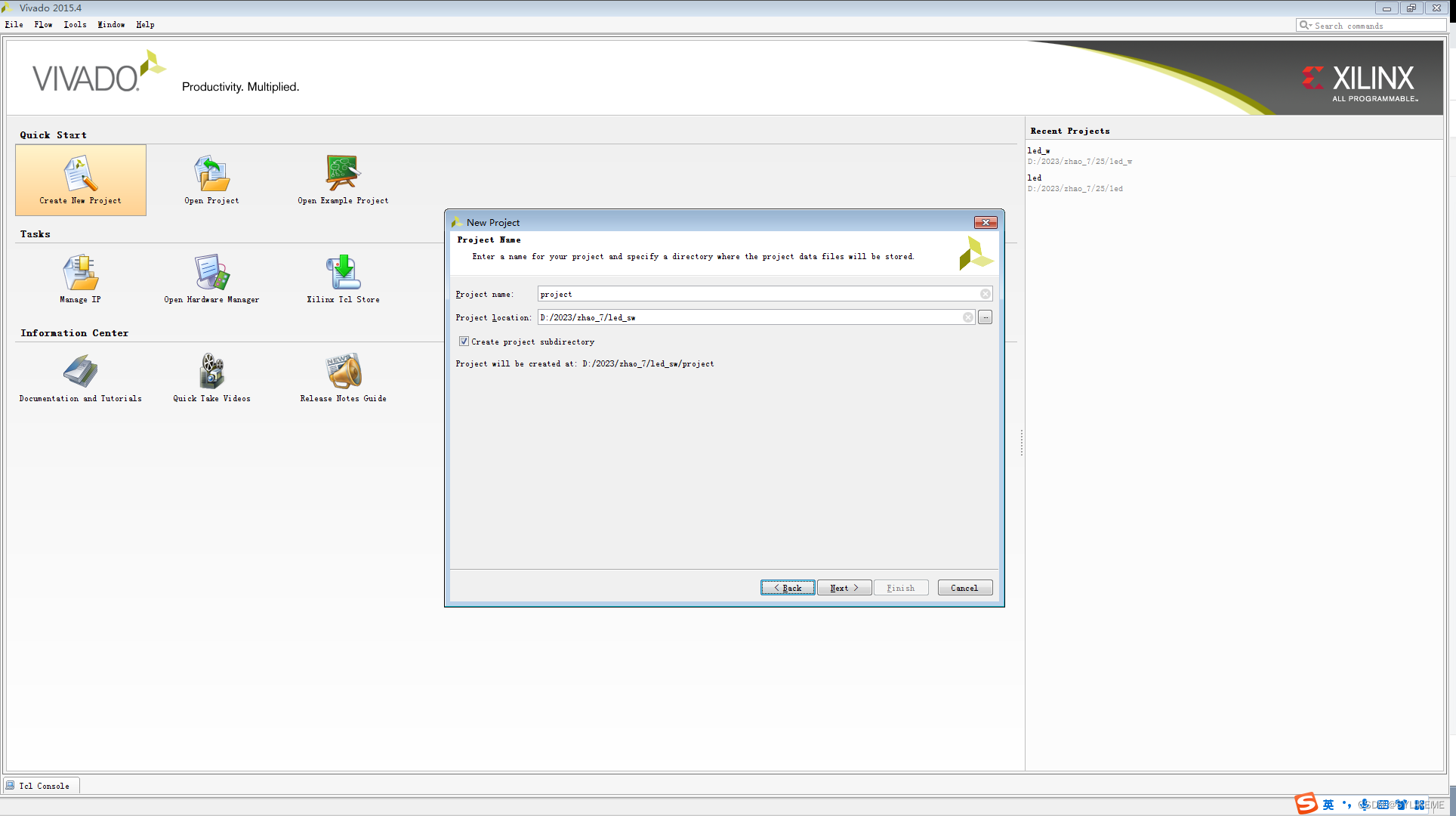

本次学习用的软件是VIVADO,版本2015.4.

同PL端开发一样,PS端同样需要创建工程。

所用的开发板是ZEDBORAD

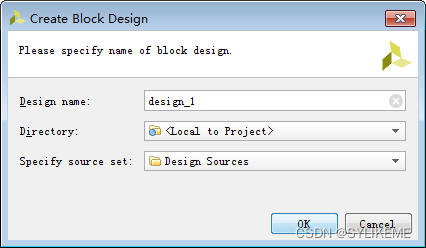

创建Block design。

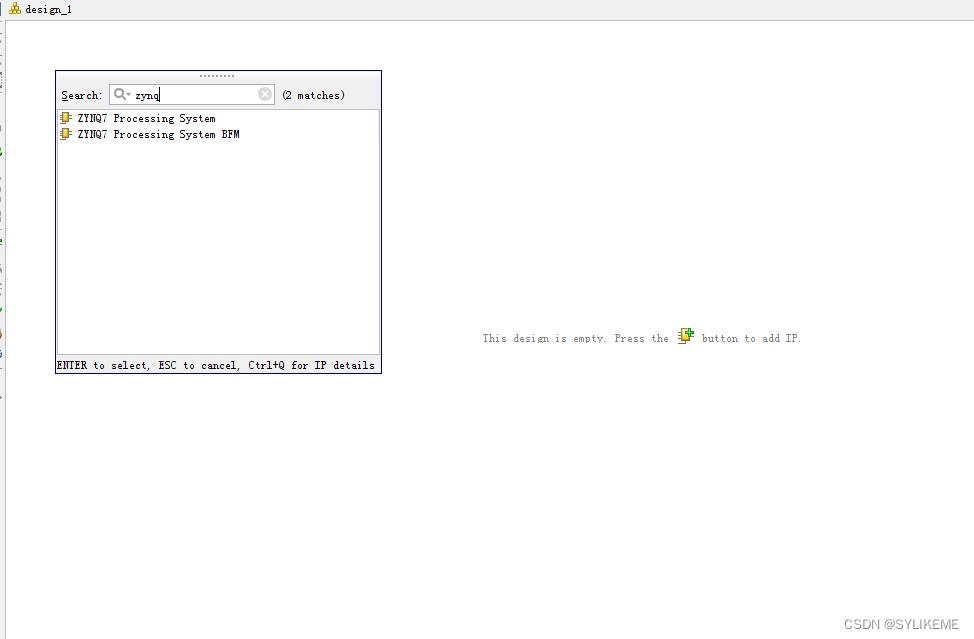

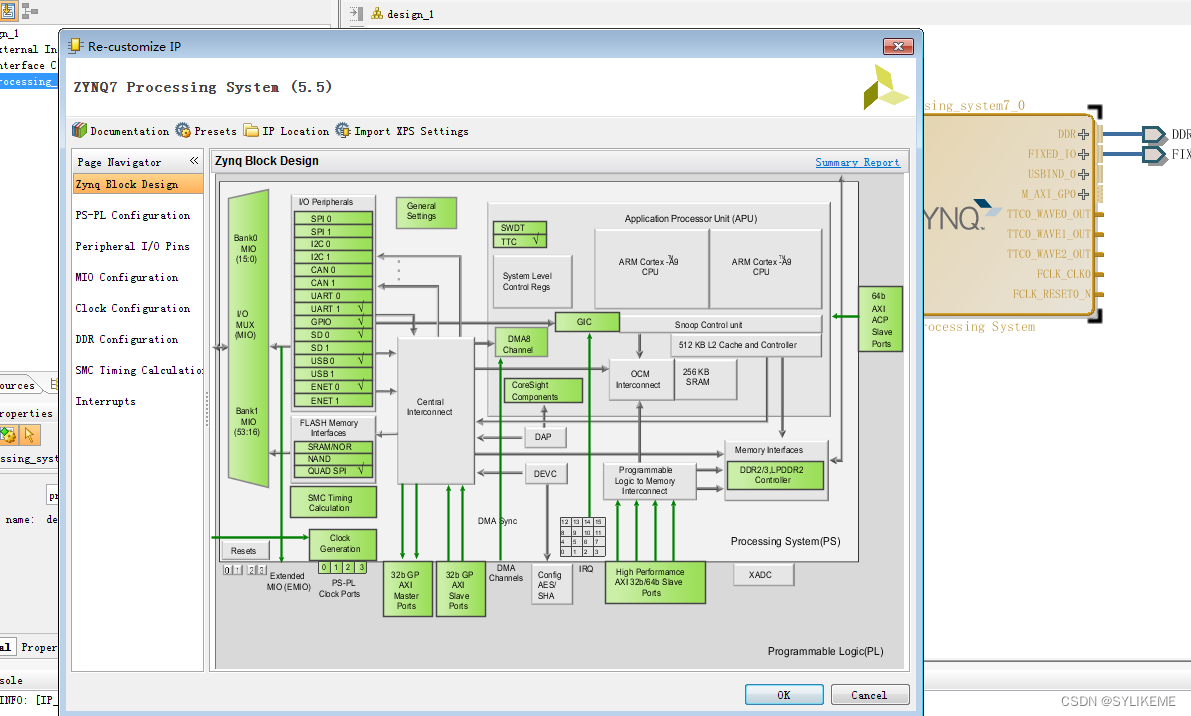

在Diagram中添加 ZYNQ7 Processing System。

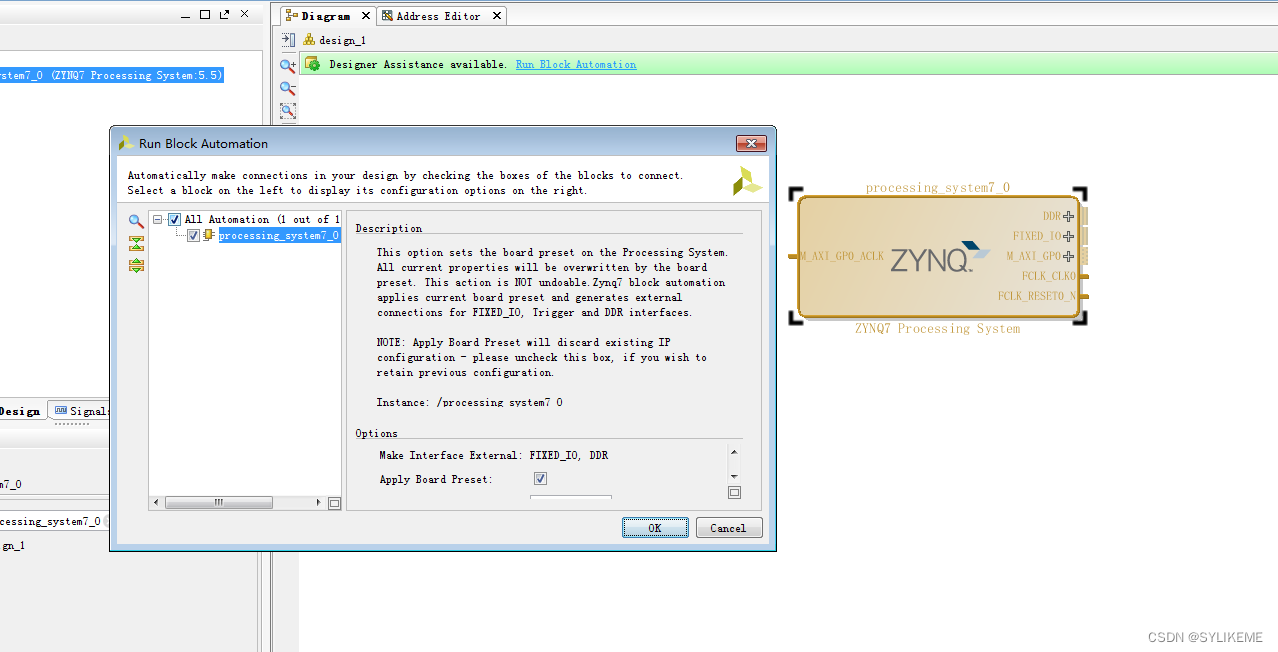

点击run block automation,根据Zedboard中所存有的配置来配置system。

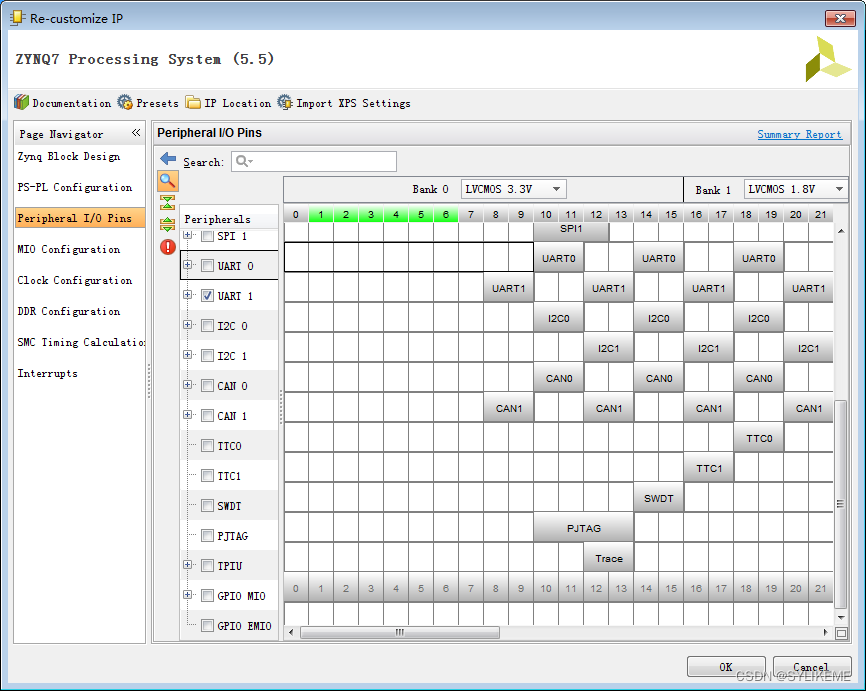

双击system来勾选我们需要的接口。

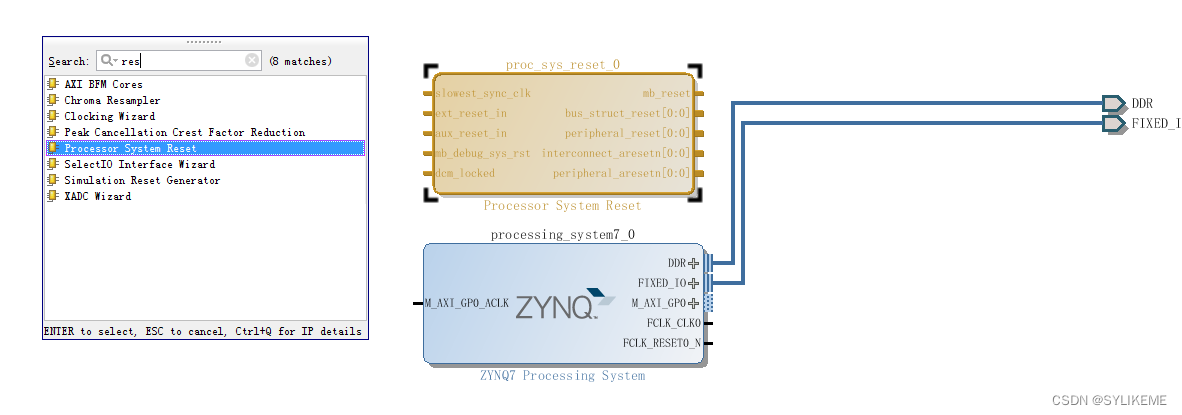

一般来说需要加上一个复位模块。

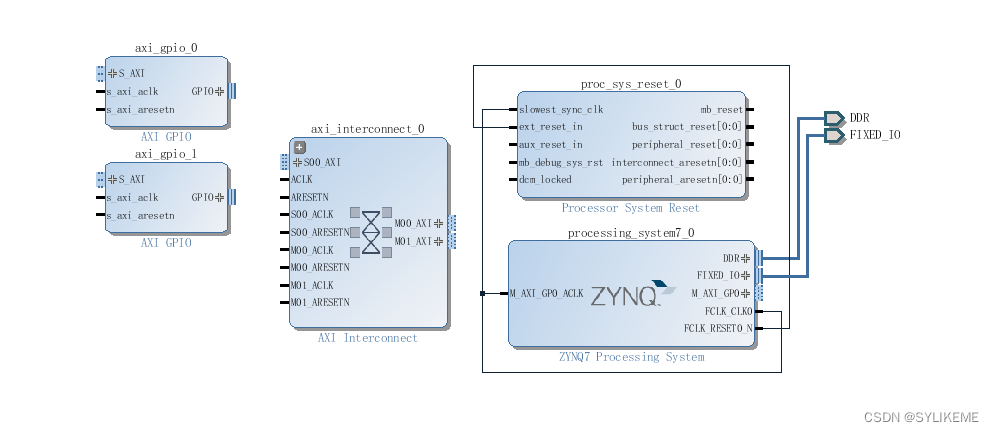

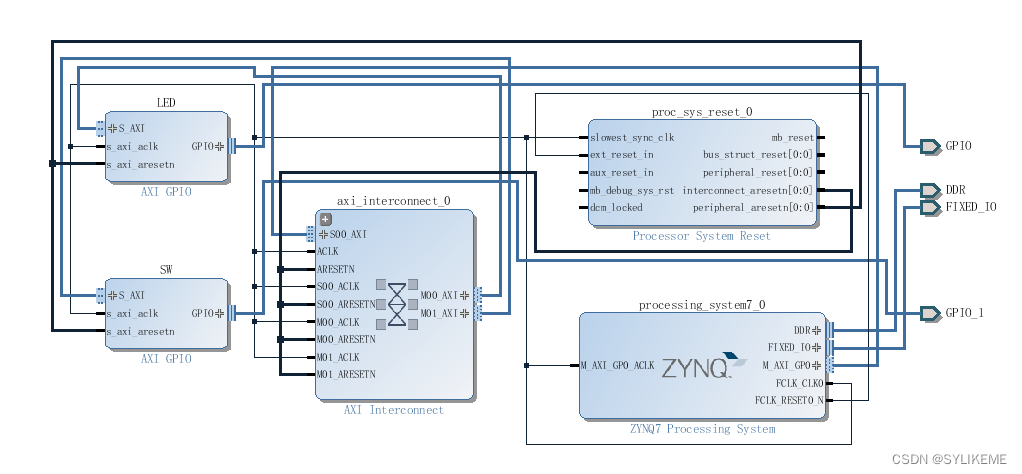

本次还需要一个AXI Interconnect和两个GPIO模块。

将模块进行连接。

将模块进行连接。

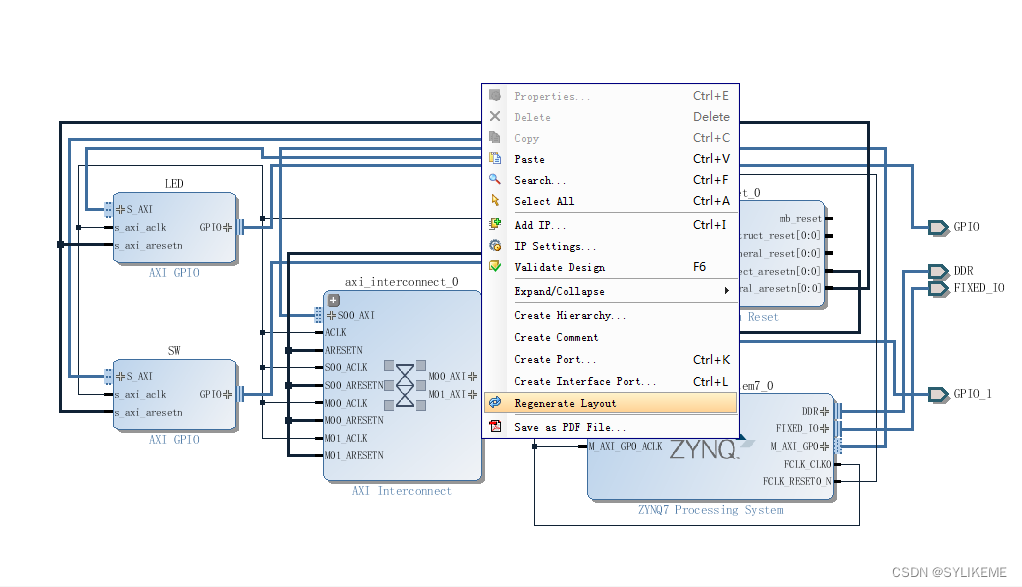

重新布局。

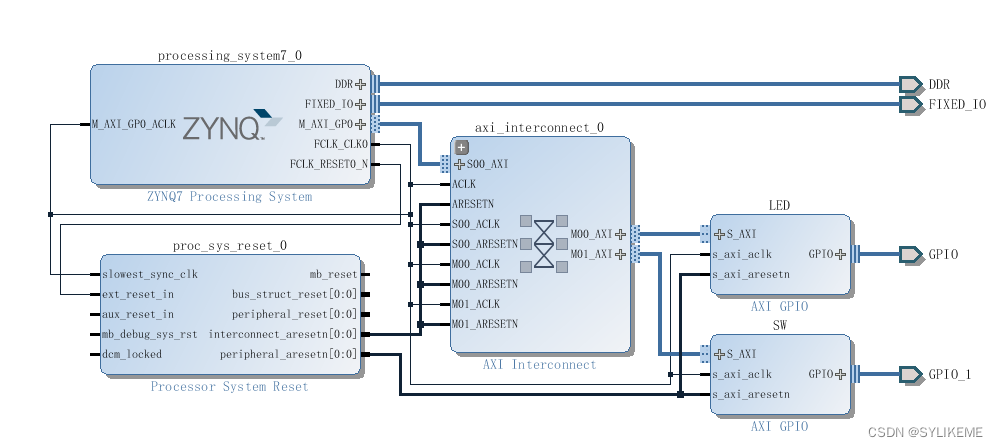

布局后。

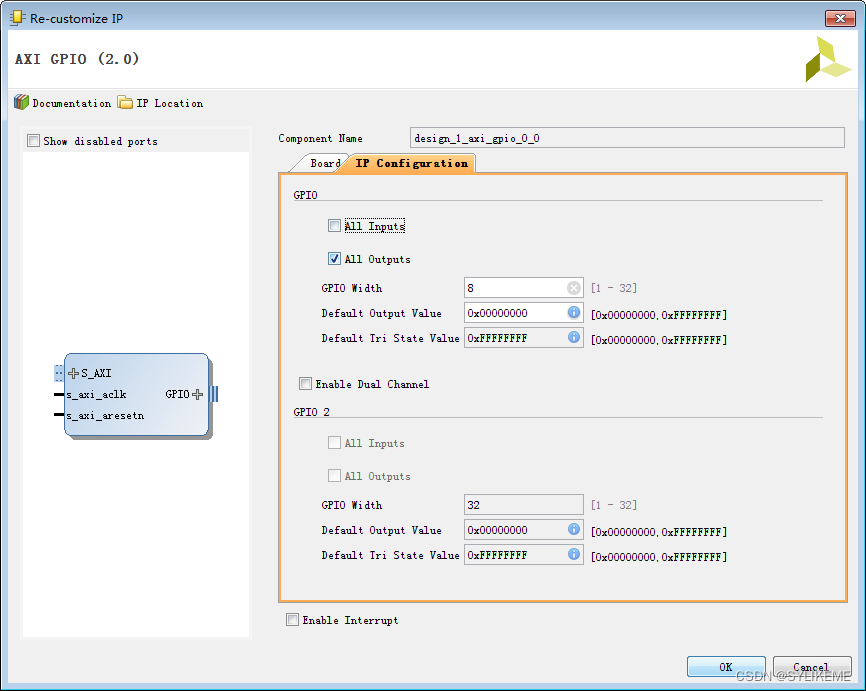

配置GPIO全为输出,宽度为8位。另外一个全为输入,宽度也是8位。

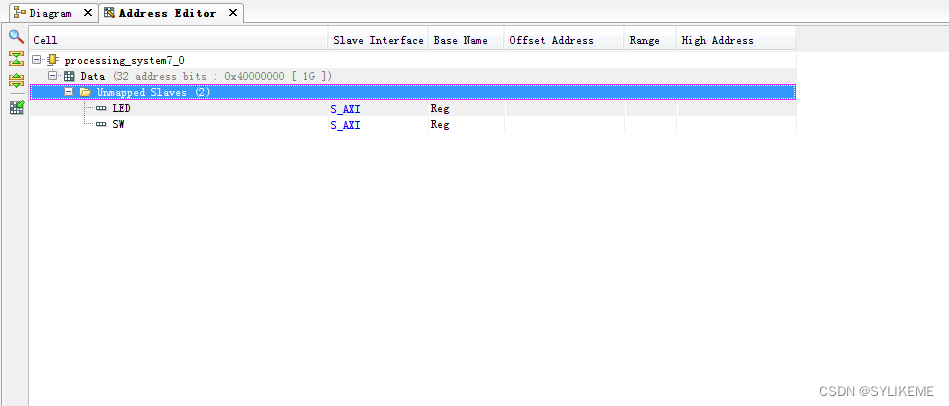

由于FPGA要控制外设是通过寄存器来控制的,而寄存器要映射FPGA的寻址地址。给没有映射的外设配置地址,之后保存。

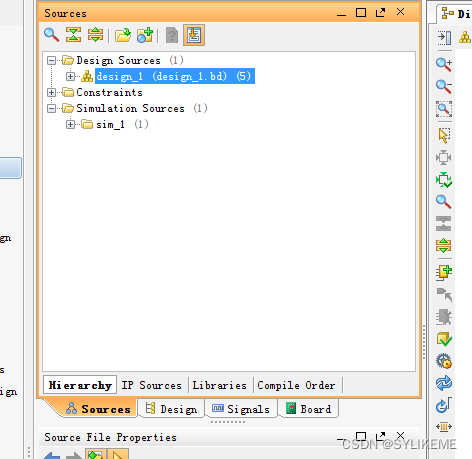

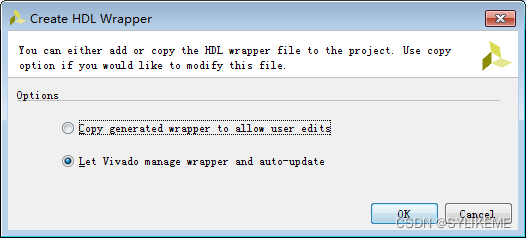

之后在sources中点击右键点击generate output products 和 create HDL wrapper。

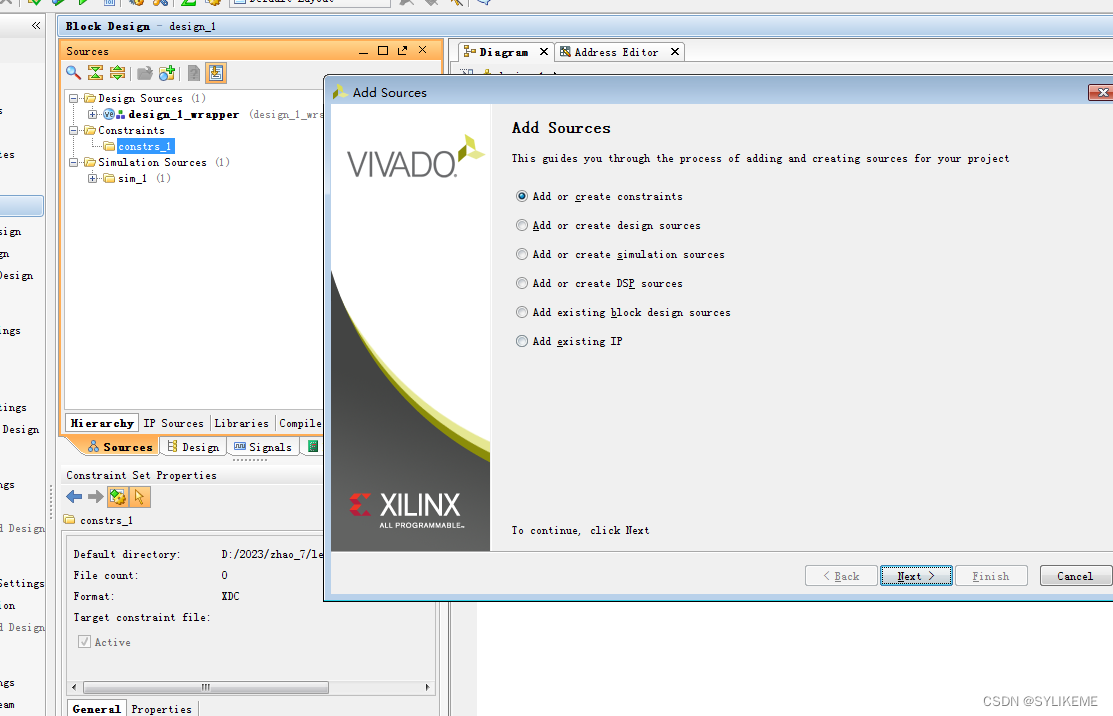

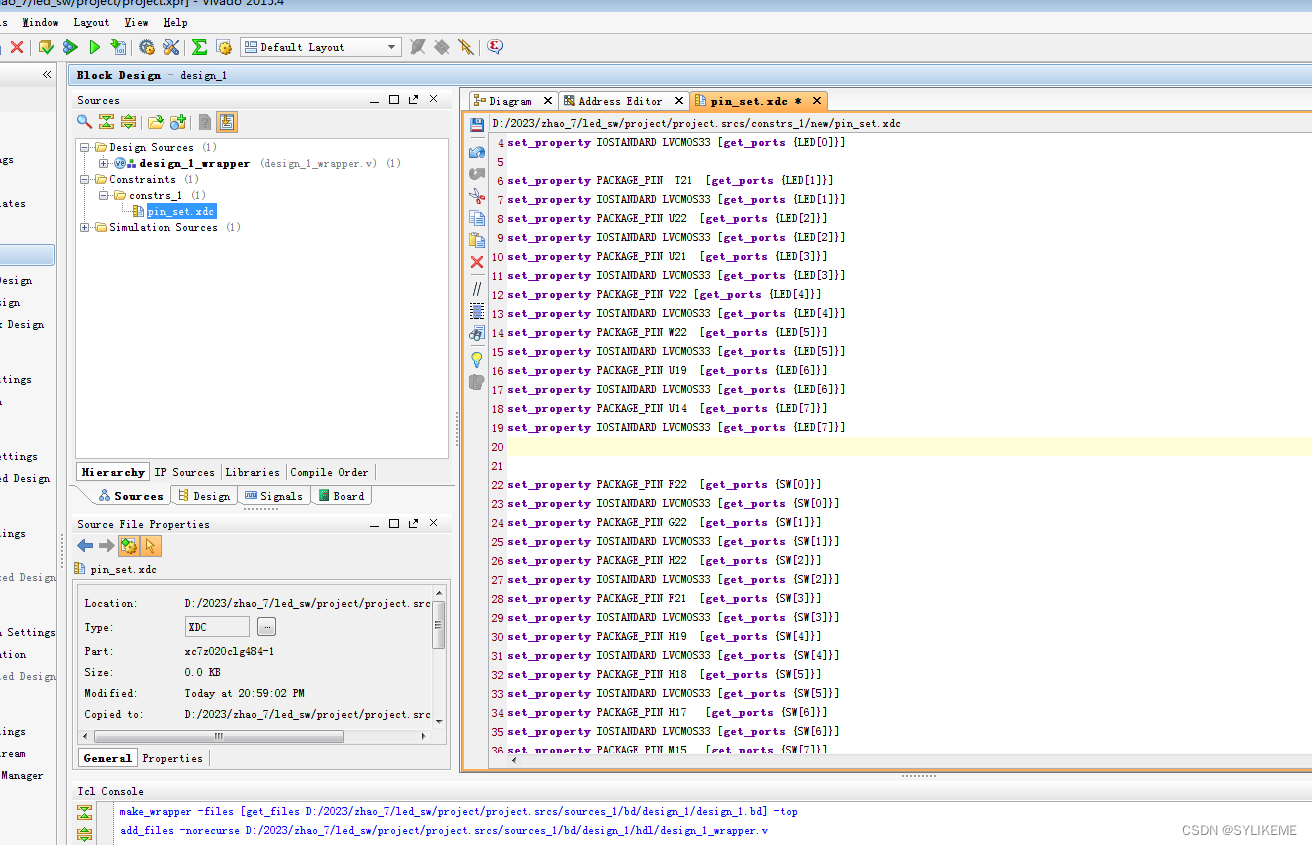

建立约束文件,绑定引脚。

编写约束文件,并保存。之后点击生成bit流。

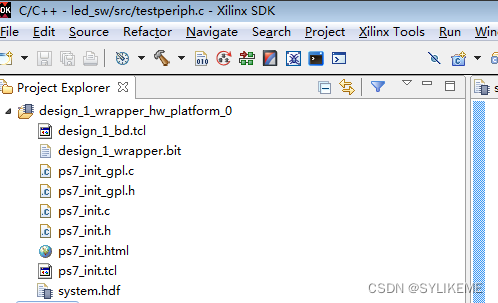

生成BIT流文件之后,先点击file>export>export hardware 之后launch SDK。

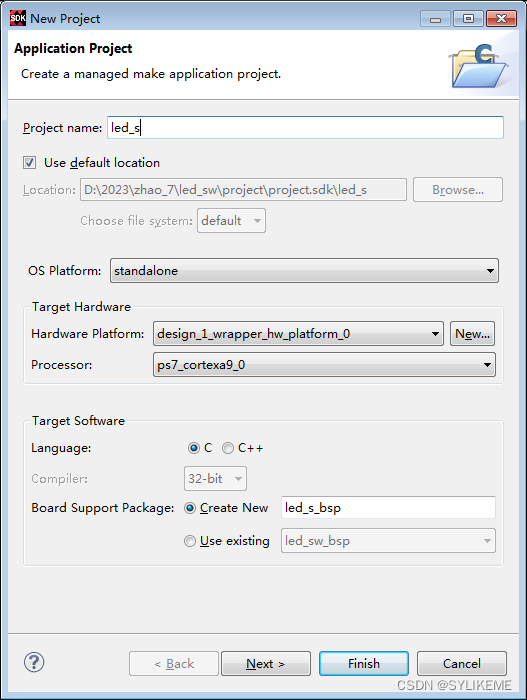

点击File>NEW>Application file

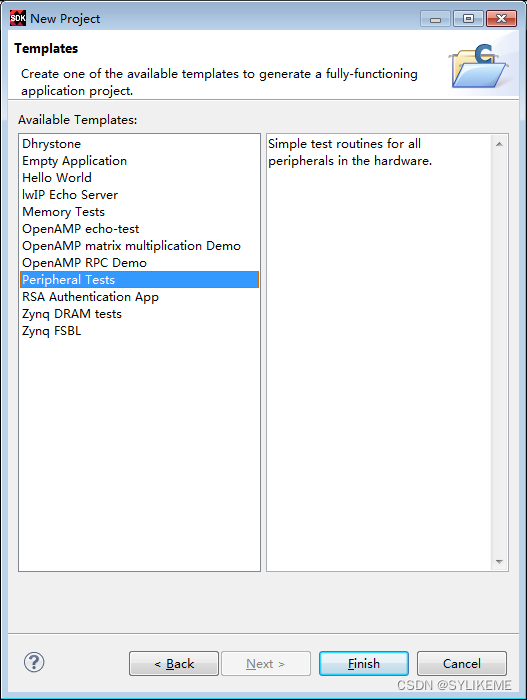

点击Next,选择Peripheral Tests。

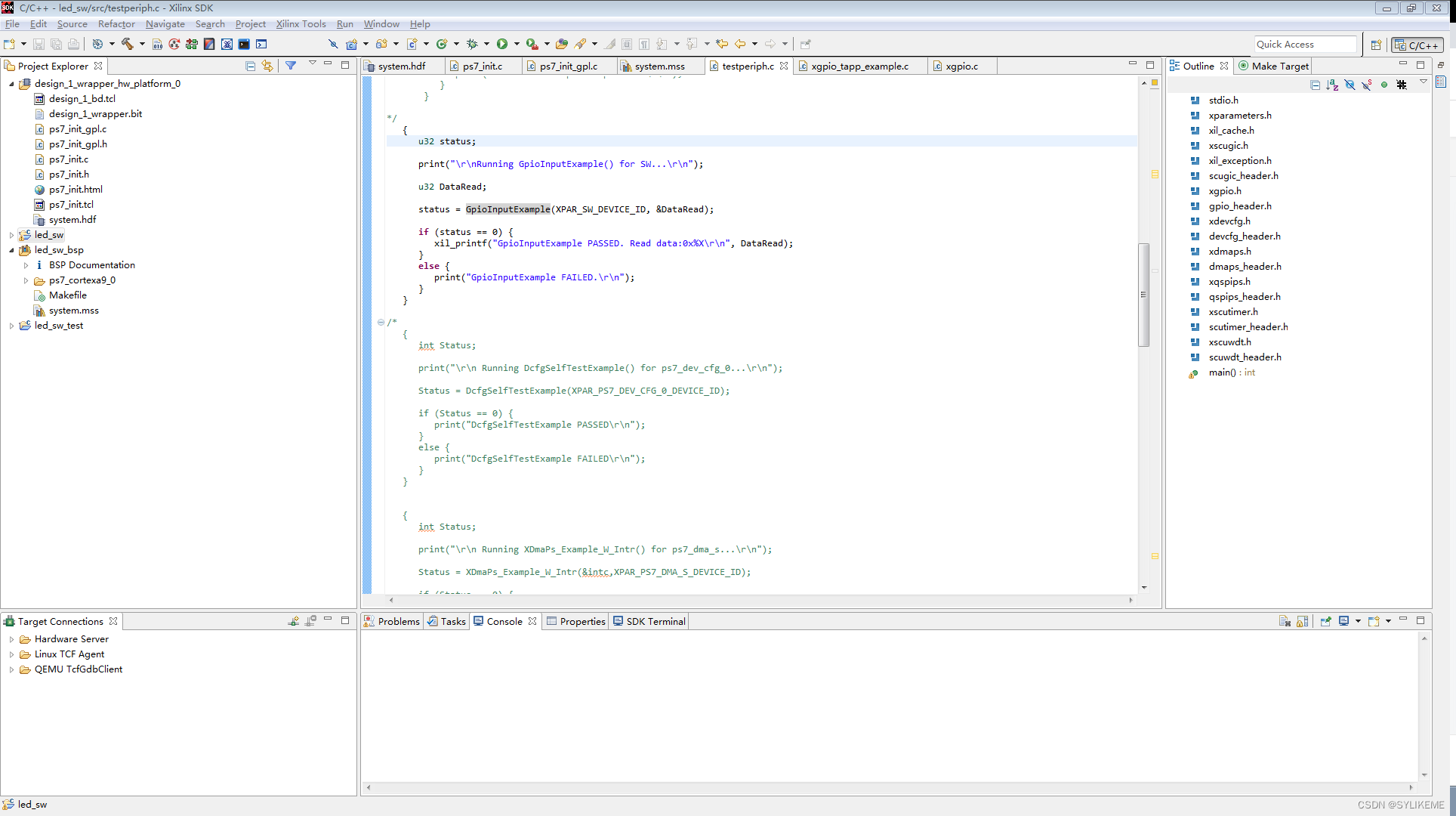

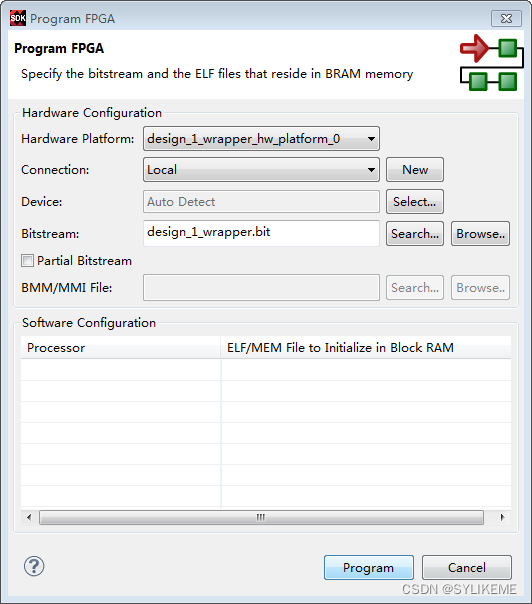

在所建立的app 文件中编辑程序。之后点击Xilinx Tools > program FPGA 进行烧写程序。

在所建立的app 文件中编辑程序。之后点击Xilinx Tools > program FPGA 进行烧写程序。

之后点击Run > Run as >Launch on hardware。板子即可运行程序。

8156

8156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?