前言

折腾了下System Generator里头的黑盒(black box),该模块就能实现将硬件语言描述的设计导入到System Generator中进行使用,今天也是对该模块实现将HDL描述导入模型文件,然后用于数字信号处理的实现,其次对模块做好配置,使其可以通过仿真验证。

设计

打开软件和新建空白模型这些就不再多述了,直接上今天的主题,在模型文件中放置Black Box,路径是:Xilinx Blockset/Index/Black Box,然后在弹出的窗口选择需要链接到黑盒的HDL文件,我这边为让步骤简单些,就直接使用Xilinx官网提供的一个滤波器的文件(transpose_fir.vhd)进行设计,注意:这些文件都要放在一个路径下

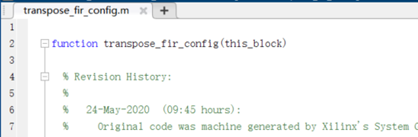

然后会自动加载一个.m(transpose_fir_config.m)的代码,并在MATLAB中打开。

需要对里面的配置做下更改

dout_port.setType(‘UFix_26_0’);中的UFix_26_0改为Fix_26_12,代表有符号的定点数,26bit的位宽,二进制点在最左侧的位置,改好后如下:

在65行的即 this_block.addFile(‘transpose_fir.vhd’)的上方添加:this_block.addFile(‘mac.vhd’),使得可以加载滤波系数,改好后做保存,即可关闭此文件。

双击Block Box模块,打开配置界面;

Block configuration m-function就是配置所需的m函数,也就是刚刚自动生成的一个,也可以换成自己创建的。

Simulation mode:就是选择仿真模式,总共有三种;

Inactive:使用这种模式的话,会忽略黑盒的输入,直接生成零;当黑盒有单独的仿真模型可用,并且模型使用模拟多路复用器与黑盒并联时,通常使用此设置。

Vivado Simulator:该模式下,使用与黑盒关联的 HDL 上的协同仿真生成黑盒的仿真结果。

External co-simulator:使用该模式,需要向设计添加 ModelSim HDL 协同仿真模块,并在 HDL 共同模拟器中指定 ModelSim 模块的名称以使用字段。在此模式下,使用

HDL 协同仿真。

选择Inactive,看看该种模式下的效果,点击OK关闭。

不过在使用前,还需要添加测试模块所需的其他模块:

具体配置可获取本次设计的文件进行学习,模块的配置参考ug958

对设计做下简单说明:输入两个正弦信号叠加的信号再和一个30M的正弦混频所得的信号,然后再通过黑盒所加载的HDL文件,然后经过下采样再示波器做显示。

Step就是做提供一个复位信号,初始为0,之后一段时间都保持为1。

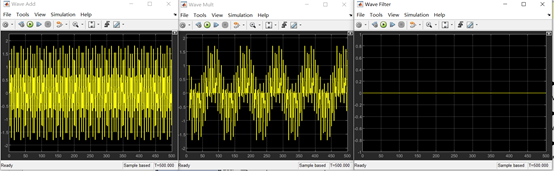

然后将Stop Time设置稍微大一点,本设计设置了500,然后点Run,观察示波器显示:

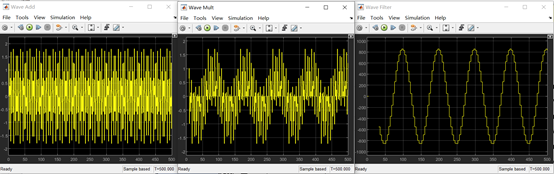

左边的是叠加后的信号,中间的是混频后的信号,最右边的就是经过黑盒后的信号,可以看到这时候的值一直保持为0,然后将黑盒配置的仿真模式再改为Vivado simulator,继续运行,这时的结果如下:

前两个代表的输入信号未变,经过黑盒输出的信号可以明显看到此时不再是零,而是是混频的信号的包络,也是黑盒所加载的滤波器的滤波效果。

设计文件已传至网盘

2403

2403

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?