前言

上一篇将创建的设计模块分成了三个时钟层次的子系统,此时子系统之间的数据由于时钟未同步,导致数据在传播时,采样所得的数据会有错误,因此需要建立一个异步通道,使得各时钟通道之间的数据可以准确的被传输。

建立异步通道

该设计将使用FIFO进行,FIFO(First-In-First-Out)也就是指FIFOs中的数据是先进先出的,控制信号可以确保仅在当前数据有效时才可被读取,并且仅当有可用空间时才写入。如果FIFO是空的或者满的,控制信号会让其停止运行,不过此次的设计不需要考虑FIFO会写满,输入是始终可以写入的。

在设计中会有两个需要用到FIFO的数据路径,包括:

- 从Ctrl到Gain Control的数据

- 从DDC到Gain Control的数据

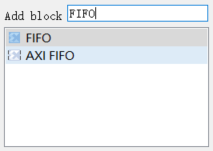

开始添加FIFO到设计中,除了以前讲到的添加方法外,还可以如下进行添加:

1、在设计文件中任意空白的地方右击,然后选中Xilinx BlockAdd

2、在对话框中输入FIFO

3、从出现的菜单中选中FIFO,然后双击添加到设计中

将Ctrl和DDC的输出数据接入FIFO模块,接法如下:

此时就已经将不同时钟域的数据链接完成,接下来就是连接控制信号,以实现数据的安全传输,Ctrl需要提供一个FIFO的写入使能信号,DDC也是如此,Gain Control则需要分别对两个FIFO有个读取数据的使能信号;

首先Ctrl模块,在当前的设计中,是无所需的信号线,因此还需要加以创建,双击该模块,进入其内部,按添加FIFO的方式再添加两个模块:Delay和Relational,并且双击Relational进行属性编辑,将Comparison改为a!=b,再点OK;

改完之后复制一个Out在本界面,再将各模块之间连接起来:

其中Relational的作用就是当输入改变时,会激活一个时钟周期的输出用以顶层FIFO的写入使能,该部分设计好后,返回顶层,并双击Gain Control打开该子模块,并且与上述相同的进行添加一些模块:Inverter(2个)以及Delay,复制一个In和两个Out的端口在本界面,并做更名然后连接各部分:

这部分的将来自顶层的FIFO的empty信号作为反向,若数据不是空的,该变量的值是0,做反向为1,可用作Ctrl数据的读取使能信号,相同的,来自FIFO1的empty信号也可以用作DDC数据的读取使能信号,相同的信号都是通过In2输入,但是由于FIFO的数据输出和empty信号会有一个延迟,因此需要加一个延迟使得数据和读取信号对齐。

返回顶层将各模块之间的控制信号连接起来,然后再Run,不过在运行前有个错误需要更改下,上一篇将System Generator那个生成器也不小心弄到了DDC模块里,需要剪切到顶层,不然无法运行……:

运行后会发现,结果和上一篇的运行结果相同:

这一步的操作也到此结束,在下一篇文章中将学习如何将不同的时钟域与每个层次结构关联,敬请期待~

本次设计所用文件

链接

提取码:if4n

567

567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?