目录

原文地址高速外设互连接口(Peripheral Component Interconnect express, PCIe)

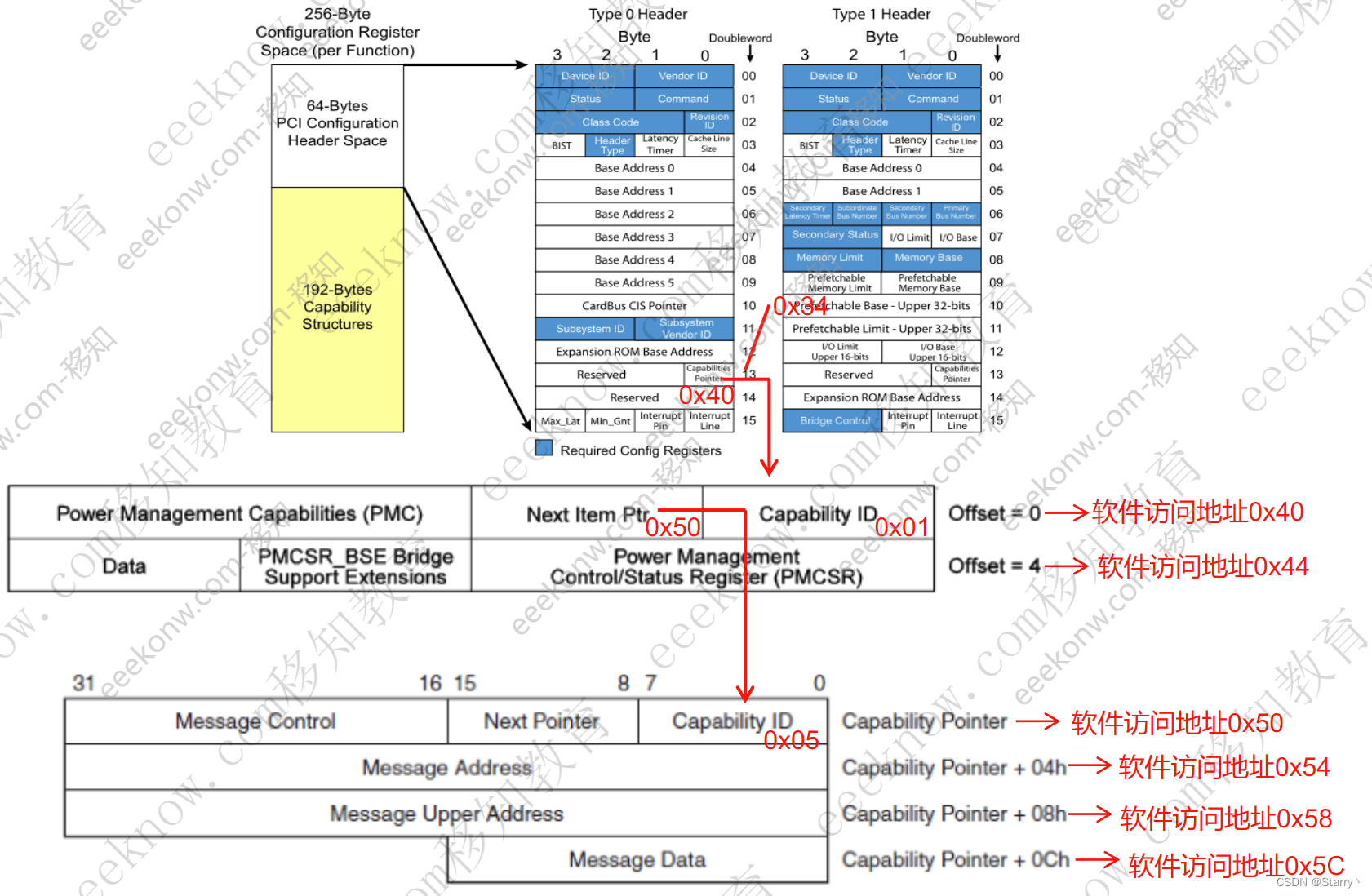

Capbility空间内容可选择实现,以下寄存器必须实现:

- PCI Express Capabiltiy

- Power Mangement.

- MSI/MSIX中断

Capbility空间采用链表结构,每个能力寄存器存储着下一个能力寄存器的地址,第一个能力寄存器的地址为Header Space的0x34 Capbility Pointer。

系统软件从头空间的Capbility Pointer寄存器开始,按着链表遍历,不断判断Capbility ID直到找到所需的寄存器。例

如下图

1. 18 Device Control Register

1.1. Max Payload Size(MPS)

MPS表示一个TLP中数据负载的最大长度。显然一定不会超过TLP中Length[9:0]字段表示的4KB。

实际使用

订阅专栏 解锁全文

订阅专栏 解锁全文

268

268

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?