1️⃣什么是START BYTE?

START BYTE会将开始条件的过程延长,就是在I2C生成START 条件之后,继续发送1个byte字节信号(0000_0001),master持续的将SDA线拉低7个周期。

2️⃣为什么需要START BYTE?

I2C总线上至少要有一个master(微控制器或者DSP)连接,如果微控制器具有片上硬件I2C总线接口,那它可以被编程为只能被总线的请求中断。当微控制没有这样的接口时,它必须不断地通过软件来监控总线,不断地轮询或监视总线的行为,这势必影响了数据传送的安全性,也增加了功耗。在这种情况下,如果采取正常情况下的start条件(在SCL为高期间,SDA由高拉低),这个过程相对是很短暂的,微控制器可能监视不到这个start条件。所以,在数据传输之前,为了确保微控制器可以采样到总线上的START条件,可以使用一个比正常情况长得多的start过程(发送0000_0001),以此便于微控制器以较低的频率采样SDA线。当微控制器检测到起始字节中的七个0中的任意一个0时,就可以切换到更快的速率,找到0000_0001之后的重复启动(Sr)条件,然后开始之后的传输。

3️⃣怎么开启START BYTE?

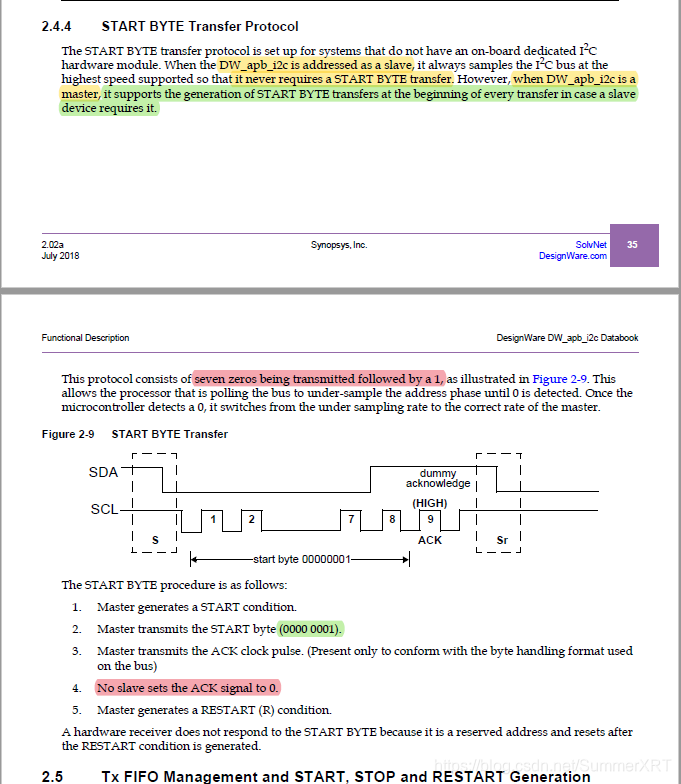

START BYTE的过程:

- maser先产生一个START条件;

- maser发送start byte(0000_0001) ;

- start byte字节传输之后的一拍,不能有任何slave响应ACK;

- master产生一个restart条件。

以下是I2C协议中的描述:

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?